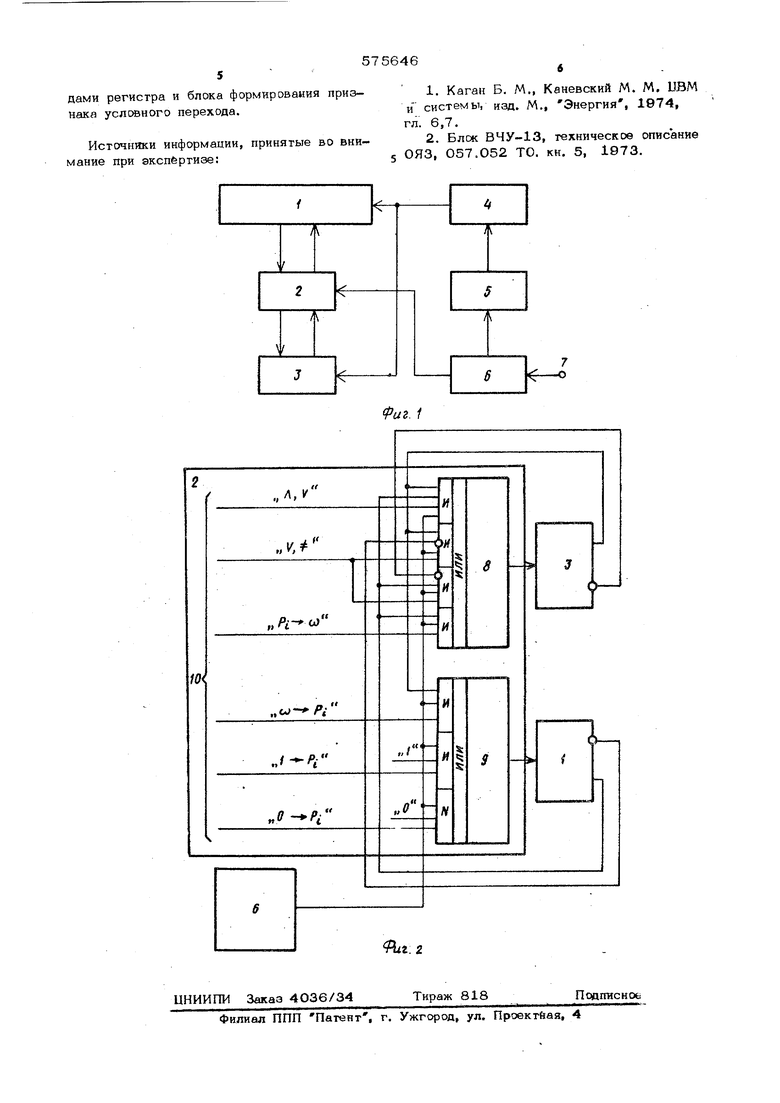

4атор 4, блок умнс кеняя 5 преобразова1-вль константы в унитарный код 6 и входную шину 7.о Блок выполнения битовых операций содермшт узел; 8, реализующий выполнение битовых операций конъюкциИб дизъюнкции, сложения по модулю /два, посыгаси го разряда регистра 1 в блок 3, увзл 9, реализую щий выполнение посылки единицы, нуля) или признака условного перехода в i -Д разряд регистра 1, шийы 10 управляющих сигналов ( V -значение i -го разряда регистра 1, О) -признак условного перехода, вырабатываемый блоком 3, Л -конъюкции, V -дизъюнкция, ijL -сложение по модулю даа. Устройство работает следующим образом. Результат операций из сумматора 4 запи сывается в регистр .1. и в. блок формирования признака условного перехода 3 в соогветс ВИИ с правилом выполнения .операции. Опэрации умножения и сдвига выполняются Е бл ке умножения 5, Результаты умножения и сдвига через сумматор 4 записывае-гся в регистр 1, Операция сдвига сааменяе1х;я умножением на унитарный двоичный код, форк;ирувмы8 преобразователем 6, который вырабатывает этот код в зависимости ; от -юнстанты, записанно14 в адресной части команды сдвига и поступающей в преобра- , еователь 6 по шине 7. Унитарный код выдается в блок умножения в качестве множимого. Этот же код используется при выпол нении битовых операций, Битовые оперйции выполняются в блсже 2 над значением разряда регистра 1 и признаком условного перехода, а результат операции ваписываегся в разряд регистра 1 -или блок формирования признака условного перехода 3 в зависимости от кода битовой операции. Блок выполнения битовых операшш представляет собой комбинационную схему,.в которой в соответствии, с алгоритмом происхо дит операция над разрядом, номер которого г указывается в команде.. Преобразс атель б по значению номера разряда, указанного в адресной части команды, поступающей с шины 7, вырабатывает унитарный двончньй код, мес/о-положение единицы, в котором определяется кодом номера разряда., единица является операт.ором, который управляет & яолнением одной из битовых операций, так как при после яовательном способе пвр€здача информшии АУ на BXQQe блока 2 в срабатывания преобраасжателя 6 оказывается 4 -и разряд ),егвсгра 1 при вьтсшиевии кокъюш ции, дизьюнкпии и сложения по модулю два над р. в признаком условного перехода oS , либо посыпки Рд в блок д) . При этом Б зависимости от управляющего сигнала срабатывает одна из схем И узла 8, и результат записывается в блок формирования признака условного перехода 3. При выполнении операций посылки единицы, нуля или tO в « -и разряд регистра 1 срабатывает один из элементов И узла 9, и осуществляется соответствующая запись в регистр 1 на место -го разряда, так как сигнал в преобразователе 6 возникает в момент регенерации -го разряда в регистре. При выполнении битовой операции, наприер засылки значения шестого разряда регистра 1 в блок 3 преобразователь 6 по коду номера разряда вырабатывает сигнал в момент шестого такта и открывает элемент И узла 8, на вход которого поступает в этот момент значение шестого разряда регистра. Результат операции записывается в блок 3. Таким образом, момент времени выполнения битовой операции зависит от сигнала с преобразователя 6 и лежит в пределах цикла выполнения операции, длительность которого равна п , где ц -разрядность АУ, f - длительность одного такта. Затраты оборудования на выполнение би- . товых операций в предлагаемой схеме умен шается на Х0% за счет исключения дешифратора номера разряда. При исключении дешифратора номера разряда оборудование АУ, участвующее в выполнении; битовых операций и построенное на микросхемах 112 серии, составляет примерно 20 элементов. Формула изобретения Арифметическое устройство последователь- ного действия, содержащее регистр, сумматор, блок умножения, блок формирования признака условного перехода, преобразователь константы в унитарный код, причем вход преобразо вателя жонстанты в унитарный код соединен с входной шиной устройства, а первый выход с входом блока умножения, .выход которого соединен с входом сум;матора, выход которого соединен с входами р§гистра и блока форми- рсжания признака условного перехода, отличающееся тем, что, с целью упрощения устройства, в него введен блок выполнения битовых операций, причем второй выход преобразователя константы в унитар-f ШУИ код соединен с первым входом блока выполнения битовых операций, второй и третий. входы которого соединены соответственно с вьшопами регистре® и блжа формирования призншса условного перехода а первый и агорой выходы блока выполнения битовых операций соединены соответственно со

дами регистра и блока формирования признака услсжного перехода.

Источники информации, принятые во внимание при экспертизе:

1,Каган Б. М., Каневский М. М. UBM и системы, изд. М., Энергия, 1974, гл. 6,7.

2.Блок ВЧУ-13, техническое описание 5 ОЯЗ, 057.052 ТО. кн, 5, 1G73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1974 |

|

SU578642A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Устройство коррекции | 1987 |

|

SU1499507A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

Авторы

Даты

1977-10-05—Публикация

1974-10-08—Подача