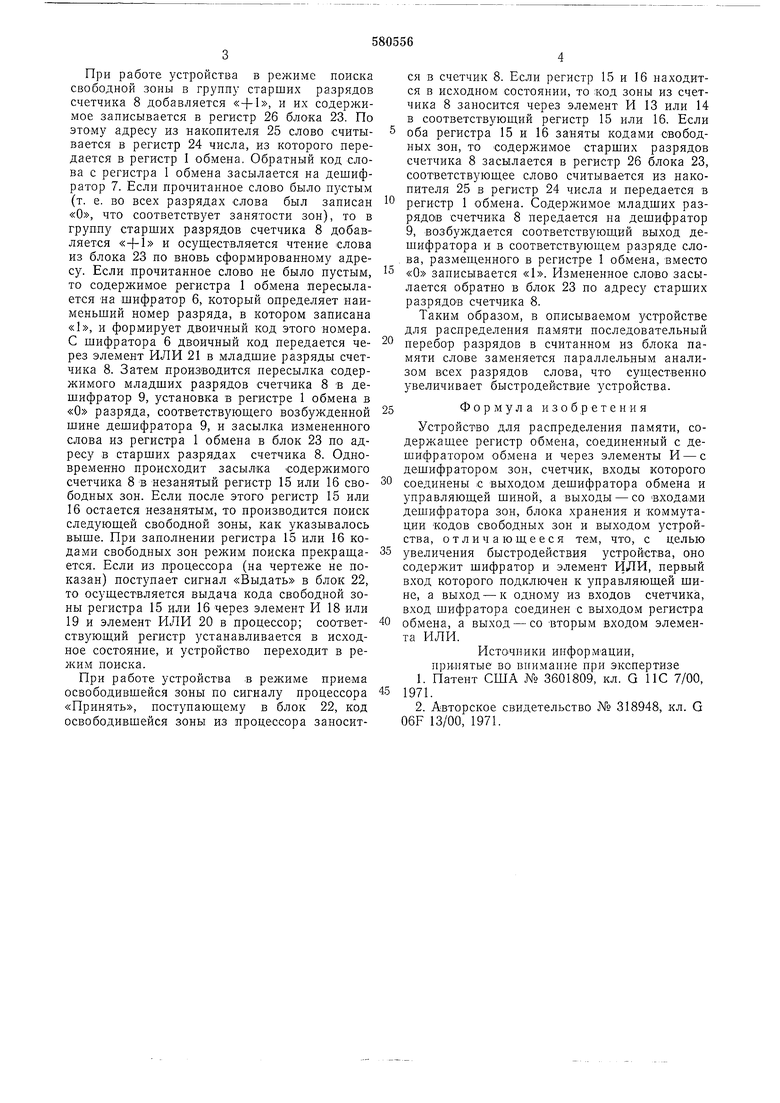

При работе устройства в режиме поиска свободной зоны в группу старших разрядов счетчика 8 добавляется «-)-1, и их содержимое записывается в регистр 26 блока 23. По этому адресу из накопителя 25 слово считывается в регистр 24 числа, из которого передается в регистр 1 обмена. Обратный код слова с регистра 1 обмена засылается на дешифратор 7. Если прочитанное слово было пз€тым (т. е. во всех разрядах слова был записан «О, что соответствует занятости зон), то в группу старших разрядов счетчика 8 добавляется «+1 и осуществляется чтение слова из блока 23 по вновь сформированному адресу. Если прочитанное слово не было пустым, то содержимое регистра 1 обмена пересылается на шифратор 6, который определяет наименьший номер разряда, в котором записана «1, и формирует двоичный код этого номера. С шифратора 6 двоичный код передается через элемент ИЛИ 21 в младшие разряды счетчика 8. Затем производится пересылка содержимого младших разрядов счетчика 8 в дешифратор 9, установка в регистре 1 обмена в «О разряда, соответствующего возбужденной щине дешифратора 9, и засылка измененного слова из регистра 1 обмена в блок 23 по адресу в старших разрядах счетчика 8. Одновременно происходит засылка содержимого счетчика 8 в незанятый регистр 15 или 16 свободных зон. Если после этого регистр 15 или 16 остается незанятым, то производится поиск следующей свободной зоны, как указывалось выше. При заполнении регистра 15 или 16 кодами свободных зон режим поиска прекращается. Если из процессора (на чертеже не показан) поступает сигнал «Выдать в блок 22, то осуществляется выдача кода свободной зоны регистра 15 или 16 через элемент И 18 или 19 и элемент ИЛИ 20 в процессор; соответствующий регистр устанавливается в исходное состояние, и устройство переходит в редким поиска.

При работе устройства .в режиме приема освободившейся зоны по сигналу процессора «Принять, поступающему в блок 22, код освободившейся зоны из процессора заносится в счетчик 8. Если регистр 15 и 16 находится в исходном состоянии, то код зоны из счетчика 8 заносится через элемент И 13 или 14 в соответствующий регистр 15 или 16. Если

оба регистра 15 и 16 заняты кодами свободных зон, то содержимое старших разрядов счетчика 8 засылается в регистр 26 блока 23, соответствующее слово считывается из накопителя 25 в регистр 24 числа и передается в

регистр 1 обмена. Содержимое младших разрядов счетчика 8 передается на дешифратор 9, возбуждается соответствующий выход дещифратора и в соответствующем разряде слона, размещенного в регистре 1 обмена, вместо

«О записывается «1. Измененное слово засылается обратно в блок 23 по адресу старших разрядов счетчика 8.

Таким образом, в описываемом устройстве для распределения памяти последовательный

перебор разрядов в считанном из блока памяти слове заменяется параллельным анализом всех разрядов слова, что существенно увеличивает быстродействие устройства.

Формула изобретения

Устройство для распределения памяти, содержащее регистр обмена, соединенный с дешифратором обмена и через элементы И - с дещифратором зон, счетчик, входы которого

соединены с выходом дешифратора обмена и управляющей шиной, а выходы - со входами дешифратора зон, блока хранения и коммутации кодов свободных зон и выходом устройства, отличающееся тем, что, с целью

увеличения быстродействия устройства, оно содержит шифратор и элемент ИЛИ, первый вход которого подключен к управляющей шине, а выход - к одному из входов счетчика, вход шифратора соединен с выходом регистра

обмена, а выход - со вторым входом элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3601809, кл. Q ПС 7/00, 1971.

2.Авторское свидетельство № 318948, кл. G 06F 13/00, 1971.

Г7г

ttn

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для РАСПРЕДЕЛЕНИЯ ПАМЯТИ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1971 |

|

SU318948A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Устройство для управления записьюи СчиТыВАНиЕМ иНфОРМАции | 1979 |

|

SU809181A2 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1986 |

|

SU1322298A2 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1985 |

|

SU1267427A1 |

| ФОНД | 1973 |

|

SU408308A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1977 |

|

SU682900A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1987 |

|

SU1413635A2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1971 |

|

SU297070A1 |

L

27

Авторы

Даты

1977-11-15—Публикация

1976-06-21—Подача