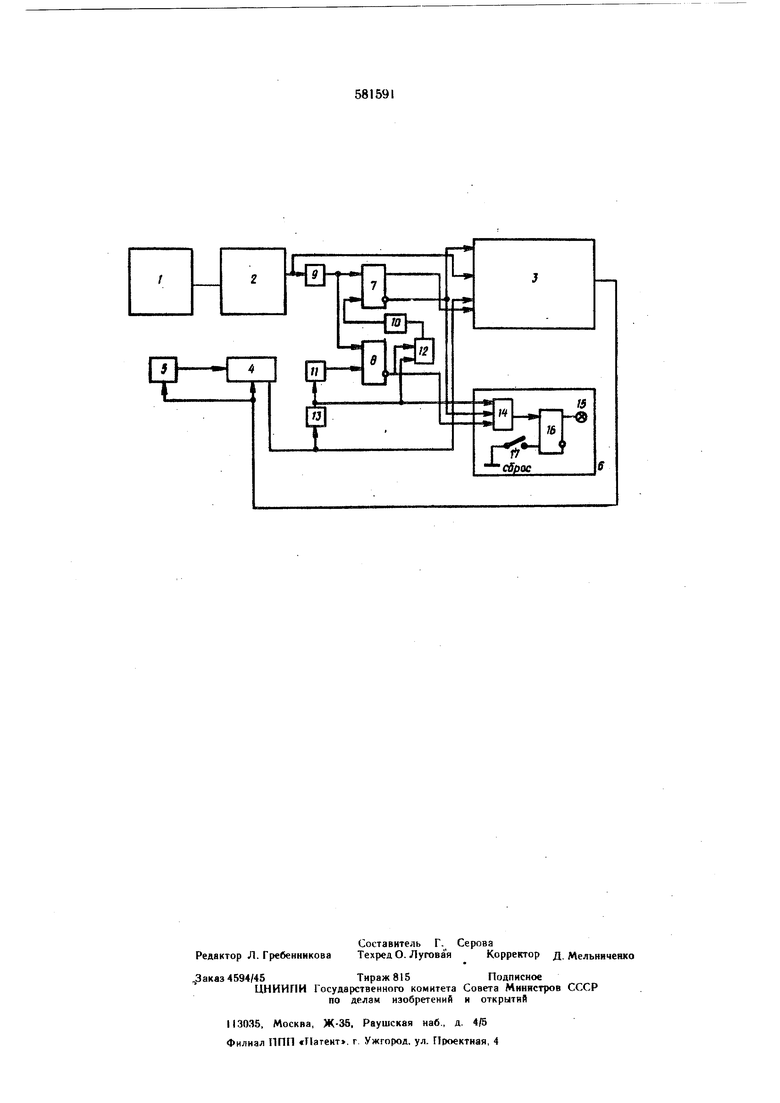

Изобретение огжкйтся к аерелаче данных и может йспольз(м$аться в синхронных помехозащнщенных системах передачи данных по каналам СВЯЗИ. Известно устройство цикловой сннхроннзацин, содержаще последовательно с.оеднненные формирователь сг{юбяруюших импульсов опознаватель маркерного сигнала и блок управления, выход которого соединен с входа мн тактового распред ителя непосредственно н через делнтель частоты, а также нндикатор состояния синхронизма {1. Однако известное устройство обладает низкой помехоустойчивостью приема при селгкцни синфазирующего импульса по длительности. Цель нзобретення-повышение помехоустойчивости устройства. Для этого в устройство цикловой синхронизации, содержащее последовательно соединенные формирователь стробнруюшнх импульсов, опознаватель маркерио го сигнала н блок управченнй, выход которого соединен с входами тактового распределителя непосредственно н через делитель частоты, а также индикатор состояния с;1НХ(Гонизма, введены два триггера, Трн блока задержки, блок совпадения и дкфференцируюший блок, при этом выход от знаватеЛя маркерного сигнала подключен к входу первого блока задержки, выход которого соединен через первый триггер с первым дополнительным входом блока управления, а через последовательно соединенные второй триггер, блок совпадения и второй блок задержкн - к другому входу первого триггера, выход которого подключен к второму дополнительному входу блока управления н к первому входу нндикатора состояния синхронизма, второй вход которого соединен с выходом второго триггера, а третий вход - с другим входом блока совпадения, с выходок дифференцирующего блока и через третий блок задержки - с другим входом второго триггера, причем вход дифференцирующего блока соеди ней с выходом тактового распределителя и с третьим дополнительным входом блока управления. Инднкатор состояния синхронизма состоит из элемента И, выход которого соедииеи с индикатором через триггер, другой Вход которого подключен к кнопке сброса. На чертеже дана структурная электрическая схема предлагаемого устройства. Устройство цикловЪй синхронизации содержит последовательно соеднненные формнрователь 1 стробирующих импульсов, ойознава- ель 2 маркерного сигнала и блок 3 управления, выход которого соединен с входами тактового распределителя 4 нештсредственно и через делитель 5 частоты, а также индикатор 6 состояния синхронизма, два триггера 7, 8, три блока 9, 10, И задержки, блок 12 совпадения и дифференцирующий блок 13. Выход опознавателя 2 маркерного сигнала подключен к входу первого блока задержки 9, выход которого соединен через первый триггер 7 с первым дополнительным входом блока 3 управления, а через последовательно соединенные второй триггер 8, блок 12 совпадения и второй блок 10 задержки - к другому входу первого триггера 7, выход которого подключен к второму дополнительному входу блока 3 управления и к первому входу индикатора 6 состояния синхронизма, второй вход которого соединен с выходом второго триггера 8, а третий вход - с другим входом блока 12 совпадения, с выходом дифференцирующего блока 13 и через третий блок 11 задержки - с другим входом второго триггера 8, причем вход дифференцирующего блока 13 соединен с выходом тактового распределителя 4 и с третьим дополнительным входом блока 3 управления. Индикatop 6 состояния синхронизма состоит из элемента И 14, выход которого соединен с индикатором 15 через триггер 16, другой вход которого подключен к кнопке 17 сброса. Устройство работает следующим образом. В исходном состоянии до поступления из канала связи первого синфазирующего импульса первый и второй триггеры 7, 8 установлены в «О, триггер 16 -в «Ь. Задний фронт первого синфазирующего импульса, пройдя через опоз -« ит-иапя поступает ченяпятель 2 маркерного сигнала, поступав, сHdudicjiD урравдения на установочный вход актового паспределителя 4, устанавливая полпжтГие соответствующее первому такту, и на Сг-гяновочный вход делителя 5 частоты, -устая.1ивая его на О 5 полной емкости, что сортnPTTTRveT середине такта. Таким способом осут ч4ляется синфазирование. Кроме того, чепрчпеовый блок 9 задержки (на время срабатывания перечисленных схем) импульс устанав .пивает первый и второй триггеры 7, 8 в «i В конце первого такта с выхода днфференцируюшего блока 13 пройдет импульс, опращиваюП1ИЙ блок 12совпадения, и параллельно через блок i 1 задержки, устанавливающий второй тоиггер 8 в «0. Блок 12 совпадения в 1-м цикле запертво 2-« ин«ле работа оказана с ГреГ-Г в К% а-„ °в .0. кнопко. ,: - триггер 7 постоянно находится в ..й9тж Га;,1ТроТод;Т 1;Г /Г Г ;l ЖЕГф- нто-ЛГ |р37Гт.Г/г 0 аТДГГ. через третий блок П задержки. В 3-м цикле работа устройства показана в случае искажения одного синфазирующего импульса: наложение помехи увеличило длительность импульса, в результате чего он не прошел через опознаватель 2 маркерного сигнала. В результате второй триггер 8 не установился в «1, и в конце первого такта через блок 12 совпадения прошел импульс, который через второй блок 10 задержки установил первый триггер 7 в «О. Синфазировки в этом цикле не произощло. В случае искажения подряд второго синфазирующего импульса (импульс отсутствует - замирание) в конце первого такта импульс с дифференцирующего блока 13 пройдет через элемент И 14 и установит триггер- 16%«I. Загорится световой индикатор 15. После вхожДеиия системы в синхронизм индикатор 5 будет гореть, пока оператор не зафиксирует его и не выключит кнопкой 17 сброса. Предлагаемое устройство, по сравнению с известным; обладает повышенной помехоустойчивостью синфазировки. Формула изобретения I. Устройство цикловой синхронизации, содержащее последовательно соединенные формирователь стробирующих импульсов, опознаватель маркерного сигнала и блок управления, выход которого соединен с входами тактового распределителя непосредственно и через делитель частоты, а также индикатор состояния синхронизма, отличающееся тем, что, с целью ctt«AHuii«.Md, u,utuKj Kt;t.H км, что, с целью 1овыщения помехоустойчивости устройства, введены два триггера, три блока задержки, блок совпадения и дифференцирующий блок, при этом выход опознавателя маркерного сигнала подключен к входу первого блока задержKH, выход которого соединен чеесз первый тригrep с первым дополнительным входом блока управления, а через последовательно соединен„це второй дриггер, блок совпадения и втордд блок задержки - к другому входу первого триггера, выход которого подключен к второму дополнительному входу блока управления и к „ервому входу индикатора состояния синхро. второй вход которого соединен с выхо второго триггера, а третий вход - с другим входом блока совпадения, с выходом дифферен- Гд Ге о Г -ра.пР ,™:tb T«P- «- ™-дГо;н„ Г„Т,Годо«То ка%праш,е„„я. 2. Устройство по п. I. омитоющеемтем. что ™1: Гото;Тс нТГнк -.-р-гГс«г ™ ;;и о; Лаии„,„р™т«е.о.н.„а. Ю1. Н W L 7АЯ. 1У/.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное устройство цикловой синхронизации | 1972 |

|

SU443491A1 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ | 1971 |

|

SU305578A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1971 |

|

SU300955A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| ПРИЕМНИК СИНХРОСИГНАЛА | 2002 |

|

RU2242093C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1992 |

|

RU2019046C1 |

Авторы

Даты

1977-11-25—Публикация

1975-12-03—Подача