(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU920832A1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2011 |

|

RU2444052C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

1

Изобретение относится к цифровой вычислительной технике и может найти применение в электронных вычислительных машннах.

Известно запоминающее устройство, содержащее поле памяти и регистр адреса, выходы которого соединены с адресными входами поля памяти, а .входы подключены к адресным входам устройства 1. Недостаток этого устройства заключается в том, что в нем все поле памяти является функционально однородным, т. е. обращения ко всем ячейкам требует одинакового вре.мени.

Известно также наиболее близкое по технической сзщности к изобретению запоминающее усгройство, которое, как и данное устройство, содержит поле памяти, информационные входы и выходы которого соединены с одноименными входами и выходами запоминающего устройства, и первый регистр адресов слов, вход параллельного ввода адресов слов которого подключен к одноименному входу запомипающего устройства 2.

Однако в таком устройстве при частом изменении между адресами в главной и вспомогательной области поля памяти содержание обоих адресных регистров очень часто взаимно обменивается и адреса должны храниться в буферной памяти в других дополнительных

устройствах. Кроме того, в запоминающем устройстве определяется только один адрес. В результате замедляется процесс проведения операций.

Цель изобретения - повыщение быстродействия устройства.

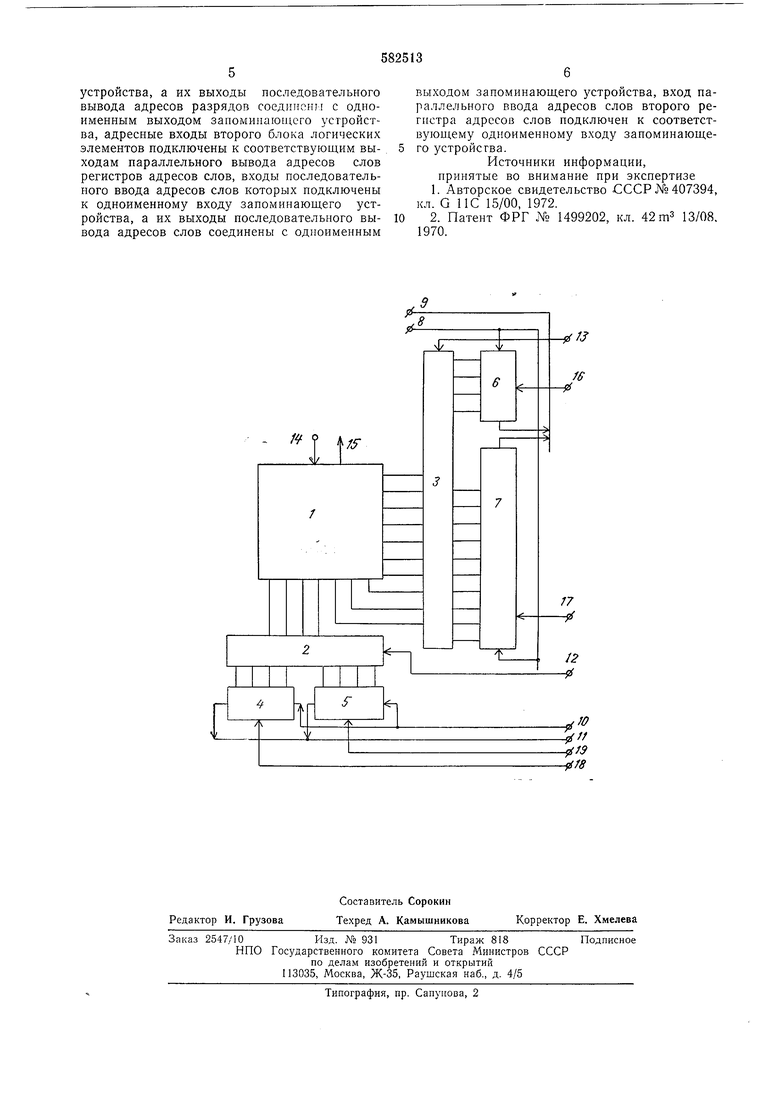

Это достигается тем, что в устройство введен второй регистр адресов слов, два регистра адресов разрядов и два блока логических

элементов, выходы которых соединены с соответствующими адресными входами поля намяти, а унравляющие входы подключены к соответствующим входам микропрограммного управления запоминающего устройства. Входы первого блока логических элементов подключены к соответствующим выходам параллельного вывода адресов разрядов регистров адресов разрядов, входы параллельного ввода адресов разрядов которых подсоедннены к

одноименным входам запомпнающего устройства. Входы последовательного ввода адресов разрядов регистров адресов разрядов соединены с одноименным входом запоминающего устройства, а их выходы последовательного

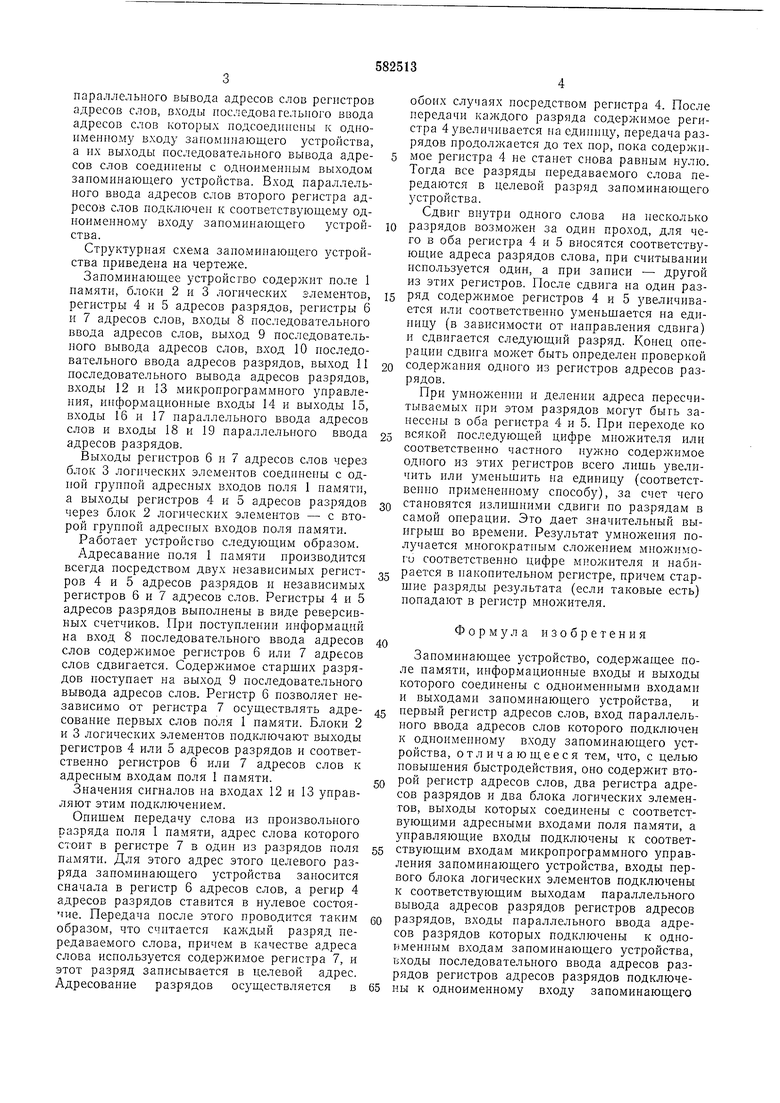

вывода адресов разрядов - с одноименным выходом запоминающего устройства. Адресные входы второго блока логических элементов подключены к соответствующим выходам параллельного вывода адресов слов регистров адресов слов, входы последовательного ввода адресов слов которых подсоединепы к одноимеппому входу запомпиающего устройства, а их выходы последовательного вывода адресов слов соединены с одноименным выходом запоминающего устройства. Вход параллельного ввода адресов елов второго региетра адресов слов подключен к соответствующему одноименному входу запоминающего устройства. Структурная схема запоминаюп;его устройства приведена на чертеже. Запоминающее устройство содержит поле 1 памяти, блоки 2 и 3 логичееких элементов, регистры 4 и 5 адресов разрядов, регистры 6 и 7 адресов слов, входы 8 последовательного ввода адресов слов, выход 9 последовательного вывода адресов слов, вход 10 последовательного ввода адресов разрядов, выход 11 последовательного вывода адресов разрядов, входы 12 и 13 микропрограммного управления, информационные входы 14 и выходы 15, входы 16 и 17 параллельного ввода адресов слов и входы 18 и 19 параллельиого ввода адресов разрядов. Выходы регистров 6 и 7 адресов слов через блок 3 логических элементов соединены с одной группой адрееных входов поля 1 памяти, а выходы региетров 4 и 5 адресов разрядов через блок 2 логических элементов - с второй группой адресных входов поля памяти. Работает устройство следующим образом. Адресавание поля 1 памяти производится всегда посредством двух независимых регистров 4 и 5 адресов разрядов и независимых регистров 6 и 7 адрееов слов. Регистры 4 и 5 адресов разрядов выполнены в виде ревереивных счетчиков. При поступлении информации на вход 8 последовательного ввода адресов слов содержимое регистров 6 или 7 адресов слов сдвигается. Содержимое старших разрядов поступает на выход 9 последовательного вывода адресов слов. Регистр 6 позволяет независимо от регистра 7 осуществлять адресование первых слов поля 1 памяти. Блоки 2 и 3 логических элементов подключают выходы регистров 4 или 5 адресов разрядов и соответственно регистров 6 или 7 адресов слов к адресным входам поля 1 памяти. Значения сигналов на входах 12 и 13 управляют этим подключением. Опищем передачу елова из произвольного разряда поля 1 памяти, адрес слова которого ciOET в регистре 7 в один из разрядов ноля памяти. Для этого адрес этого целевого разряда запоминающего устройства заносится сначала в регистр 6 адресов слов, а регир 4 адресов разрядов ставится в нулевое состоячие. Передача после этого проводится таким образом, что считается каждый разряд передаваемого слова, причем в качестве адреса слова используется содержимое региетра 7, и этот разряд записывается в целевой адрес. Адресование разрядов осуществляется в обоих случаях посредетвом регистра 4. После передачи каждого разряда содержимое регистра 4 увеличивается на едипицу, передача разрядов продолжается до тех пор, пока содержимое регистра 4 не станет снова равным нулю. Тогда все разряды передаваемого слова передаются в целевой разряд запоминающего устройства. Сдвиг внутри одного слова на несколько разрядов возможен за один проход, для чего в оба регистра 4 и 5 вносятся соответствующие адреса разрядов слова, при считывании использзется один, а при записи - другой из этих регистров. После сдвига на один разряд содержимое регистров 4 и 5 увеличивается или соответственно уменьщается на едипицу (в зависимости от направления сдвига) и сдвигается следующий разряд. Конец операции сдвига может быть определен проверкой содержания одного из регистров адресов разрядов. При умножении и делении адреса пересчитываемых при этом разрядов могут быть занесены в оба регистра 4 и 5. При переходе ко всякой последующей цифре мпожителя или соответственно частного нужно содержимое одиого из этих регистров всего лищь увеличить или уменьщить на единицу (соответственно примененному способу), за счет чего становятся излишними сдвиги по разрядам в самой операции. Это дает значительный выигрыщ во времени. Результат умножения получается мпогократпым сложением множимого соответственно цифре множителя и набирается в накопительном регистре, причем старщие разряды результата (если таковые есть) попадают в регистр множителя. ормула изобретения Запоминающее устройство, содержащее поле памяти, информационные входы и выходы которого соединены с одноименными входами и выходами заноминающего устройства, и первый регистр адресов елов, вход параллельпого ввода адресов слов которого подключен к одноименному входу запоминающего устройства, отличающееся тем, что, с целью новыщения быстродействия, оно содержит второй регистр адресов слов, два регистра адресов разрядов и два блока логических элементов, выходы которых соединены с соответствующими адресными входами поля памяти, а управляющие входы подключены к соответствующим входам микропрограммного управления запоминающего устройства, входы первого блока логических элементов подключены к соответствующим выходам параллельного вывода адресов разрядов регистров адресов разрядов, входы параллельного ввода адресов разрядов которых подключены к одноименным входам запоминающего устройетва, входы последовательного ввода адресов разрядов регистров адресов разрядов подключены к одноименному входу запоминающего

устройства, а их выходы последовательного вывода адресов разрядов соедииоим с одноименным выходом запоминающего устройства, адресные входы второго блока логических элементов подключены к соответствующим выходам параллельного вывода адресов слов регистров адресов слов, входы последовательного ввода адресов слов которых подключены к одноименному входу запоминающего устройства, а их выходы последовательного вывода адресов слов соединены с одноименным

/

и

выходом запоминающего устройства, вход параллельного ввода адресов слов второго регистра адресов слов подключен к соответствующему одноименному входу запоминающего устройсгва.

Источники информации, иринятые во внимание при экспертизе

-ff/J

-

Авторы

Даты

1977-11-30—Публикация

1972-02-29—Подача