(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1305681A1 |

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1277107A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043653A1 |

| Микропрограммный модуль | 1984 |

|

SU1193675A1 |

| Запоминающее устройство | 1976 |

|

SU613401A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Микропрограммное устройство управления | 1979 |

|

SU905818A1 |

| Устройство для отображения информации | 1985 |

|

SU1354183A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1062701A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

Изобретение отностхзя к вычислителшб технике и может быть использовано в упра/1ЯЮШИХ устройствах систем коммутации сосйшений.

Известно устройство для управления обработкой программе имеющих различный приоритет, в установке для обработки данных l.

Недостатком этого устройства является необходимость затрат времени на выполнение арифметических операций оля определения программы, имеющей в данный момент наивысший приоритет.

Наиболее близким к изобретению техническим решением является устройство программного управления для системы дальней Гвлефонной свяэ управляемой сэсреаоТоченио хранимой программой,содержащее вхооные регистры, дешифраторы, микропрограммную память, адресные элементы И, влемент ИЛИ, генератор тактовой частоты, развертывающий блок и элемент И запуска развертывающего блока 2.

Недостатком устройства является значительные временные затраты на выбор мик- , ропрограмм, так как выбор микропрограммы, имеющей наивысший приоритет по сравнению с остальными микропрограмма;ли, находгацимися в очереди, осуществляется последова- тельным просмотром приоритетов и анализом очередей заявок всех микропрограмм.

Целью изобретения являе;{ря сокращение времени выборки программ.

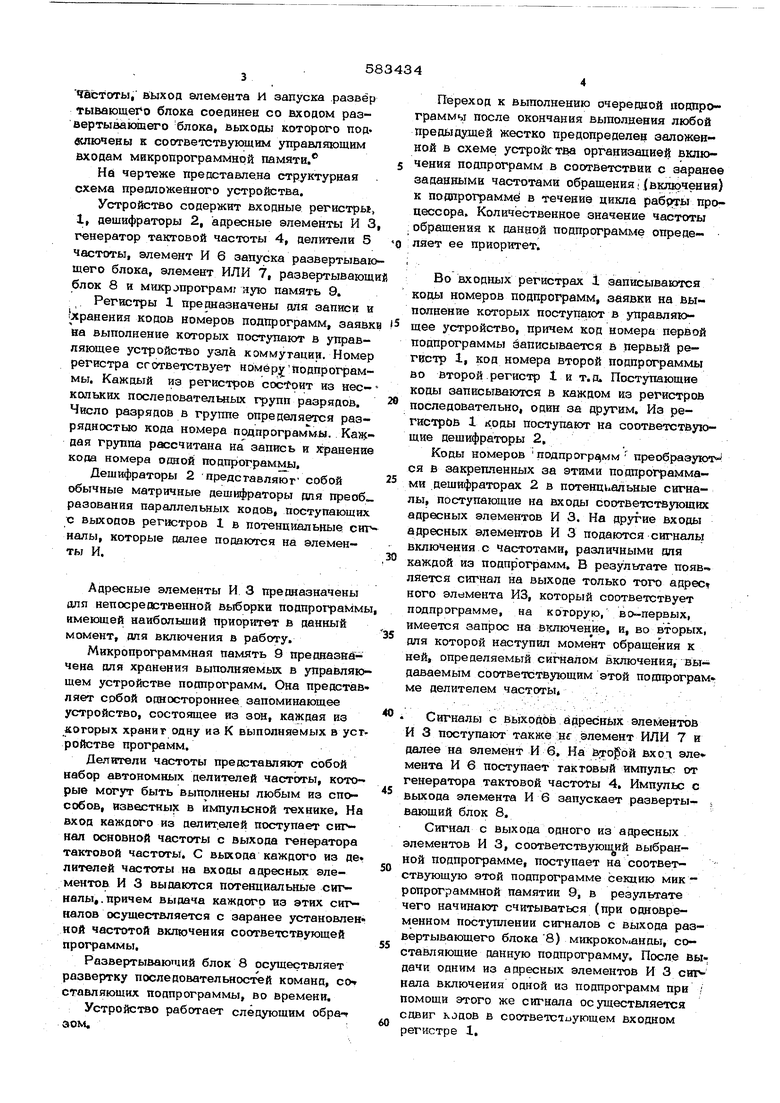

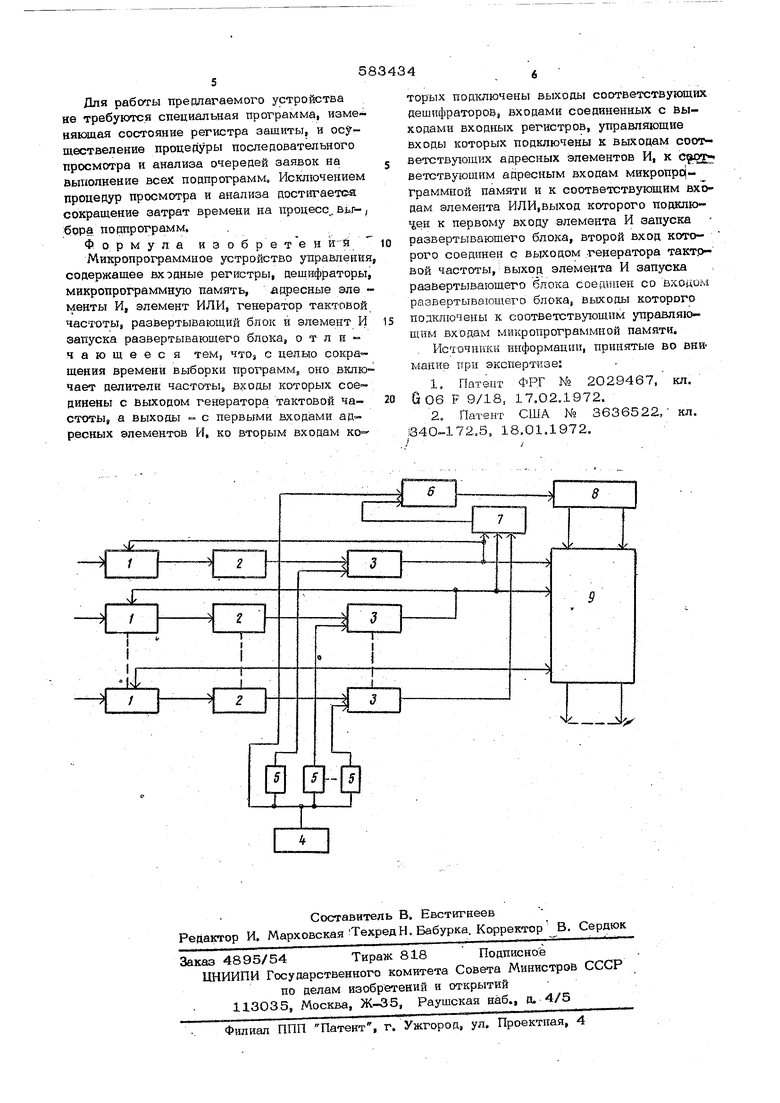

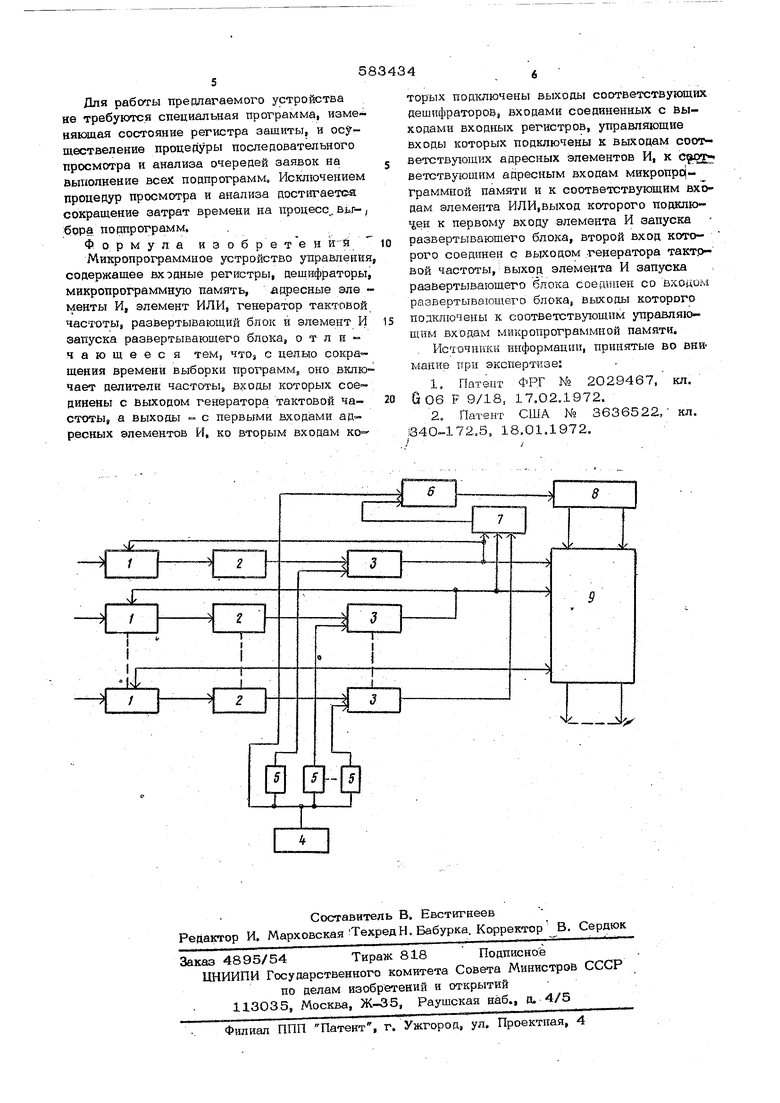

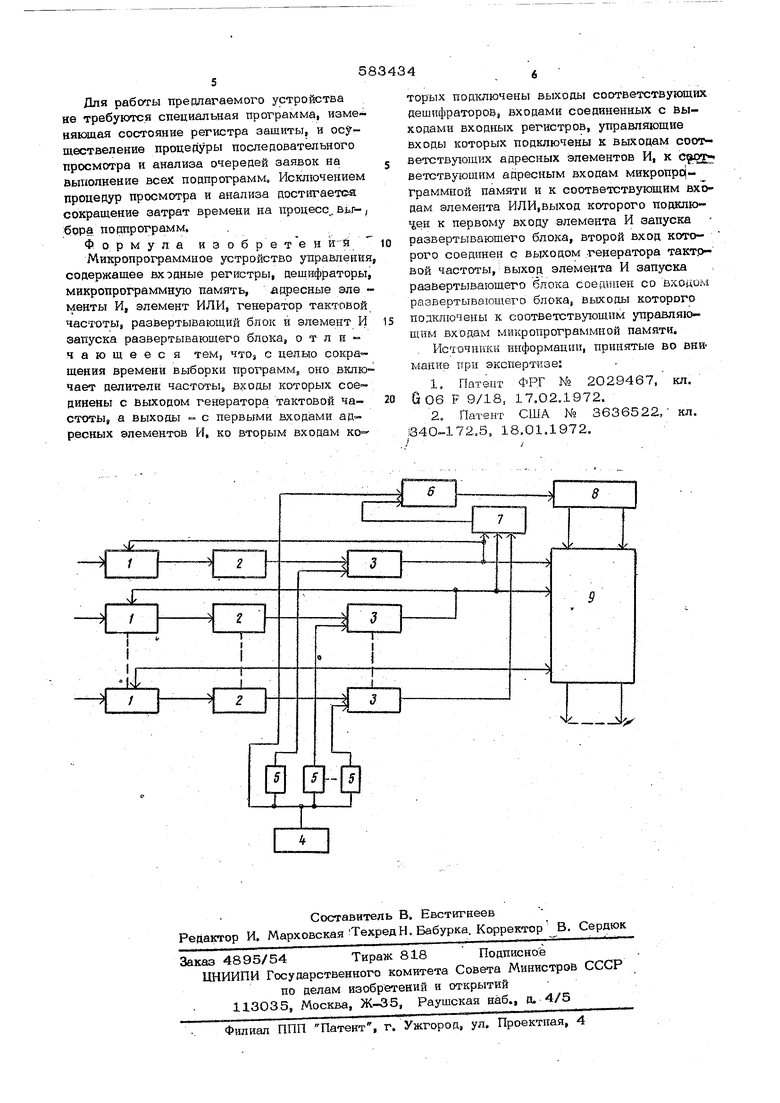

Для этого устройство содержит Дчэлители частоты, входь которых соединены с выходом генератора тактовой частоты, а выходы с первыми входами адресных элементов И, . к вторым входам, которых подключены выходы дешифраторов, входами ойединенных с выходами входных регистров, управляющие входы которых подключены к выходам соответствующих адресных элементбв И, к соответствующим адресным входам микропрограммной памяти и к соответствующим вхо, дам элемента ИЛИ, выход которого подклн чен к первому входу элемента Изапуска развертывающего блока, второй вход KOTOpt го соединен с выходом генератора тактовой частоты, выход элемента И запуска развёр тывающе1 о блока соединен со входом развертываюшего блока, выходы которого под. жлючены к соответствующим управляющим входам микропрограммной памяти. На чертеже представлена структурная схема предложенного устройства. Устройзтво содержит входные регистры, if дешифраторы 2, адресные элементы И 3 генератор тактовой частоты 4, делители 5 частоты, элемент И 6 запуска развертываю адего блока, элемент ИЛИ 7, развертывающ блок 8 и микр програмг яую память 9. Регистры 1 предназначены для записи и ;.хранения кодов номеров подпрограмм, заявк иа выполнение которых поступают в управляющее устройство узла коммутации. Номер регистра сгответствует номеруподпрограммы. Каждый из регистров сострит из нескачьких последовательных групп разрядов. Число разрядов в группе определяется разрядностью кода номера прдпрограм мы. Каждая группа рассчитана на запись и зфанение кода номера одной подпрограммы, Дещифраторы 2 предсгавляюг собой обычные матричные дешифраторы для преоб разования параллельных кодов, поступающих с выходов регжзтров 1 в потенциальные сиг налы, которые далее подаются на элементы И. Адресные элементы И 3 предназначены ОЛЯ непосредственной выборки подпрограммы имеющей наибольший приоритет в данный момент, для включения в работу. Микропрограммная память 9 предназнаГ-чена нля хранения выполняемых в управляющем устройстве подпрограмм. Она представляет собой ошюстороннее. запоминающее устройство, состоящее из зон, каждая из когорых хранит одну из К выполняемых в устройстве программ. Делители частоты представляют собой набор автономных делителей частоты, которые могут быть выполнены любым из способов, известных в импульсной технике. На вход каждого из делит.елей пххггупает сигнал основной частоты с выхода ген атора тактовой частоты. С выхода каждого из де. лителей частоты на входы адресных элементов И 3 выдаются потенциальные сигналы, . причем выдача каждогр из этих сигналов осуществляется с заранее установленной частотой включения соответствующей программы. Развертывающий блок 8 осуществляет развертку последовательностей команд, со ставляющих подпрограммы, во времени. Устройство работает следующим обра- аом. Переход к выполнению очередной подпрограммы после окончания выполнения любой предыдущей жестко предопределен заложенной в схеме устройства организацией включения подпрограмм в соответствии с заранее заданными частотами обращения; fвключения) к подпрограмме в течение цикла рабрты процессора. Количественное значение частоты обращения к данной подпрограмме определяет ее приоритет. Во входных регистрах 1 записываются коды номеров подпрограмм, заявки на выполнение которых поступают в управляюще устройство, причем код номера первой подпрограммы Записывается в первый регвстр 1, код номера второй подпрограммы во второй регисгф t и т.д. Поступающие коды записываются в каждом из регистров последовательно, од1вд за другим. Из регистров 1 коды поступают на соответствующие Дещифраторы 2. Коды номеров подпрограмм преобразуются в закрепленных за этими подпрограммами дещифраторах 2 в потенциальные сигналы, поступающие на входы соответствующих адресных элементов И 3. На другие входы адресных элементов И 3 подаются сигналы включения с частотами, различными для каждой из подпрограмм, В результате появ-. ляется сигнал на выходе только того адрес ного элемента ИЗ, который соответствует подпрограмме, на которую, во-первых, имеется запрос на включен ие, и, во вторых, для которой наступил момент обращения к ней, определяемый сигналом включения, выдаваемым соответствующим этой подпрограм ме делителем частоты, Сигналы с выходбв адресных элементов И 3 поступают также не элемент ИЛИ 7 и далее на элемент И 6, На В5го{5ой вхон эле% мента И 6 поступает тактовый импульс от генератора тактовой частоты 4. Импульс с выхода элемента И 6 запускает разверты- . вающий блок 8, Сигнал с выхода одного из адресных элементов И 3, соответствующий Выбранной подпрограмме, поступает на соответствующую этой подпрограмме секцию микропрограммной памятии 9, в резулм-ате чего начинают считываться (при одновременном поступлении сигналов с выхода развертывающего блока 8) микрококлнды, составляющие данную подпрограмму. После вы-; дачи одним из адресных элементов И 3 сигнала включения одной из подпрограмм при / помощи этого же сигнала осуществляется сдвиг кодов в соответс7иующем входном регистре 1.

Авторы

Даты

1977-12-05—Публикация

1975-12-22—Подача