(54) ПАРАЛЛЕЛЬНЫЙ ОДНОФАЗНЫЙ РЕГИСТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Асинхронный регистр сдвига (его варианты) | 1982 |

|

SU1140173A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1531172A1 |

| Устройство для считывания и обработки изображений | 1988 |

|

SU1513486A1 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU822292A1 |

1

Изобретение относится к области Ы)1 числительной техники.

Известен параллельный однофазный регистр, содержащий ячейки пагу5яти и логические элементы И-НЕ . Его недостатком является низкая надежность.

Наиболее близким по технической сущности к изобретению являeтc параллельный однофазньтй регистр, содержащий ячейки памяти, первые управпяющие входы которых подключены к выходу элемента НЕ, вход которого соединен со вторыми управляющими входами ячеек памяти и управляющей шиной регистра 2,

Этот регистр также недостаточно надеже

Целью изобретения является повышение надежности регистра.

Поставленная цель достигается тем, что предложенный регистр содержит управляющий триггер, выход которого подключен к выходной и)ине регистра, а его входы соединены с выходами ячеек памяти и элемента НЕ, и тем, что ячейка памяти содержит элемент НЕ, элемент И-НЕ и элемент И-ИЛИНЕ с функциональными расширителями по И,

выход которого соединен со входом элемента НЕ, а входы подключены к разрядной информационной шине регистра, первому упра&ляюшему входу ячейки памяти и Ыз1ходу элемента НЕ, соединенному с первым выходом ячейки памяти и первым входом элемента И-НЕ, другие входы которого подключены к разрядной информационной шине регистра и второму управляющему входу ячейки памяти, второй выход, которой соединен с выходом элемента И-НЕ, а также тем, что упра&пяюший триггер содержит элемент НЕ и элемент И-ИЛИ-НЕ с функциональными расширителями по И, выход которого подключен ко входу элемента НЕ, а входы подключены ко входам управляющего триггера и элемента НЕ, соединенному с выходом управляющего триггера и выходной шиной регистра.

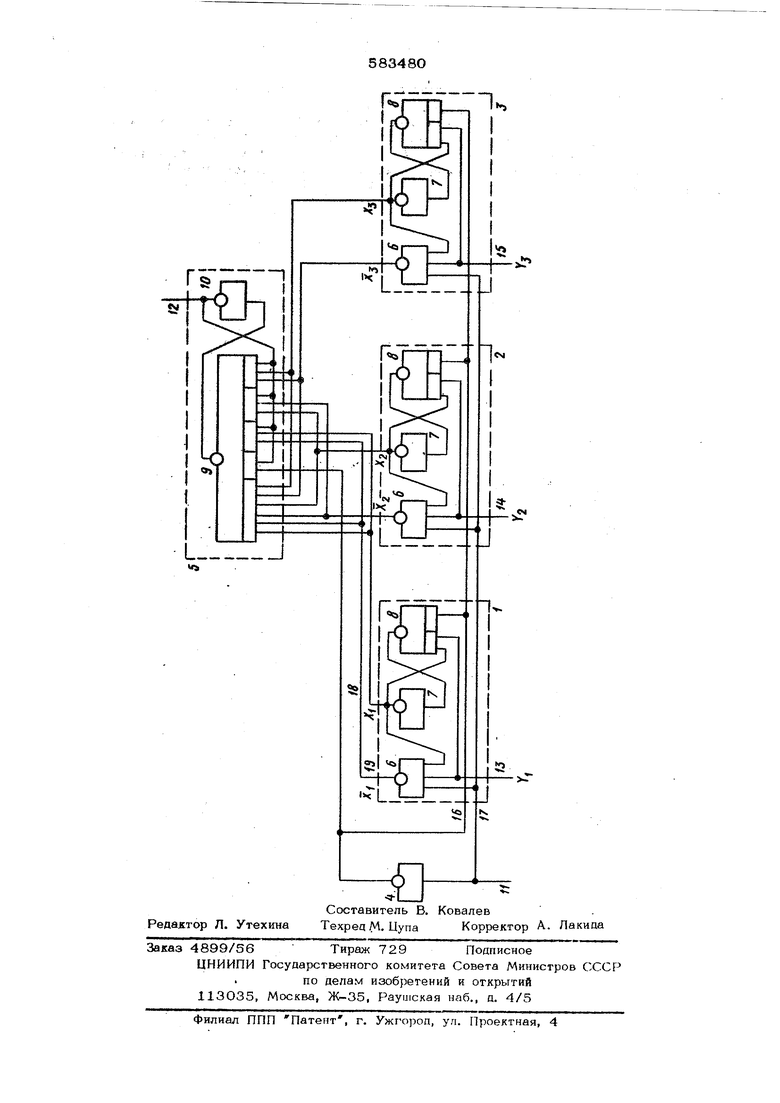

На чертеже представлена схема регистре.

Параллельный однофазный регистр содержит ячейки 1-3 памяти, элемент НЕ 4 и :управляюший триггер 5.

Каждая ячейка памяти содержит элемент И-НЕ 6, элемент НЕ 7 и эпемент И-ИЛИflF 8 с функциональными расширителями по И, Управлякяиий триггер 5 содержит элемент И-ИЛИ-НЕ 9 с функциональными расширителями по И и элемент НЕ 10. Вход элемента НЕ 4 соединен с упра&. лягошей шиной 11 регистра, а выход элемента НЕ 10 - с выходной шиной 12. Первый вход элемента И-НЕ 6 ячейки памяти соедилен с выходом элемента НЕ 7, а его другие входы - с соответствующей из разрядных информационных шин 13-15, и управляющей шиной 11 регистра. Выходы элементовИ-НЕ и НЕ 7 каждой ячейки памяти являютс парафазными выходами Xj ,Х ,Х, 5(j,Xj, Xj соответствуклиих разрядов регистра. Ячейка памяти имеет первыр 16 и второй 17 управляющие входы и первый 18 и второй 19 выходы. Устройство работает следующим образом. Перед поступлением входных сигналов на шины 13-15 ячеек на них подаются соответствующие уровню логической единицы сигналы, т.е. в исходном состоянии Yj У- «УЗ а сигнал на шине 11 соответствует уровню логического нуля. При этом сигнал на выходах элементов НЕ 4,7 и 1О и элемента И-НЕ 6 соответствует уровню логической к единицы, а сипнал на выходах элементов И-ИЛИ-НЕ 8 и 9 - уровню логического нуля. Затем на шины 13-15 ячеек памяти поступают коды вводимого числа, а на управляющую шииу 11 - сигнал уровня логической единиць. Если сигнал на разрядной информационной шине одной из ячеек памяти соответствует уровню логической .единицы, то на выходе элемента И-НЕ 6 этой ячейки устанавливается уровень логического нуля ). Если сигнал на разрядной информационной шиие соответствует урювню логического ну- ля, то выходные сигналы элементов НЕ 7 и И-ИЛИ-НЕ 8 этой ячейки памяти изменяется на противоположные только при поя лении на выходе НЕ 4 уровня логического нуля. После установки во всех ячейках памяти элементов И-НЕ 6 и НЕ 7 в противоположные состояния (Х|ФЛ|) и уровня логического нуля на выходе элемен та НЕ 4, на выходе элемента И-ИЛИ-НЕ 9 устанавливается сигнал логической , а иа выходе элемента НЕ 10 - сигнал логического нуля, что свидетельствует об окончании переходных процессов при записи кода в регистр. Сброс регистра осуществляется следукущим образом. На разрядные информационные шины 13-15 ячеек памяти подаются сигналы уро ней логической едииицы, а на управляющую шину 11 - сигнал уровня логического нуля. Если в одной из ячеек памяти бал записей код единицы, т.е,1, )(| О, то на выходе элемента И-НЕ 6 этой ячейки устанавли- веется уровень логической единицы (){« l), что свидетельствует о сбросе данной ячей-ки памяти. Если в одной из ячеек памяти был записан код нуля, то выходные сигналы элементов НЕ 7 и И-ИЛИ-НЕ 8 этой ячвйки изменятся на противоположные лишь после появления уровня логической единицы на выходе элемента НЕ 4. После установки во всех ячейках памяти элементов И-НЕ в и НЕ 7 в противоположные состояния и (уровня логической единицы на выходе art мента НЕ 4 на выходе элемента И-ИЛИ-НЕ 9 устанавливается сигнал логического нуля, а на ш 1ходе элемента НЕ 10 - сигнал логической единицы, что свидетельст ет об окончании переходных процессов при сбр. се регистра. Таким образом, при управлении с помошью выходного сигнала шины 12 процессом записи информации в регистр и его сброса устраняется влияние разбросов задержек логических элементов, т.е. повышается надежность регистра. Формула изобретения 1. Параллельный однофазный регистр, содержащий ячейки памяти, первые управляющие входы которых подключены к выходу апемеита НЕ, вход которого соединен со вторыми управляющими входами ячеек памяти и управляющей шиной регистра, о т л и чающийся тем, что, с целью повышения надежности регистра, он содержит управляющий триггер, выход которого пооключей к выходной шине регистра, а его входы соедииены с выходами ячеек памяти и элемента НЕ. 2. Регистр по п. 1,отлячающиЯн с я тем, что ячейка памяти содержит алв- мент НЕ, элемент И-НЕ и элемент И-ИЛИНЕ с функциональными расширителями по И, выход которого соединен со входом элемента НЕ, а входы подключены к разрядной информационной шине регистра, первому управляющему входу ячейки памяти в выходу элемента НЕ, соединенному с первым выходом ячейки памяти и первым входом элемента И-НЕ, другие входы которого подключены к разрядной информационной шиие регистра и второму управл5пощему входу ячейки памяти, второй выход которой соединен с выходом элемента И-НЕ. 3. Регистр по п. 1, отличают ис я тем, что управляющий триггер содержит

элемент НЕ и элемент И-ИЛИ-НЕ с фуикЦ ональными расширителями по И, выхоп кото рого подключен ко входу элемента НЕ, моды подключены ко входам управляющего триггера и выходу элемента НЕ, соединенному О выходом управляющего триггера и выхооной шиной регистра.

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1977-12-05—Публикация

1976-02-04—Подача