1

Изобретение относится к области автоматики и вычислительной техники, а именно к устройствам для обнарзжеиня иеисправностей в устройствах, преобразования скорости передачи информации.

В области автоматики и вычислительной техники часто используется устройство, выполняющее задачу преобразоваиия скорости передачи информации при осуществлении приемопередачи информации между устройствами с различиыми скоростями работы, основным узлом которого является накопитель. Причем во многих случаях условия сопряжения требуют установки в устройстве преобразования скоростн передачи информации двух переключающихся буферных накопителей, работающих поочередно то в режиме записи, то в режиме считывания.

В процессе функциоиироваиия устройства преобразования скорости передачи информации в составе сложных систем очень важным является обеспечение исправности этих устройств. Для этого необходимо располагать достаточио эффективными средствами контроля, способными не только обнаружить наличие неисправностей, но и указывать их местонахождение. Одним из таких средств является контроль устройства с помощью испытательных программ. Для контроля устройства преобразования скорости передачи информации требуется специальное ус1ройство, которое формировало бы проверочный тест, кодовые комбинации которого изменялись бы по определенному закону, для записи в один накопитель, одновременно считывало бы информацию из другого накопителя и анализировало бы резз льтаты прохождения проверочного теста через каждый накопитель контролируемого устройства.

Известны устройства для контроля блоков передачи информации, содержащее триггеры, блок сравнения кодов, элементы И и блок неравнозначности 1, и з стройство для контроля блоков передачи информации, содержащее счетчик адреса, логические элементы, элементы задержки, регистры управления и контроля, блок фиксации ощибки 2.

Педостатком известного устройства для контроля блоков передачи информации является

отсутствие возможности диагностики неисправности его, так как анализирз ется прохождение не каждого слова проверочного теста через объект контроля, а всего теста по сумме слов теста. Недостатком второго известного устройства для контроля блоков передачи информации является отсутствие контроля программной части устройств преобразования скорости передачи информации, осз-ществляющей подключение накопителей то на запись, то на

считывание, так как оно не осзществляет одновременно с выдачей проверочного теста в контролируемое устройство прием из контролируемого устройства и анализ информации, посланной в него за предшествующий период времени.

Наиболее близким решением к предлагаемому является устройство для контроля блоков передачи информации, содержаш,ее проверяемый и эталонный блоки, блок сравнения, два элемента И, элемент задержки, стробирующий элемент И, элемент ИЛИ, счетчик, дешифратор, генератор импульсов, триггер, кнопки пуска и сброса, причем выходы проверяемого и эталонного блоков соединены с входами блока сравнения, выход которого соединен с первым входом первого элемента И, выход первого элемента И соединен с первым входом элемента ИЛИ, выход которого соединен с нулевым входом триггера, единичный выход триггера соединен с первым входом второго элемента И, второй вход которого через контакты кнопки пуска соединен с выходом генератора импульсов, выход генератора импульсов через контакты кнопки сброса соединен с единичным входом триггера и с установочным входом счетчика, первый выход которого соединен с дешифратором, первый выход дешифратора соединен с первым входом стробирующего элемента И, второй вход которого соединен с выходом элемента задержки и вторым входом первого элемента И, выход стробирующего элемента И соединен с первым входом проверяемого и эталонного блоков 3.

Недостатком этого устройства является недостаточно полный контроль объекта, представляющего собой блок передачи информации, осуществляющего преобразование скорости передачи информации с двумя буферными накопителями, так как не осуществляется формирование проверочного теста для записи одного кадра в проверяемую схему с одновременным считыванием и анализом результатов прохождения предшествующего кадра из проверяемой схемы, что необходимо для контроля такого устройства преобразования скорости.

Целью изобретения является расширение функциональных возможностей устройства.

Это достигается тем, что устройство дополнительно содержит блок проверочного теста, делитель частоты, счетчик количества слов, два дополнительных элемента И,: два дополнительных элемента задержки, два дополнительных триггера, два дополнительных элемента ИЛИ, причем второй выход дешифратора соединен с первым входом первого дополнительного элемента ИЛИ, второй вход которого соединен с нулевым входом второго дополнительного триггера, с установочным входом делителя частоты, с единичным входом триггера, выход первого дополнительного элемента ИЛИ соединен с единичным входом первого дополнительного триггера, нулевой вход которого соединен с выходом второго дополнительного элемента ИЛИ, первый выход счетчика количества слов соединен с первым входом второго дополнительного элемента ИЛИ, второй вход которого соединен со вторым выходом счетчика количества слов и единичным входом второго дополнительного триггера, выход первого дополнительного элемента И соединен с входом блока проверочного теста и со счетным входом счетчика количества слов, выход второго элемента И соединен со счетным входом делителя частоты и первым входом первого дополнительного элемента И, второй вход которого соединен с выходом первого дополнительного элемента задержки, единичный выход первого дополнительного триггера соединен с входом первого донолнительного элемента задержки, выход делителя частоты соединен с первым входом второго дополнительного элемента И, второй вход которого соединен с выходом второго дополнительного элемента задер}кки, единичный выход второго дополнительного триггера соединен с входом второго дополнительного элемента задержки, выход блока проверочного теста соединен со вторым входом проверяемого блока.

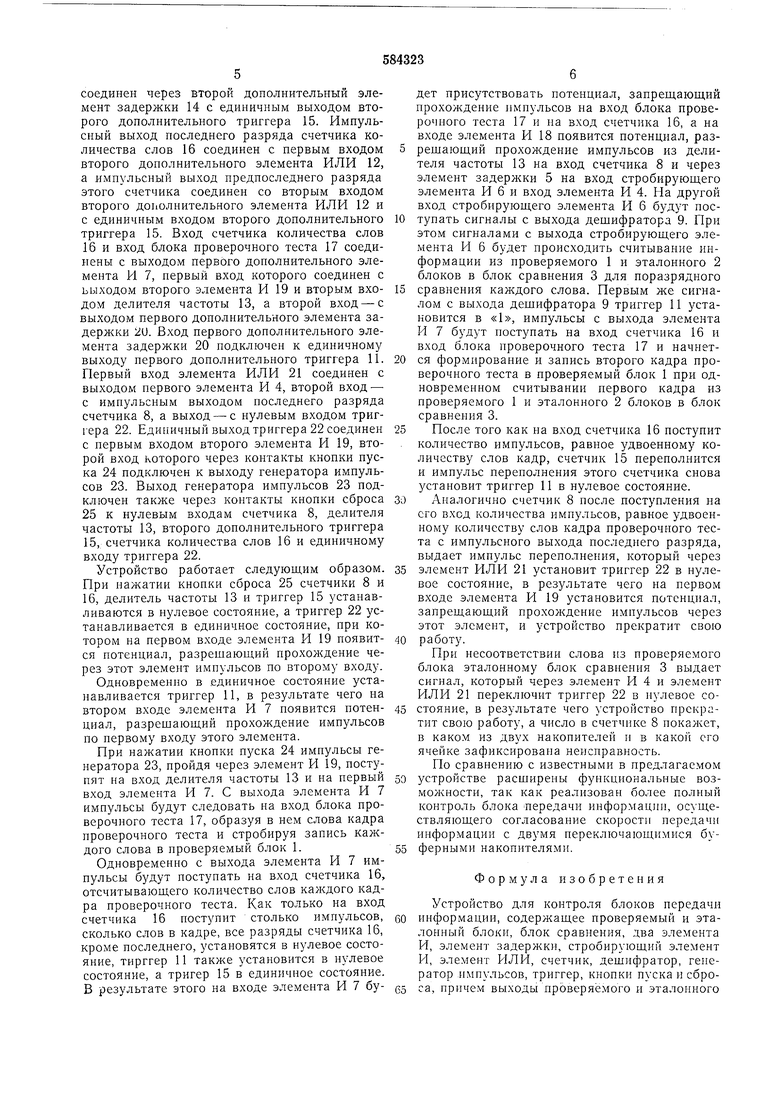

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство для контроля блоков передачи информации содержит проверяемый блок 1, эталонный блок 2, блок сравнения 3,; первый элемент И 4, элемент задержки 5, стробирующий элемент И 6, первый дополнительный элемент И 7, счетчик 8, дешифратор 9у первый дополнительный элемент ИЛИ 10, первый дополнительный триггер И, второй донолнительный элемент ИЛИ 12, делитель частоты 13, второй дополнительный элемент задержки 14, второй дополнительный триггер 15, счетчик количества слов 16, блок проверочного теста 17, второй дополнительный элемент И 18, второй элемент И 19, первый дополнительный элемент задержки 20, элемент ИЛИ 21, триггер 22, генератор импульсов 23, кнопка пуска 24, кнопка сброса 25. Идентичные выходы блоков 1 и 2 подключены; |К ,входам блока сравнения 3, выход которого соединен с первым входом первого элемента И 4. Второй вход первого элемента И 4 соединен с выходом элемента задержки 5 и входом стробирующего элемента И 6, выход которого соединен с первыми входами проверяемого 1 и эталонного 2 блоков. Вход элемента задержки 5 соединен с выходом второго дополнительного элемента И 18 и со счетным входом счетчика 8. Иервый выход счетчика 8 соединен с входом дешифратора 9, первый выход которого соединен с первым входом стробирующего элемента И 6, а второй выход соединен с первым входом первого дополнительного элемента ИЛИ 10. Выход первого дополнительного элемента ИЛИ 10 соединен с единичным входом первого дополнительного триггера 11, нулевой вход которого соединен с выходом второго дополнительного элемента ИЛИ 12. Первый вход второго дополнительного элемента И 18 соединен с выходом делителя частоты 13, а второй вход

соединен через второй дополнительный элемент задержки 14 с единичным выходом второго дополнительного триггера 15. Импульсный выход последнего разряда счетчика количества слов 16 соединен с первым входом второго дополнительного элемента ИЛИ 12, а импульсный выход предпоследнего разряда этого счетчика соединен со вторым входом второго дополнительного элемента ИЛИ 12 и с единичным входом второго дополнительного триггера 15. Вход счетчика количества слов 16 и вход блока проверочного теста 17 соединены с выходом первого донолнительного элемента И 7, первый вход которого соединен с ьыходом второго элемента И 19 и вторым входом делителя частоты 13, а второй вход - с выходом первого дополнительного элемента задержки 20. Вход первого дополнительного элемента задержки 20 подключен к единичному выходу первого дополнительного триггера 11. Первый вход элемента ИЛИ 21 соединен с выходом первого элемента И 4, второй вход- с импульсным выходом последнего разряда счетчика 8, а выход - с нулевым входом триггера 22. Единичный выход триггера 22 соединен с первым входом второго элемента И 19, второй вход которого через контакты кнопки пуска 24 подключен к выходу генератора импульсов 23. Выход генератора импульсов 23 подключен также через контакты кнопки сброса 25 к нулевым входам счетчика 8, делителя частоты 13, второго дополнительного триггера

15,счетчика количества слов 16 и единичному входу триггера 22.

Устройство работает следующим образом. При нажатии кнопки сброса 25 счетчики 8 и

16,делитель частоты 13 и триггер 15 устанавливаются в нулевое состояние, а триггер 22 устанавливается в единичное состояние, при котором на первом входе элемента И 19 появится потенциал, разрешающий ирохождение через этот элемент импульсов по второму входу.

Одновременно в единичное состояние устанавливается триггер И, в результате чего на втором входе элемента И 7 появится потенциал, разрещающий прохождение импульсов по первому входу этого элемеита.

При нажатии кнопки пуска 24 импульсы генератора 23, пройдя через элемент И 19, иосту пят на вход делителя частоты 13 и на первый вход элемента И 7. С выхода элемента И 7 импульсы будут следовать на вход блока проверочного теста 17, образуя в нем слова кадра проверочного теста и стробируя запись каждого слова в проверяемый блок 1.

Одновременно с выхода элемента И 7 импульсы будут поступать на вход счетчика 16, отсчитывающего количество слов каждого кадра проверочного теста. Как только на вход счетчика 16 поступит столько импульсов, сколько слов в кадре, все разряды счетчика 16, кроме последнего, установятся в нулевое состояние, тирггер 11 также установится в нулевое состояние, а тригер 15 в единичное состояние. В результате этого на входе элемента И 7 будет присутствовать потенциал, запрещающий прохождение имиульсов на вход блока проверочного теста 17 и на вход счетчика 16, а на входе элемента И 18 появится потенциал, разрешающий прохождение импульсов из делителя частоты 13 на вход счетчика 8 и через элемент задержки 5 на вход стробирующего элемеита И 6 и вход элемента И 4. Па другой вход стробирующего элемента И 6 будут поступать сигналы с выхода дещифратора 9. При этом сигналами с выхода стробирующего элемента И 6 будет происходить считывание информации из проверяемого 1 и эталонного 2 блоков в блок сравнения 3 для поразрядного сравнения каладого слова. Первым же сигналом с выхода дещифратора 9 триггер И установится в «1, импульсы с выхода элемента И 7 будут поступать на вход счетчика 16 и вход блока проверочного теста 17 и начнется формирование и запись второго кадра проверочного теста в проверяемый блок 1 при одновременном считываиии иервого кадра из проверяемого 1 и эталонного 2 блоков в блок сравнения 3.

После того как на вход счетчика 16 поступит количество импульсов, равное удвоенному количеству слов кадр, счетчик 15 переполнится и импульс переполнения этого счетчика снова установит триггер 11 в нулевое состояние.

Аналогично счетчик 8 после поступления на его вход количества импульсов, равное удвоенному количеству слов кадра проверочного теста с импульсного выхода последнего разряда, выдает импульс переполнения, который через элемент ИЛИ 21 установит триггер 22 в нулевое состояиие, в результате чего на первом входе элемента И 19 установится потенциал, запрещающий прохождение импульсов через этот элемент, и устройство прекратит свою работу.

При иесоответствии слова из проверяемого блока эталонно.му блок сравнения 3 выдает сигнал, который через элемент И 4 и элемент ИЛИ 21 переключит триггер 22 в иулевое состояние, в результате чего устройство прекратит свою работу, а число в счетчике 8 покажет, в каком из двух накопителей и в какой его ячейке зафиксирована неисправность.

По сравнению с известными в предлагаемом устройстве расширены функциональные возможности, так как реализован более полный контроль блока передачи информации, осуществляющего согласование скорости передачи информации с двумя иереключающимися буферными накопителями.

Формула изобретения

Устройство для контроля блоков передачи информации, содержащее проверяемый и эталонный блоки, блок сравнения, два элемента И, элемент задержки, стробирующий элемент И, элемент ИЛИ, счетчик, дешифратор, генератор импульсов, триггер, кнопки пуска и сброса, причем выходы проверяемого и эталонного блоков соединены с входами блока сравнення, выход которого соединен с первым входом иервого элемента И, выход первого элемента И соединен с первым входом элемента ИЛИ, выход которого соединен с нулевым входом григгера, единичный выход триггера соединен с первым входом второго элемента И, второй вход которого через контакты кнопки пуска соединен с выходом генератора импульсов, выход генератора импульсов через контакты кнопки сброса соединен с единичным входом триггера и с установочным входом счетчика, первый выход которого соединен с дешифратором, первый выход дешифратора соединен с первым входом стробируюшего элемента И, второй вход которого соединен с выходом элемента задержки и вторым входом первого элемента И, выход стробируюш,его элемента И соединен с первым входом проверяемого и эталонного блоков, отличаю ш,ееся тем, что, с целью расширения функциональных возможностей, оно дополнительно содержит блок проверочного теста, делитель частоты, счетчик количества слов, два дополнительных элемента И, два дополнительных элемента задержки, два дополнительных триггера, два дополнительных элемента ИЛИ, причем второй выход дешифратора соединен с первым входом первого дополнительного элемента ИЛИ, второй вход которого соединен с нулевым входом второго дополнительного триггера, с установочным входом делителя частоты, с единичным входом триггера, выход первого дополнительного элемента ИЛИ соединен с единичным входом первого дополнительного триггера, нулевой вход которого соединен с выходом второго дополнительного элемента ИЛИ, первый выход счетчика количества слов соединен с первым входом второгодополнительного элемента ИЛИ, второй вход которого соединен со вторым выходом счетчика количества слов и единичным входом второго дополнительного триггера, выход первого дополнительного элемента И соединен с входом блока проверочного теста и со счетным входом счетчика количества слов, выход второго элемента И соединен со счетным входом делителя частоты и первым входом нервого дополнительного элемента И, второй вход которого соединен с выходом первого дополнительного элемента задержки, единичный выход первого дополнительного триггера соединен с входом первого дополнительного элемента задержки, выход делителя частоты соединен с первым входом второго дополнительного элемента И, второй вход которого соединен с выходом второго дополнительного элемента задерл ки, единичный выход второго дополнительного триггера соединен с входом второго дополнительного элемента задержки, выход блока проверочного теста соединен с вторым входом проверяемого блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 330453, кл. G 06 F 11/02, 1970. 2.Авторское свидетельство СССР № 341087, кл. G ПС 29/00, 1970. 3.Авторское свидетельство СССР № 238236, кл. G 06 F 11/00, 1967.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для ввода измерительной информации | 1986 |

|

SU1354179A1 |

| Устройство для сопряжения | 1983 |

|

SU1128246A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1033994A2 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

Авторы

Даты

1977-12-15—Публикация

1975-09-25—Подача