(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ОСНОВНОЙ И ВСПОМОГАТЕЛЬНОЙ ВЫЧИСЛИТЕЛЬНЫХ МАШИН

вавмого устройства сопр$1жения не обеспв чивает индикации обменной информации как для анализа результатов промежуточных решений, так и для контроля входной инфо1 мапин дополнительной вычислительной маши- вы.

Целью изобретений является р д1ирение функциональных возможностей устройства|.

Поставленная цель достигается тем, что устройство дополнительно ooдepжйf дешифратор подтактов| обмена, блок приостанова j вспомогательной электронной вычислитель- ной машины, датчик периода обмена, буферный блок памяти и блок выбора контрольных слов, причем управлякчций выход вспомогвтельной электронной вычислительной iNtamaHbl соединен с первым входом дешифратора подтактов обмена, первый, второй и третий выходы которого соединенны соответственно со вторым входом блока режимов,, обмена, с входом бпока прерывания, с входом блока приостанова вспомогательной злек тронной вычиспитепьнсЛ машины, выход бпока приостанова соединен с управляющим входом вспомогательной электронной вычислительной машины, информационный выход регистра приема-выдачи информации соединен с входом блока выбора контрольныхслов,; управляющий вход которого соединен с выходом блока режимов обмена, информационный выход вспомогательной электронной рычислитйльной машины соединен с входом датчика периода обмена, выход которого Сое динен со вторым входом дешифратора подтактов обмена, третий информационный выход и вход регистра приема- выдачи информации соединены соответственно ;t G-информа ционным входом и выходом буферного блока памяти, управляющий вход которого соединен с выходом блока режимов обмена,

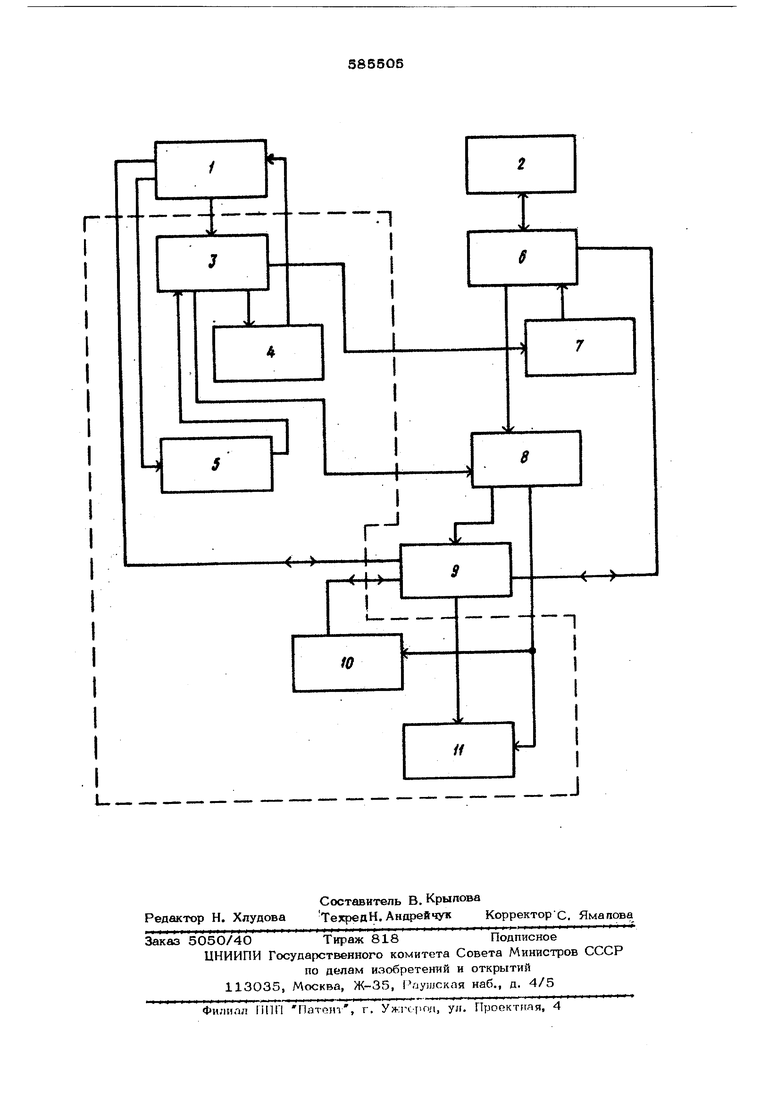

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство для сопряжения основной и вспомогательной вычислительных маши содержит вспомся:ательную электронную вычислительную машину (ВЭВМ) 1, основную-, электронную вычиспитеньную; машину (ОЭВМ 2, дешифратор подтактов обмена 3, блок приостанова 4 ВЭВМ, датчик 5 периода обме на, блок согласования 6, блок прерывания 7 OSBMJ блок режимов обмена 8, регистр 9 приема-выдачи информации, буферный блок памяти 10, блок выбора контрольных слов 11.

Работа предлагаемого устройства осушествляется следующим образом,

ВЭВМ 1 осуществляет ввод первичной информации и ее обработку в соответствии с заложенной .в ней программой. Обработка информации осуществляется циклами, каждый

из которых состоит из отдельных тактов, причем ввод и вывод информации кйк первичной, так и для ОЭВМ 2 осуществляется в подтактах каждого такта. В результате обработки инфбрмацйи;в оперативной памяти ОЭВ 2 формируется массив информации, передачзГ которого в ВЭВМ 1 обеспечивает предлагаемое устройство,

В дещифратор подтактов обмена 3 из ВЭВМ 1 поступает текущее значение двенадцатиразрядного кода. В блоке дешифратора подтактов обмена 3 происходит выделение и дешифрация определенных разрядов /этого кода,, кото|5ые представляют такты и подтакты ВЭВМ. i

Параллельно с выводом кода ВЭВМ 1 обеспечивает вывод в блок датчика периода обмена 5 текущего значения двадцатичетырехразрядного кода циклов работы. Блок 5 принимает код циклов и запоминает его. Разработанная заранее программа ОЭВМ 2J определяет необходимое время обработки информации, что ясвляется исходно информацией для выбора периода обмена между основной и вспомогательной вычислитеными машинами. При этом в зависимости от объема решаемых задач изменяется период,обмена информацией. Признак выбора одного из фиксированных периодов обмена информацией выбирается вручную с помощью ряда переключателей датчика периода обмена 5. Признак периода обмена поступает в схему формирования управляющего сигнала периода обмена блока 5, при этом осуществляется выделение цикла и его признака на временной оси отйосительно сигнала опорного генератора ВЭВМ 1, по истечении которого в работе устройства должна начаться подготовка и вывод информации в буферный блок памяти 10.

Сформированный в датчике периода обмена 5 импульс признака кода цикла поступает в дешифратор подтактов обмена 3, тем самы вырабатывая йа временной оси цикла такты, подтакты, в которых осуществляется вывод информации в буферный блок памяти 10, исходя из заранее разработанной стуктуры ввода-вывода.

Дешифратор : подтактов обмена 3 при получении исходной информации анализирует номера подтактов каждого такта и при поступлении подтактов вывода информации выдает в блок приостанова ВЭВМ 4 управляющие сигналы. Блок 4 принимает указанные сигналы и формирует сигналы признака непрограммированной команды (нк) приостановки ВЭВМ 1 и адресную часть ячейки опетивной памяти ВЭВМ 1, из которой должна быть списана информация. При формировании указанных сигналов сигнал адресной части несколько опережает сигнал признака НК так, что поступление признака НК является командой для съема информации с уже выбранной ячейки.. По поступлении очередного подтакта вывода информации блок щшостанова 4 ВЭВМ формирует повторна указанные выше сигналы, по которым описывается очередное информационное слово. Формируемые таким образом сигналы поступают в ВЭВМ 1 и при наличии признака НК прио танавливается вычислительной процесс ВЭБМ 1. Затем информационное слово выводится из ВЭВМ 1 и поступает в регистр приема-выдачи информации.. 9. Одновременно с формированием сигналов i для ВЭВМ 1 в дешифраторе подтактов обмена 3 формируются управляющие сигналы для блока реж мов обмена 8, тем самым определяя режим его работы, т.е. считывание информации с ВЭВМ 1 и ее запись уЭ буферный блок памяти 1О. Блок режимов обмена 8 формирует перво начально сигнал обнуления регистра приемавыдачи информации 9, а затем сигнал записи, который совпадает со временем появлени я сигналов кода на выходах регистра приема-выдачи информации 9, осуществляя запись информационного слова в регистр приема-выдачи информации одновременно с формированием управляющих сигналов для записи. В блоке режимов обмена 8 формиру ся управляющие сигналы для блоков 10 и . 11. Указанные сигналы поступают в буферный блок памяти 10 и устанавливают его в исходное состояние. Сигнал, снимаемый с блока 1О, является адресом ячейки памяти МОЗУ. Указанный сигнал подготавливает ячейку для переписывания информации с регистра приема-выдачи информации 9 в бло 10. Буферный блок памяти 10 осуществляет перепись информации с регистра приема-выд чи информации 9 во внутреннюю память блока 10. При записи последнего слова в буферный блок памяти 10 дешифратор подтактов обмена 3 формирует и выдает; в блок прерывания 7 ОЭВМ признак окончания вывода информации из ВЭВМ 1 в блок 10 При этом блок прерывания 7 ОЭВМ выра:батывает сигнал прерывания программы ОЭВМ 2. Указанный ( поступает в бло согласования 6, где преобразуется по ампли туде и полярности, пригодной для управлени ОЭВМ 2. Преобразованный сигнал поступает Ъ ОЭВМ 2, что является командой для прерывания программы ОЭВМ. По этому сигналу ОЭВМ 2 передает упр ление на чтение информации из блока 10. При этом выраба1Ъ1ваются сначала подгото вительная комауда, а затй.м исполнительная Чтение, импульсы которых посредством блока 6 поступают в блок режимов обмена 8, меняя его режим работы. Вырабатываемые в блоке 8 сигналы поступают в блок 10, обнуляют его. Блок режимов обмена 8 вырабатывает также сигнал обнуления регистра приемавыдачи информации 9, подготавливая его к приему информационного слова из блока 1О. При формировании блоком 10 импульса обращения осуществляется списывание информации из ячейки памяти и запись ее по сигналу блока 8 в регистр приема-выдачи информации 9. Управляющие импульсы исполнительной команды ОЭВМ 2 списывают информацию с регистра приема-выдачи информации 9. Импульсы информации поступают в блок согласования 6, масштабируются, а затем поступают в регистр ОЭВМ 2. При выработке очередной исполнительной команды в ОЭВМ 2 - осуществляется очередное описывание аналогичным образом. По окончании считывания информационных слов из блока 10 и запись их в память ОЭВМ 2 сбрасывается триггер Чтение в блоке режимов обмена 8, переводит режим работы блока 8 на запись информации из ОЭВМ 2 в блок 10. Чтение информации при этом осуществляется по управляющим сигналам подготовительной и исполнительной команд, вырабатываемых в ОЭВМ 2. После записи информации из ОЭВМ 2 в блок 10 осуществляется запись ее в память ВЭВМ 1. При этом выработка управляющих сигналов осуществляется устройствами описанным выше образом. В целях анализа или контроля обменных | управляющих слов блок 8 формирует управляющие сигналы, привязанные к сигналу опорно;го генератора ВЭВМ 1, которые поступают в блок выбора контрольных слов 11. При приемесигнапов схема управления блока 11 формирует строб разрешения приема информации из блока 9 в блок 11. Запись информации осуществляется по управляющим сигналам блока 8. При записи любого иэ информаЬибЭНых слов в блоки 9 и 11 счетчик номера слов схемы управления бл9ка 11 подсчитывает номера обменных слов по сигналам блока 8, анализируется код номера обменного слова п при совпадении текущего кода номера слова с кодом, набранным с помощью ;наборного поля, обры - вает строб, тем самым фиксируя в контрольном регистре значения обменного слова. Зафиксированная информация в контрольном регистре поступает на схему индикации блока 11. Включение в состав предлагаемого устройства блока п11ИОстаноБа БЭВМ, датчика периода обмена, дешифратора подтактпв, блока выбора кпнтрольных слов и буферног-о блока памяти, шх-.шплшю построить уг-т11Г1Йптво для сопряжения и вспомогательной вычислительных машин, при этом сокр. тить машинное время какЪсновной, так и вспомогательной вычислительных машин, зат рачиваемое на обмен информапией, поэваляет непосредственно контролировать любое ел , во передаваемой информации. Формула изобретения Устройство для сопряжения основной и всоомогательнoft вычислительных машин, солержашее блок прерывания основной машины блок режимов обмена, блок согласования я регистр приема-выдачи информации, причем вход и выхоа основной электронной-вычисли тельной машины соединены соответственно с первым выходом и входом блока согласова вея. второй выход блока согласования соеакнен с первым входом блока режимов обмена, выход которого соединен с управляюшнм входом регистра приема-вьшачи информапвн, информационные выходы и входы регистра приема-вьшачи информации соединены соогветствечно i с информационными входом и выхоа6ь4 вспомогательной электронной вычислительной машины и с информационным входом и выходом блока согласования, а выход блока прерывания соединен со вторым входом блока согласования, отличаюш е е с я тем, что, с йелью расширения .функциональных возможностей, оно дополните но содержит дешифратор подтактрв обмена, .блок приостанова вспомогательной электронной вычислительной машины, датчик периода обмена, буферный блок памяти и блок выбора контрольных слов, причем управляющий выход вспомогательной электронной вычислительной машины соединен с первым входом дешифратора подтактов обмена, первый, второй и третий выходы которого соединены соответственно со вторым входом блока режимов обмена, с входом блока прерывания, с входом блока приостанова вспомогательной электронной вычислительной машины, выход блока приостанова соединен с управляюшим входом вспомогательной электронной вычислительной машины, информационной выход регистра приема-выдачи информации соединен с входом блока выбора контрольных слов, управл$поший вход которого соединен с .выходом блока режимов обмена, информационный выход вспомогательной электронной вычислительной машины соединен с входом датчика периода обмена, выход которого соединен :со вторым .входом дешифратора подтактов обмена, третий информационный выход и вход регистра приема-вьшачи информации соединены соответственно с информационным входом и выходом буферного блока памяти, управляюШни вход которого соединен с выходом блока режимов. обмена. Источники информации, принятые во внимание -при экспертизе: 1. Авторское свидетельство СССР № 235596, кл. С Об F 15/16, 1956, 2. Авторское свидетельство СССР N9 437О75, кл. С Об Р 15/16, 1971,

н

ч-)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительных групп, состоящих из основной и вспомогательных ЭВМ | 1991 |

|

SU1783532A1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2011 |

|

RU2444052C1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для обмена информацией между персональной ЭВМ и управляющим вычислительным комплексом | 1991 |

|

SU1838819A3 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Устройство для обмена информацией между внешними устройствами и основной памятью электронной вычислительной машины | 1972 |

|

SU455345A1 |

I;

Авторы

Даты

1977-12-25—Публикация

1975-06-04—Подача