1

Изобретение относится к области вычислительной техники и, в частности, к устройствам для управления потоком информации между внешними устройствами и основиой памятью вычислительной машины.

Известно устройство для обмена информацией между внешними устройствами и основной памятью электронной вычислительной машины, содержаш,ее блок памяти, соединенный двусторонними связями с входами-выходами устройства, регистры записи и чтения с адресной и первой числовой частью, узел модификации и дешифратор, причем выход разрядов первой числовой части регистра чтения соединен через дешифратор с первым выходом устройства, а через узел модификации - с входами разрядов первой числовой части регистра записи.

Цель изобретения - повышение быстродействия устройства и обеспечение одновременного использования одной и той зоны блока памяти для приема и выдачи информации.

Это достигается тем, что устройство имеет в регистрах записи и чтения вторые числовые части, второй дешифратор, второй и третий узлы модификации. Выход разрядов второй числовой части регистра чтения соединен с входом второго дешифратора и одним входом второго узла модификации, другой

вход второго узла - с первым входом третьего узла модификации и с первым выходом второго дешифратора.

Второй выход второго дешифратора связан с вторым выходом устройства, а его третий выход - с вторым входом третьего узла модификации, третий вход которого соединен с соответствуюшим входом блока памяти и выходами разрядов адресной части регистра чтения. Выходы второго и третьего узлов модификации подключены к входам соответственно разрядов адресной и второй числовой части регистра записи.

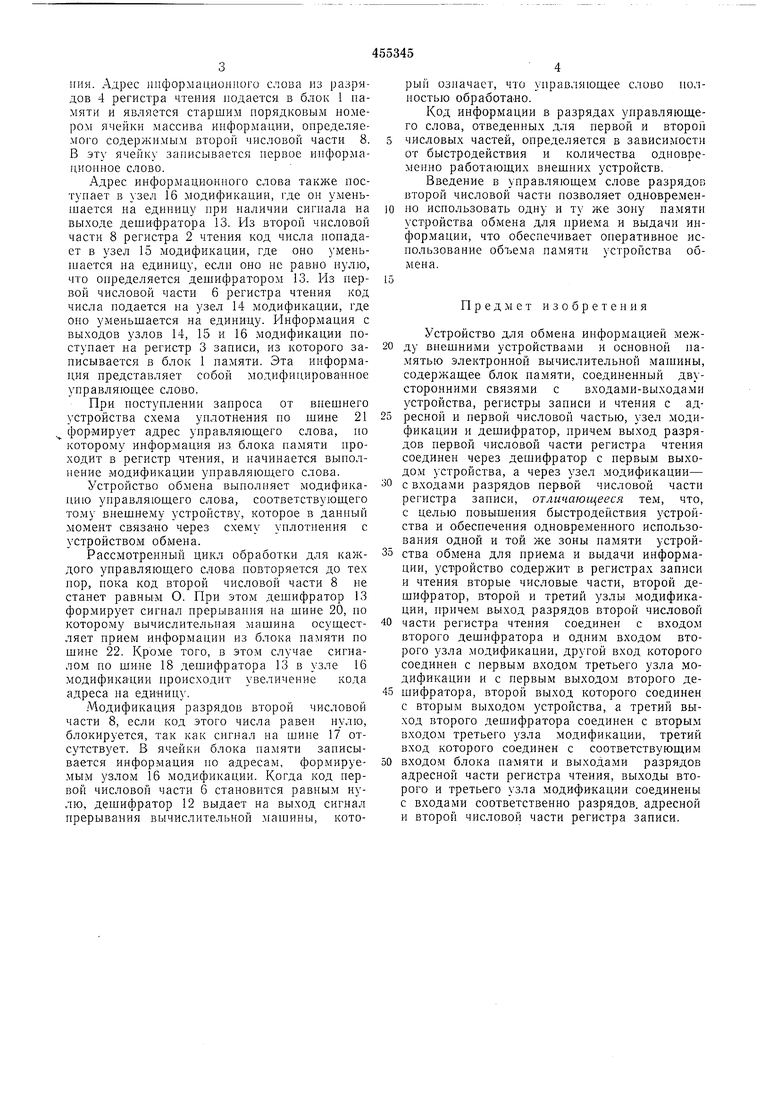

Блок-схема устройства представлена на чертеже.

Устройство обмена содержит блок 1 памяти, регистры чтения 2 и записи 3, адресные части 4 и 5, первые 6 и 7 и вторые 8 и 9 числовые части, разряды 10 и II признаков, дешифраторы 12 и 13, узлы 14, 15 и 16 модификации, шины 17-22.

Код в первой числовой части 6 указывает количество слов обмена, а код во второй части 8 - количество ячеек в блоке 1 памяти. необходимое для поступающей информации.

Устройство работает следующим образом.

При поступлении по шине 22 из основной

памяти ЭВМ заправляющего слова, оно выдается устройством обмена в регистр 2 чтеПИЯ. Адрес информационного с.чова из разрядов 4 регистра чтения иодается в блок 1 иамяти и является старшим порядковым номером ячейки массива информации, определяемого содержимым второй числовой части 8. В эту ячейку записывается первое информациоиное слово. Адрес информационного слова также поступает в узел 16 модификации, где он уменьгиается на единицу при наличии сигнала на выходе дешифратора 13. Из второй числовой части 8 регистра 2 чтения код числа попадает в узел 15 модификации, где оно уменьшается па единицу, если оно не равно нулю, что онределяется дешифратором 13. Из нервой числовой части 6 регистра чтения код числа нодается на узел 14 модификации, где оно уменьшается па единицу. Информация с выходов узлов 14, 15 и 16 модификации поступает на регистр 3 записи, из которого записывается в блок 1 памяти. Эта информация представляет собой модифицироваипое управляющее слово. При поступлении запроса от внешнего устройства схема уплотнения по шине 21 формирует адрес управляющего слова, цо которому информация из блока памяти проходит в регистр чтения, и начинается вынолнение модификации управляюп его слова. Устройство обмена выполняет модификацию управляющего слова, соответствующего тому внешнему устройству, которое в данный .момент связано через схему уплотнения с устройством обмена. Рассмотренный цикл обработки для каждого управляющего слова повторяется до тех пор, пока код второй числовой части 8 не станет равным О. Ири этом дешифратор 13 формирует сигнал прерывания на шине 20, по которому вычислительпая машина осущестляет прием информации из блока памяти но шине 22. Кроме того, в этом случае сигналом по шине 18 дешифратора 13 в узле 16 модификации происходит увеличение кода адреса па единицу. Модификация разрядов второй числовой части 8, если код этого числа равен пулю, блокируется, так как сигнал на шине 17 отсутствует. В ячейки блока памяти записывается информация но адресам, формируемым узлом 16 модификации. Когда код первой числовой части 6 становится равным нулю, дешифратор 12 выдает на выход сигнал прерывания вычислительной машины, который означает, что управ.чяющее слово полностью обработано. Код информации в разрядах управляющего слова, отведенных для первой и второй числовых частей, определяется в зависимости от быстродействия и количества одновременно работающих внешних устройств. Введение в управляющем слове разрядов второй числовой части позволяет одновременно иснользовать одну и ту же зону памяти устройства обмена для приема и выдачи информации, что обеспечивает оперативное исиользовапие объема памяти устройства обмена. Предмет изобретения Устройство для обмена информацией между внешними устройствами и основной памятью электронной вычислительной машины, содержащее блок памяти, соединенный двусторонними связями с входами-выходами устройства, регистры записи и чтения с адресной и первой числовой частью, узел модификации и дешифратор, причем выход разрядов первой числовой части регистра чтения соединен через дешифратор с первым выходом устройства, а через узел модификации- с входами разрядов первой числовой части регистра записи, отличающееся тем, что, с целью повышения быстродействия устройства и обеспечения одновременного использования одной и той же зоны памяти устройства обмена для приема и выдачи информации, устройство содержит в регистрах записи и чтения вторые числовые части, второй дешифратор, второй и третий узлы модификации, причем выход разрядов второй числовой части регистра чтепия соединен с входом второго дешифратора и одним входом второго узла модификации, другой вход которого соединен с первым входом третьего узла модификации и с первым выходом второго дешифратора, второй выход которого соединен с вторым выходом устройства, а третий выход второго дешифратора соединен с вторым входом третьего узла модификации, третий вход которого соединен с соответствующим входом блока пз.мяти и выходами разрядов адресной части регистра чтения, выходы второго и третьего узла модификации соединены с входами соответственно разрядов, адресной и второй числовой части регистра записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля ввода-вывода | 1980 |

|

SU896626A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Устройство для объема информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1679497A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для обмена информацией | 1977 |

|

SU734655A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

Авторы

Даты

1974-12-30—Публикация

1972-06-28—Подача