(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел безВОССТАНОВлЕНия OCTATKA | 1979 |

|

SU817706A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

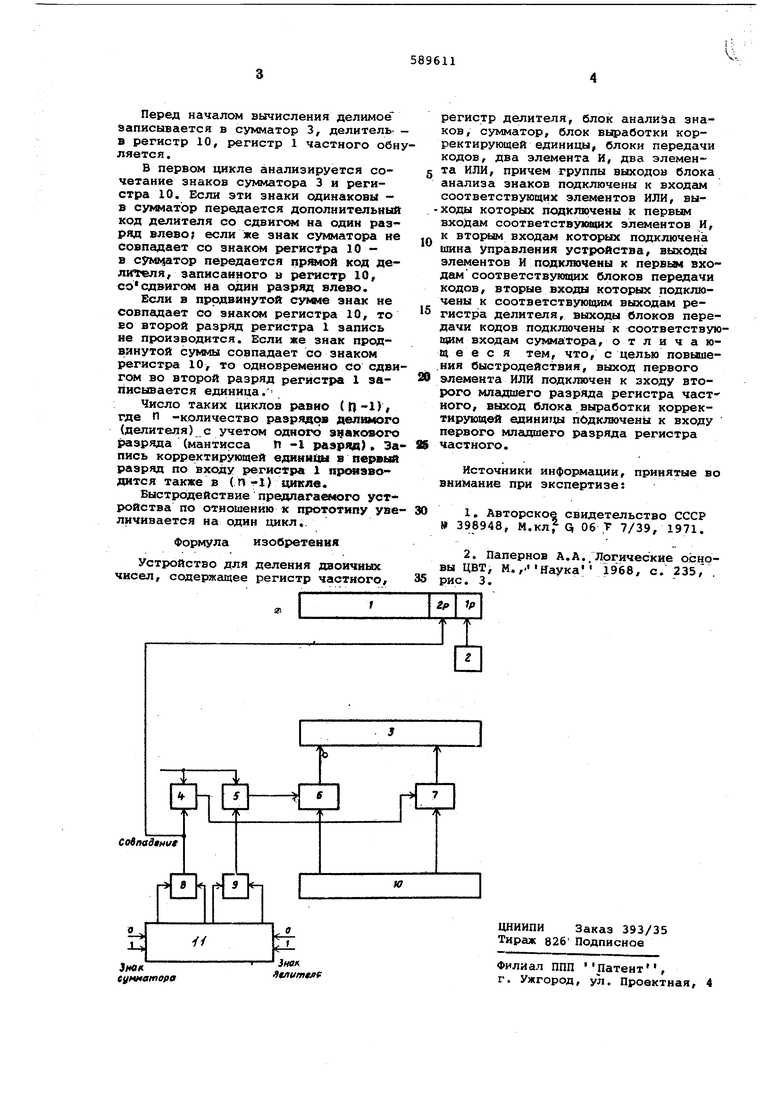

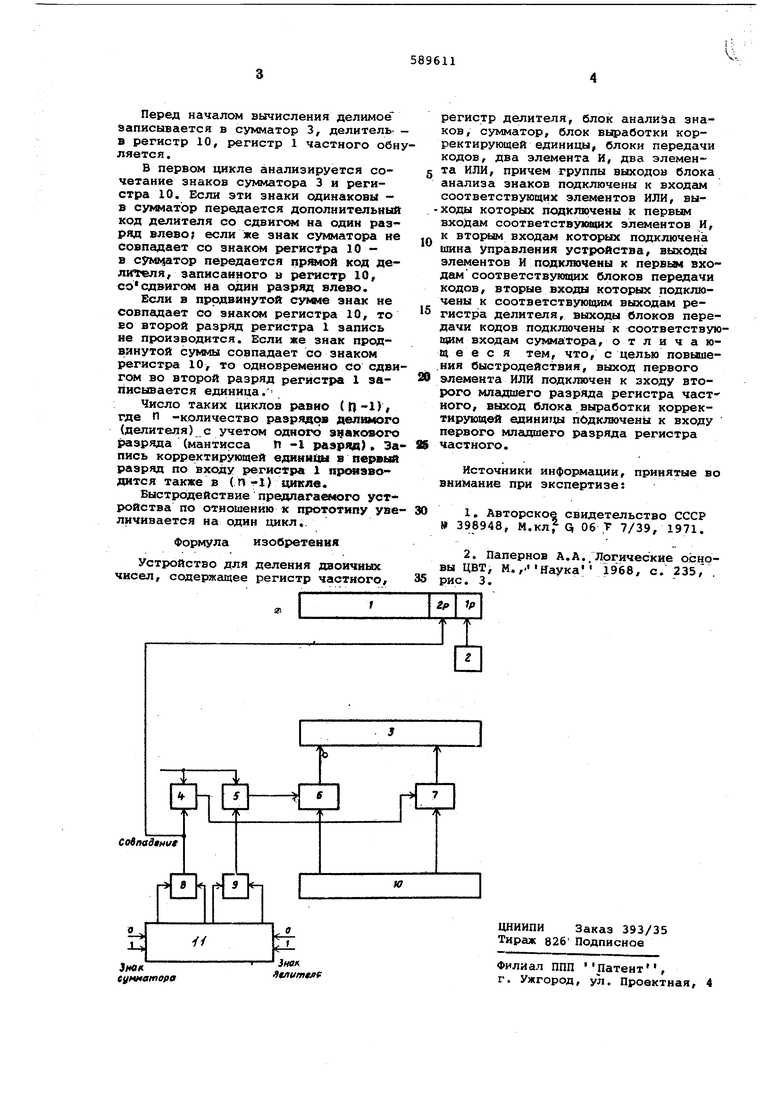

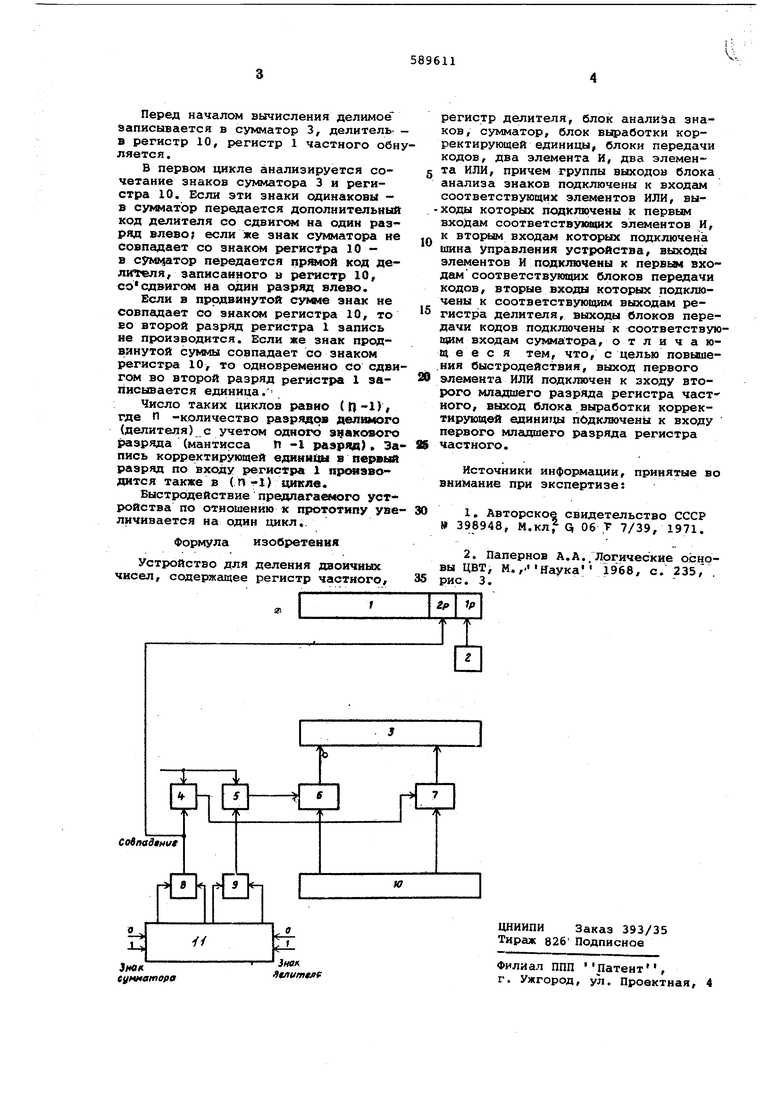

Изобретение предназначено для выполнения операции деления и может широкое применение в цифровых вычислительных машинах. Известно устройство для деления двоичных чисел, содержащее регистр частного, регистр делителя и сумматор l . В таких устройствах за каждый цикл определяется одна цифра частного и запись последней производится в первый разряд регистра частного Наиболее близким к изобретению техническим решением является устройство для деления двоичных чисел, содержащее регистр д«лителя, регистр частного, блок анализа знаков, сумматор, блок выработки корректирующей единицы, блоки передачи кодов, два элемента И, два элемента ИЛИ, прИ чем группы выходов блока анализа зна ков подключены к входам соответствую щих элементов ИЛИ, выходы которых подключены к первьм входам соответст вующих элементов И, к вторым входам которых подключена шина управления устройства, выходы элементов И подключены к первьш входам соответствую щих блоков передачи кодов, вторые вх ды которых подключены к соответствую щим выходам регистра делителя, выходы блоков передачу кодов подключены к соответствующим входам сумматора 2j. В этом устройстве запись единицы частного производится в первый разряд. После окончания (П -1) циклов, в каждом КЗ которых Определяется одна цифра частного, необходимо потратить еще один цикл на сдвиг информации в регистре частного на один разряд влево. И только тогда в младший разряд возможна запись корректирующей единихш. Цель изобретения - повышение быстродействия устройства.Достигается это тем, что выход первого элемента ИЛИ подключен к входу второго младшего разряда регистра частного/ выход блока выработки корректирующей единицы подключен к входу первого младшего разряда регистра частного. На чертеже приведено устройство для деления двоичных чисел без восстановления остатка. Устройство содержит регистр 1 частного, блок 2 выработки корректирующе единицы, суг«1атор 3, два элемента И 4, 5, блоки б и 7 передачи ко,ов, два элемента ИЛИ 8, 9, регистр 10 делителя, блок 11 анализа знаков. Перед началом вьлчисления делимое записывается в сумматор 3, делитель в регистр 10, регистр 1 частного обн ляется. В первом цикле анализируется сочетание знаков сумматора 3 и регистра 10. Бели эти знаки одинаковы в сумматор передается дополнительный код делителя со сдвигом на один разряд влево; если же знак сумматора не совпадает со знаком регистра 10 - в cSnvttjaTop передается прялой код делкгтеля, записанного в регистр 10, сосдаигсм на один разр|зд влево. Вели в продвинутой сумме знак не совпадает со знаком регистра 10, то во второй разряд регистра 1 запись не производится. Вели же знак продвинутой суммы совпадает со знаком регистра 10, то одновременно со сдви гом во второй разряд регистра 1 записывается единица. Число таких циклов равно ( где п -количество разрядов делимого (делителя) с учетом одного знакового разряда (мантисса П -1 раэряЕд). За пись корректирующей единн1ш в nepBbtft разряд по входу регистра 1 пршоводнтся также в (И-1) цикле. Быстродействие предлагаемого усТ ройства по отношению к прототипу уве личивается на один цикл,. Формула изобретения Устройство для деления дзоичиых чисел, содержащее регистр частного. регистр делителя, блок анализа знаков, сумматор, блок выработки корректирующей единицы, блоки передачи кодов, два элемента И, два элемента ИЛИ, причем группы выходов блока анализа знаков подключены к входам соответствующих элементов ИЛИ, выходы которых подключены к первым вхоДсш соответствук ф1х элементов И, к втор«Ф4 входам которых подключена шина управления устройства, выходы элементов И подключены к первьм входам соответствующих блоков передачи кодов, вторые входы которых подключены к соответствуюощм выходам регистра делителя, выходы блоков передачи кодов подключены к соответствующим входам сумматора, отличающее с я тем, что, с целью повьапе.ния быстродействия, выход первого элемента ИЛИ подключен к зходу второго младшего разряда регистра част ного, выход блока выработки корректирующей единитда подключены к входу первого мпалщ его разряда регистра частного. Источники информации, принятые во внимание при экспертизе: 1, Авторское свидетельство СССР 398948, М.кл Q 06 Г 7/39, 1971. 2. Папернов А.А. Логические основы ЦВТ, М., Наука 1968, с. 235; рис. 3.

Авторы

Даты

1978-01-25—Публикация

1974-08-05—Подача