(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Устройство для деления | 1984 |

|

SU1242935A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления | 1983 |

|

SU1164698A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Устройство для деления двоичных чисел | 1981 |

|

SU1008733A1 |

| Делительное устройство | 1982 |

|

SU1104508A1 |

Изобретение относится к области вьгчиспитепьной техники и может быть испопьзовамо в процессорах быстродействующих ЦВМ

Известны устройства для деления чисел в системе счисления 1 ), испопьзукшие регистры хранения чисеп, кратных делителю fl.

Наиболее близкимк изобретению по технической сущности $ вляется устройство, содержащее регистры хранения кратных делите лю, сумматор-вычитатепь, блок сдвига, буферный регистр, регистр частного и блок управпения, первый -и второй выходы которого соединены с первым и вторым управляющим входами регистров хранения кратных делителю, третий и четвертый выходы блока управления соединены с первой и второй управляющими шинами сумматора-вьгчитателя, пятый выход блока управпения подключен к щине сдвига регистра частного, щесто выход блока управления подключен к щине сдвига блока сшзига, выход сумматора-вы- читателя соединен с буферным регистром, а выходы регистров хранения кратных делителю объединены l . Недостатками устройства являются большой объем оборудования и низкое быстродействие.

Целью изобретения является повышение быстродействия и упрощение устройства.

Цепь достигается тем, что в предлагаемом устройстве выход регистров хранения кратных делителю соединен с первым входом сумматора-вычитатепя, а выход блока сдвига соединен со вторым входом сумматора-вычитатепя, выходом регистра частного и со входом регистров хранения кратных делителюутвыход знакового разряда буферного регистра соединен со входом блока управления, а вход младщего разряда регистра частного подключен к седьмому выходу блока управления.

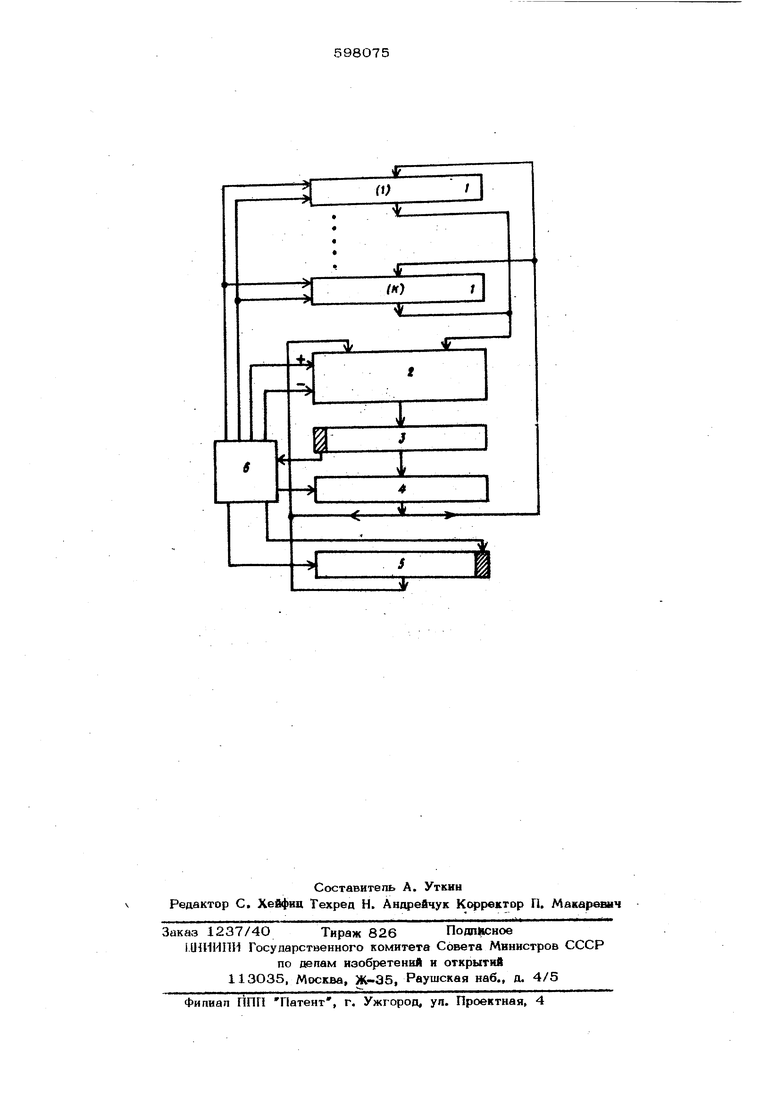

На чертеже представлена бпок-схема устройства для деления.

Устройство содержит k регистров 1 хранения кратных делителю, имеющие цепи приема и выдачи чисел, комбинационный нараппепьный сумматор-вычитатепь 2, буферный регистр 3, блок сдвига 4, регистр S частного и блок управления 6. Регистры 3 и 5 снабжены цепями приема н выдачи кода, а сумматор имеет управляющие шины сложение и вычитания. Работает устройство с -едующим образом, Депнтепь поступает одновременно в первый регистр 1 и регистр 3. Делимое посту пает.в регистр 5 Лапее производится вычисление кратных дегштепю, для чего содержимое первого в других 1эегистров 1 подается в сумматор-вцчитатепь 2 и аапасывается в очередной регистр 1 кратного. При этом вычисляются кратные дейителю, отвечающие рекуррентному соотношению;. Е %1/2-«.5) где Е -целевая часть чВспа, а i принимает значение-от О до k -1« а ff аоа.т)И РИ tn, не равном степени числа 2: при 10 равном степени числа 2: причем v« wКратные щ записываются в соответст вующие их кратности регистры 1. Далее производится невосредствевно делеиие. Дпя примера рассмотрим попучение цифры частн го при оепении чисел, представпевных в восьмеричной системе счисления (1 из 8). В этом случае иеобходнмо вычислить кра-гные делителю: и (D делитель). В первой итерации производится вычитание 4D из остатка, храняшегося в регистре 3 (нпи из делимого, храняцегося в регистре 5, для первой частного). При этом остаток передается из регистра 3 через блок 4 со СДВИГОМ влево на одни 8-ичный разряд, а результат вычитания поступает в регистр 3 с задержкой суммирования. Знак остатка поступает в блок управления 6, где запоминается. Во второй итерации производится сложение или вычита ние 2D нз остатка в зависимости от его знака, для чего остаток передается из регистра 3 через блок 4 без сдвига в сумматор 2. Знак остатка поступает в блок управ ления 6, где также запоминается. В третьей ите рации производится сложение или вычитание из остатка в зависимости от его знака для чего он передается иа регистра 3через лок 4 и без сдвига в сумматор. Знак остата поступает в блок управпяния 6, где форируется код очередной 8-ичной цифры частого в соответствии со знаками трех остатов. Цифра частного поступает в регистр 5, одержимое которого далее сдвигается влео на один 8-ичный разряд. Процесс продолжается до получения всех цифр частного. Ф о р мула изобретения Устройство для деления, содержащее регистры хранения кратных делителю, сумматор вычитатепь, блок сдвига, буферный регистр, регистр частного и блок управления первый и второй выходы которого сое дине-; ны с первым и вторым управляющими входами регистров хранения кратных делителю третий и четвертый выходы блока управления соединены с первой и второй ynpaBnsnoщимн шинами сумматора вычитателя, пяты выхрд блока управления соединен ti шиной сдвига регистра частного, шестой выход блока управления подключен к шине сдвига блока сдвига, выход сумматора-вычитателя соегднен с буферным регистром, а вькоды регистров хранения кратных делитеniO объединены, о т я в ч.а ю 1Ц-е е с я тем, что, с целью повьние1аия.)одействия и упрощения yclrpt ftcT&a)3feixoji( регистров храиен ия:кратнш::5Йп11тедю соединен с первым входом; cзf ймatQpйr-вьгштaтeпя,a выход блока сдэир а1;;(:1.6еданей со вторш входом cyMMdfbpa вычитателя, 1}ыходом регистра частного и со входом регистров хранения кратных делителю, выход знакового разряда буферного регистра соединен со входом блока управления а вход младшего разряда регистра частного подключен к седьмсж у выходу блока управления. Источники информации, принятые во вн мание при экспертизе 1.Карцев М. А. Арифметика цифровых. машин . М,, 1969. 2.Патент США № 3.578.961, кп. 235-159. 1971.

Авторы

Даты

1978-03-15—Публикация

1976-02-16—Подача