(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА УПРАВЛЕНИЯ МИКРОПРОГРА.МЛШОГО

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1115054A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1667068A1 |

| Устройство управления микропрограм-МНыМи пЕРЕХОдАМи | 1979 |

|

SU813428A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1164706A1 |

Изобретение относится к области цифровой вычислительной техники.

Известно устройство для контроля блоков микропрограммного управления цифровой вычислительной машины, содержащее регистр команд, регистр адресов микрокоманд, дешифратор адресов микрокоманд, блок памяти микрокоманд, регистр микрокоманд и дешифратор микрокоманд, которое обеспечивает проверку правильности считывания из блока памяти адреса следующей микрокоманды 1.

Недостатком этого устройства является то, что оно не осуществляет проверку работы при выполнении команд ветвления («условный переход или «безусловный переход).

Наиболее близким техническим решением к данному изобретению является устройство для контроля блока микропрограммного управления, содержащее регистр команд, регистр адресов микрокоманд, дешифратор адресов микроко.манд, счетчик микрошагов, блок памяти микрокоманд, регистр микрокоманд, дешифратор микрокоманд, причем входом устройства является вход регистра команд, выход которого соединен с первым входом регистра адреса микрокоманд, первый -выход регистра адреодмикрокоманд через дешифратор адреса микрокоманд и блок памяти микрокоманд соединен со

входом регистра микрокоманд, первый выход которого соединен со вторым входом регистра адреса микрокоманд, а второй выход регистра микрокоманд соединен со входом дешифратора микрокоманд 2.

Недостатком этого устройства является то, что для контроля переходов используются две команды, которые добавляются в программу вычислений. Введение в программу двух избыточных команд для организации контроля снижает быстродействие работы устройства, что особенно неэффективно при работе в реальном масштабе времени.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в предлагаемое устройство введены блок разрещения контроля, дешифратор микрощагов. регистр контрольной микрокоманды, формирователь признаков, формирователь адреса контрольной микрокоманды, блок памяти контрольных микрокоманд, блок выработки ошибки ветвления, причем выход дешифратора микрокоманд соединен с первым входом формирователя адреса контрольной микрокоманды и со входом формирователя признаков, выход которого соединен со вторым входом формирователя адреса контрольной микрокоманды, выход формирователя адреса контрольной микрокоманды через блок памяти контрольных микрокоманд соединен со входами счетчика микронтгов н регистра контрольной микрокоманды, выход которого соединен с первым входом блока выработки ошибки ветвления, выход счетчика микрошагов через дeнJифpaтop микрошагов соединен с первым входом б.юка разрешения контроля, второй вход которого сосдинеп со входом устройства, а выход соединен со вторым вход(хм блока выработки ошибки ветвления, rvropofi выход реги.стра адреса микрокоманд соединен с третьим входом формирователя адреса контрольной микрокоманды, второй выход регистра микрокоманд соединен с третьим входом блока выработки ошибки ветвления, ,1 которого является выходом устройства.

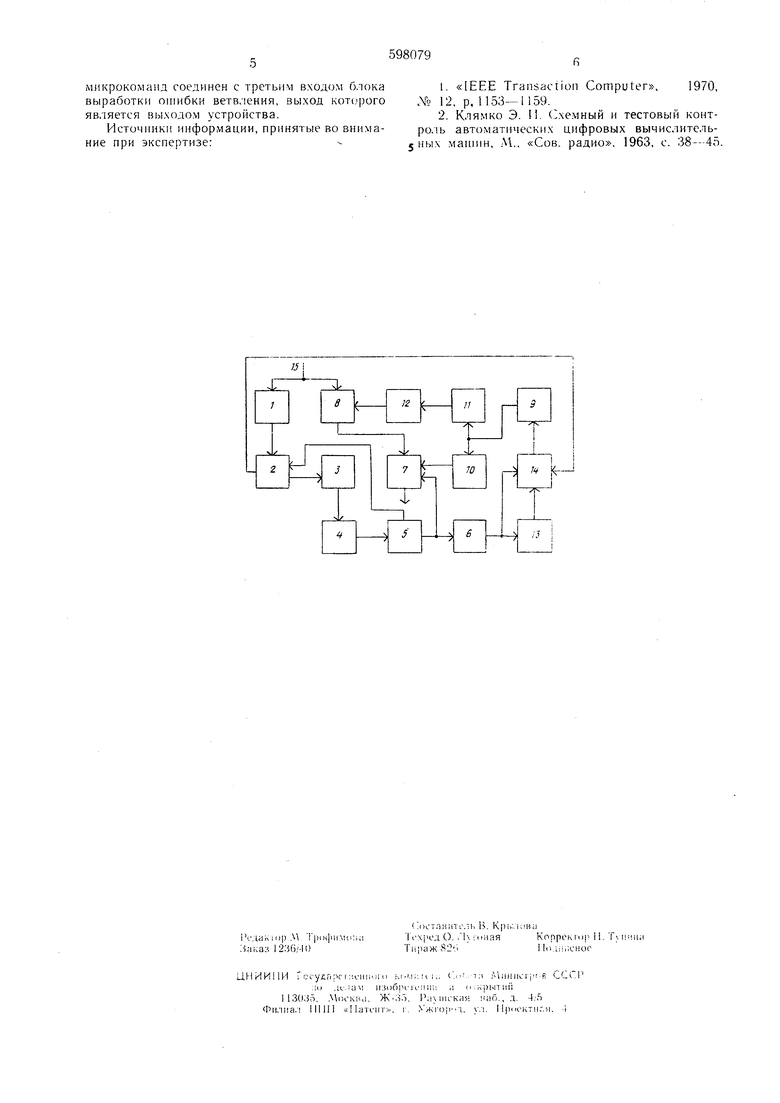

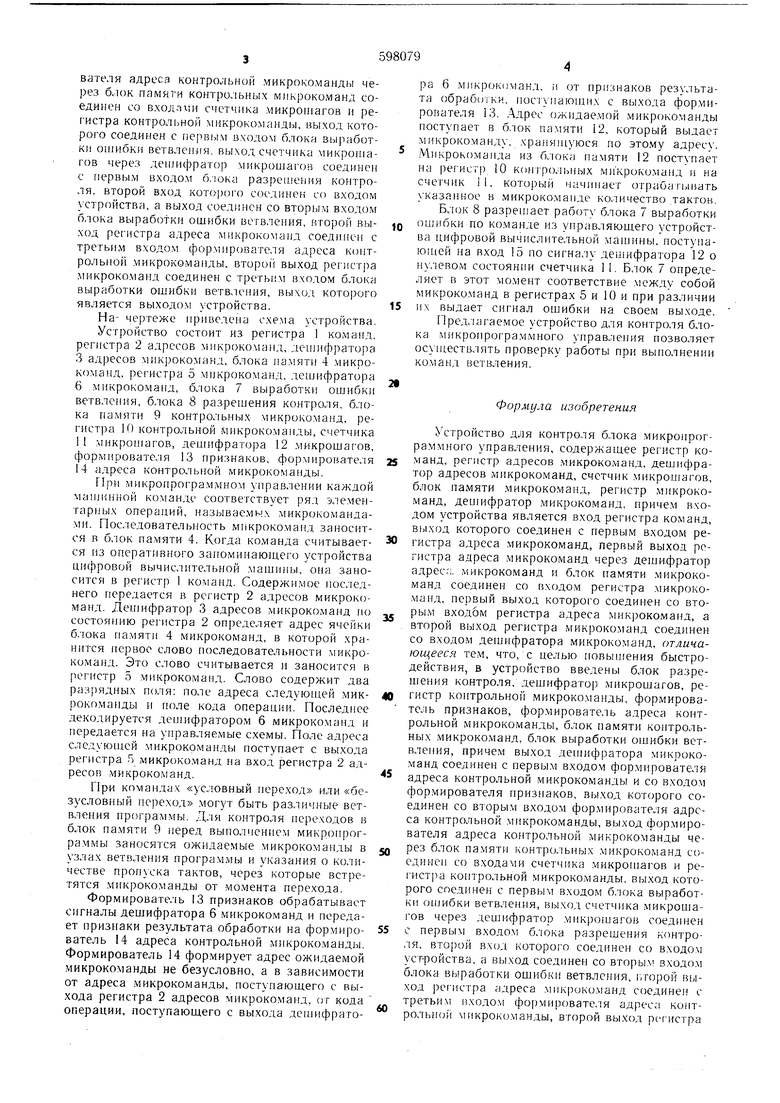

На- чертеже нриведена схема устройства.

Устройство состоит из регистра I команд, регистра 2 адресов микрокоманд, деи1ифратора 3 адресов мик)око.манд, блока памяти 4 .микрокоманд, регистра 5 микрокоманд, .1е пифратора 6 микрокоманд, блока 7 выработки ошибки ветвле 1ия, блока 8 разрешения контроля, блока памяти 9 контрольных микрокома1{д, регистра J О контрольной микроко.мапды, счетчика 1 1 микрогнагов, дешифратора 12 .микрошагов, формировате.чя 13 признаков, формирователя 14 адреса контрольной микрокоманды.

При микропрограммном управлении каждой ман инной команде соответствует ряд элементарных операций, называемых микрокомапда.ми. Пос,тедовательность микроко.манд заносится в блок памяти 4. Когда команда считывается из оперативного заноминающего устройства цифровой вычие.1 1тельной машины, она заносится в регистр 1 команд. Содержимое носледнего передается в регистр 2 адресов микрокоманд. Деп ифратор 3 адресов микрокоманд но состоянию peiHCTpa 2 определяет адрес ячейки б.шка памятп 4 микрокоманд, в которой хранится первое слово последовательности микрокоманд. Это слово считывается и заносится в региетр 5 микрокоманд. Слово содержит два раз)ядных поля: поле адреса следующей микрокоманды и ноле кода операции. Последнее декодируется депшфратором 6 микрокоманд и передается на управляемые схе.мы. Поле адреса следуюптей .микрокоманды поступает с выхода регистра 5 микроко.манд на вход регистра 2 адpecoFs микрокоманд.

При командах «условный переход или «безусловный переход могут быть различные ветвления нрограммы. Для контроля переходов в блок па.мяти 9 перед выполнением микропрограммы заносятся ожидаемые микрокоманды в узлах ветвления программы и указания о количестве пропуска тактов, через которые встретятся .микроко.манды от мо.мента перехода.

Формироватеть 13 признаков обрабатывает сигналы дешифратора 6 микрокоманд и передает признаки результата обработки на формирователь 14 адреса контрольной микрокоманды. Формирователь 14 фор.мирует адрес ожидаемой микрокоманды не безусловно, а в зависимости от адреса .микрокоманды, поступающего с выхода регистра 2 адресов микроко.манд, от кода операции, поступающего с выхода деп|ифратора 6 микрокоманд, и от признаков результата обрабспки, ностунающих с выхода формирователя 13. .Адрес ожидае.мой микрокоманды поступает в блок памяти 12, который выдает микрокоманду, храняп1уюся по этому адресу. Микрокоманда из б.тока памяти 12 поступает им регистр 10 контрольных микрокомапд и на счетчик И, который начинает отрабагьп)ать чказанное в .микроко.маиде количество тактов.

Блок 8 разрен.ает работу блока 7 выработки ошибки по ко.манде из управляющего устройства цифровой вычислительной машины, поступающей на вход 15 по сигналу деишфратора 12 о пу,1евом состоянии счетчика 1 1. Блок 7 определяет в этот мо.мент соответствие .между собой .микроко.манд в регистрах 5 и 10 и при различии их выдает сигнал ошибки на своем выходе.

Пред.чагаемое устройство для контро,1я блока микропрогра.ммного управления позволяет осуществлять проверку работы при выполнении команд ветвления.

Формула изобретения.

Устройство для контроля блока микропрограммного управления, содержащее регистр ко.манд, регистр адресов .микрокоманд, дешифратор адресов микрокоманд, счетчик микропгагов, блок памяти .микроко.манд, регистр микрокоманд, дешифратор .микрокоманд, причем входом устройства является вход регистра команд, выход которого соединен с первым входом регистра адреса микрокоманд, первый выход регистра адреса микрокоманд через дешифратор адрес.;, .микрокоманд и блок памяти микрокоманд соединен со входом регистра микроко.манд, первый выход которого соединен со вторым входбм регистра адреса п-1крокоманд, а второй выход регистра микрокоманд соединен со входом дещифратора микрокоманд, отличающееся тем, что, с целью гговьинения быстродействия, в устройство введены блок разрешения контроля, дещифратор микрошагов, регистр контрольной .микрокоманды, формирователь признаков, фор.мирователь адреса контрольной микрокоманды, блок памяти контрольных микрокоманд, блок выработки ощибки ветв,тепия, причем выход деп1ифратора .микрокоманд соединен с первым входом формирователя адреса контрольной микрокоманды и со входом фор.мирователя признаков, выход которого соединен со вторы.м входо.м формирователя адреса контрольной .микрокоманды, выход фор.мирователя адреса контрольной микрокоманды через блок па.мяти контрольных .микрокоманд соСлТинеи ео входами счетчика .микрошагов и регист11а коитрольной .микрокоманды, выход которого соединен с первым входом блока выработки о1.пибки ветвления, выход счетчика .микрошагов через дешифратор .микрошагов соединен с первым входом блока разрешения контро:1Я, второй вх(;д которого соединен со входом усг-ройства, а выход соединен со вторым входом блока выработки ошибки ветвления, г/горой выход регистра адреса .микрокоманд соединен с третьим входом формирователя адреса контрольн(.)й микроко.манды, второй выход регистра микрокоманд соединен с третьим входом блока выработки ошибки ветвления, выход которого яв.1яется выходом устройства. Источники информации,принятые во внимание при экспертизе: 1.«IEEE Transaction Computer, 19/0, Хо 12, p. 1153- 1159. 2.Клямко Э. 11. (1хе.мный и тестовый контроль автоматических цифровых вычислительиых машин, М.. «Сов. радио, 1963, с. 38-45.

Авторы

Даты

1978-03-15—Публикация

1975-05-05—Подача