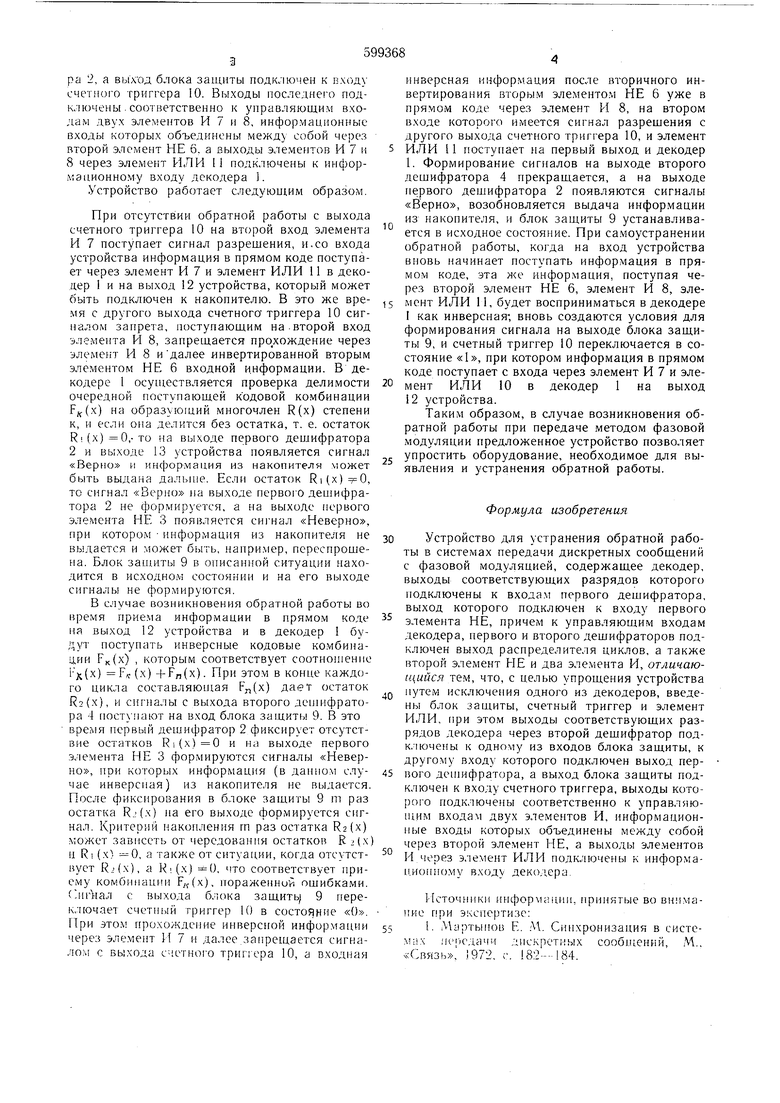

pa 2, a выход блока защиты подключен к входу счетного триггера 10. Выходы последнего подключены. соответственно к управляющим входам двух элементов И 7 и 8, информационные входы которых объединены между собой через второй элемент НЕ 6. а выходы элементов И 7 и 8 через элемент ИЛИ 11 подключены к информационному входу декодера 1. Устройство работает следующим образом. При отсутствии обратной работы с выхода счетного триггера 10 на второй вход элемента И 7 поступает сигнал разрешения, и.со входа устройства информация в прямом коде поступает через элемент И 7 и элемент ИЛИ 11 в декодер 1 и на выход 12 устройства, который может быть подключен к накопителю. В это же время с другого выхода счетного триггера 10 сигналом запрета, поступающим на.второй вход элемента И 8, запрещается прохождение через элемент И 8 и далее инвертированной вторым элементом НЕ 6 входной информации. В декодере 1 осун1,ествляется проверка делимости очередной поступающей кодовой комбинации F(x) на образующий многочлен R(x) степени к, и если она делится без остатка, т. е. остаток R(X)O,-TO на выходе первого дещифратора 2 и выходе 13 устройства появляется сигнал «Верно и информация из накопителя может быть выдана дальше. Если остаток Ri(x)0, то сигнал «Верно на выхОлТе первого деп1ифратора 2 не формируется, а на выходе первого элемента НЕ 3 появляется си1-нал «Неверно, при котором информация из накопителя не выдается и может быть, нанример, переспрошена. Блок запи-1ты 9 в описанной ситуации находится в исходном состоянии и на его выходе сигналы не формируются. В случае возникновения обратной работы во приема информации в прямом коде на выход 12 устройства и в декодер 1 будут поступать инверсные кодовые комбинации FK(.X) , которым соответствует соотноп1енне FX(X) F,c(x) +Fn(x). При этом в конце каждого цикла составляюн1ая Fn(x) дает остаток R2(x), и сигналы с выхода второго дешифратора 4 поступают на вход блока загциты 9. В это вредмя первьн1 деи1ифратор 2 фиксирует отсутствие остатков Ri(x)0 и на выходе первого элемента НЕ 3 формируются сигналы «Неверно, при которых информация (в данном случае инверсная) из накопителя не выдается. После фиксирования в блоке защиты 9 m раз остатка R.(x) на его выходе формируется сигнал. Критерий накопления гп раз остатка R2(x) может зависеть от чередования остатков Riix) ц RI (х) 0, а также от ситуации, когда отсутствует R)(x), а R(X) 0, что соответствует приему комбинации Frt(x), пораженной ошибками, (линал с выхода блока защиту 9 ггереключает счетный триггер 10 в состояние «О. При это.м прохождение инверсной информации через элемент И 7 и далее,запрещается сигналом с выхода счетного триггера 10, а входная инверсная информация после вторичного инвертирования вторым элементом НЕ 6 уже в прямом коде через элемент И 8, на втором входе которого имеется сигнал разрешения с другого выхода счетного триггера 10, и элемент ИЛИ 11 поступает на первый выход и декодер 1. Формирование сигналов на выходе второго дешифратора 4 прекращается, а на выходе первого дешифратора 2 появляются сигналы «Верно, возобновляется выдача информации из накопителя, и блок защиты 9 устанавливается в исходное состояние. При самоустранении обратной работы, когда на вход устройства вновь начинает поступать инфор.мация в прямом коде, эта же информация, поступая через второй элемент НЕ 6, элемент И 8, элемент ИЛИ 11, будет восприниматься в декодере I как инверсная вновь создаются условия для формирования сигнала на выходе блока защиты 9, и счетный триггер 10 переключается в состояние «Ь, при котором информация в прямом коде поступает е входа через элемент И 7 и элемент ИЛИ 10 в декодер 1 на выход 12 устройства. Таким образом, в случае возникновения обратной работы при передаче методом фазовой модуляции предложенное устройство позволяет упростить оборудование, необходимое для выявления и устранения обратной работы. Формула изобретения Устройство для устранения обратной работы в системах передачи дискретных сообщений с фазовой модуляцией, содержащее декодер, выходы соответствующих разрядов которого подключены к входам первого дешифратора, выход которого подключен к входу первого элемента НЕ, причем к управляющим входам декодера, первого и второго дещифраторов подключен выход распределителя циклов, а также второй элемент НЕ и два элемента И, отличающийся тем, что, е целью упрощения устройства нутем исключения одного из декодеров, введены блок защиты, счетный триггер и элемент ИЛИ, при этом выходы соответствующих разрядов декодера через второй дещифратор подк.1ючены к одному из входов блока защиты, к другому входу которого подключен выход перпого ден1ифратора, а выход блока защиты подключен к входу счетного триггера, выходы которого подключены соответственно к управляюи1им входам двух элементов И, информационHi ie входы которых объединены между собой через второй элемент НЕ, а выходы эле.ментов И через элемент ИЛИ подключены к информационному входу декодера. Источники информации, принятые во внимание при экспертизе: 1. ЛАартынов Е. Л. Синхронизация в системах 1К|)Сдачч дис.чретных сообщений, М., «Связь, 1972. V. .

Выход

Выход Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Устройство для дистанционного управления двухпозиционными объектами | 1983 |

|

SU1149299A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

| Устройство для устранения обратной работы в системах передачи дискретных сообщений с фазовой манипуляцией | 1990 |

|

SU1755722A3 |

| Устройство для определения распределений вероятностей амплитуд импульсных сигналов | 1990 |

|

SU1785010A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство синхронизации по циклам | 1977 |

|

SU743218A1 |

Авторы

Даты

1978-03-25—Публикация

1976-12-28—Подача