1

Изобретение относится к технике измерения характеристик случайных процессов и предназначается для осуществления дискриминации по уровням амплитуд случайных процессов и может быть использовано в анализаторах законов распределения.

Известен цифровой дискриминатор 1, имеющий больщой объем оборудования, а именно для д-разрядного двоичного счетчика необходимо не менее 4п логических элементов И, ИЛИ.

Наиболее близким техническим решением к предлагаемому является цифровой дискриминатор 2, содержащий «-разрядный двоичный счетчик, триггер результата анализа, элемент И результата анализа, триггер управления, переключатели нижнего и верхнего уровней дискриминации.

К недостаткам дискриминатора относится функциональная сложность устройства, связанная с предварительной записью в двоичный счетчик дополняющего кода числа, соответствующего исходному уровню анализа, перед началом функционирования и промежуточной записью дополняющего кода числа, соответствующего щирине дифференциального «окна, в процессе работы дискриминатора, что снижает его быстродействие. Для такого дискриминатора время задержки между приходом на вход счетчика импульса, который является граничным для исходного уровня анализа, и готовностью устройства к продолл ению анализа, т. е. моментом окончания записи в счетчик кода ширины дифференциального «окна, определяется выражением

о2(я+2)-,р,

где л - число триггеров в двоичном счетчике;

гтр - время задержки срабатывания триггера.

Следовательно, время задержки /о, которое определяет максимальную частоту поступления пмпульсов на вход счетчика, довольно велико и сильно зависит от числа разрядов счетчика.

Цель изобретения - повышение быстродействия и упрощение дискриминатора.

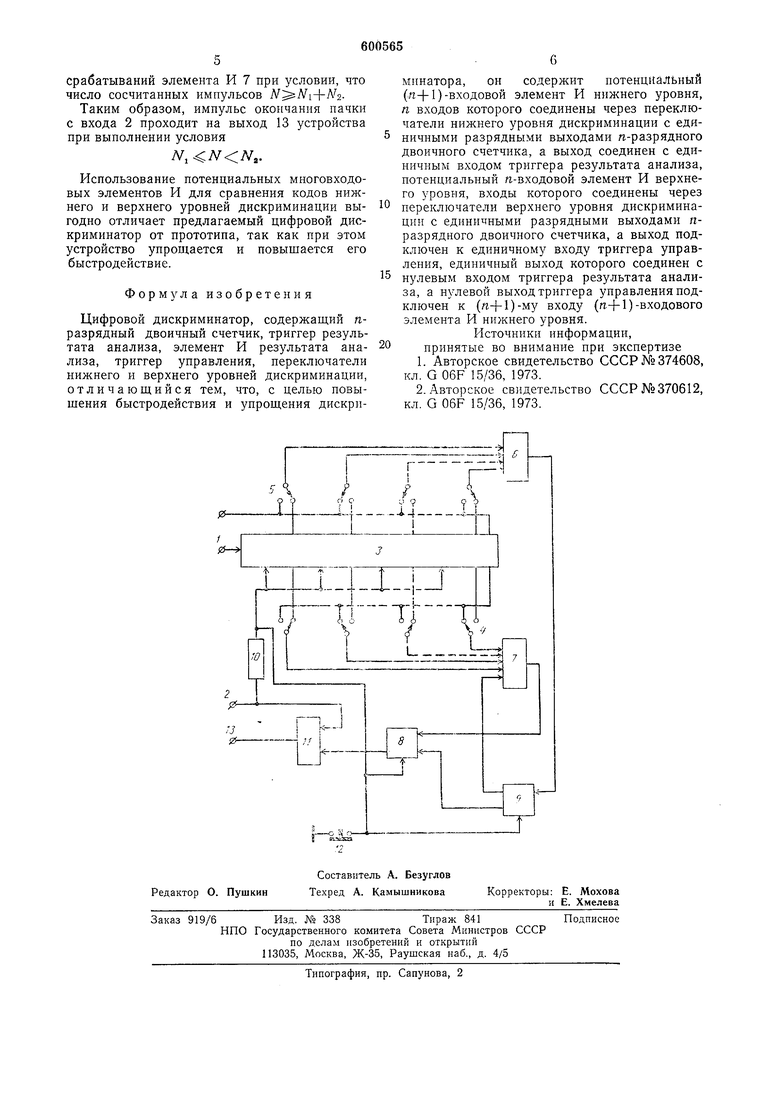

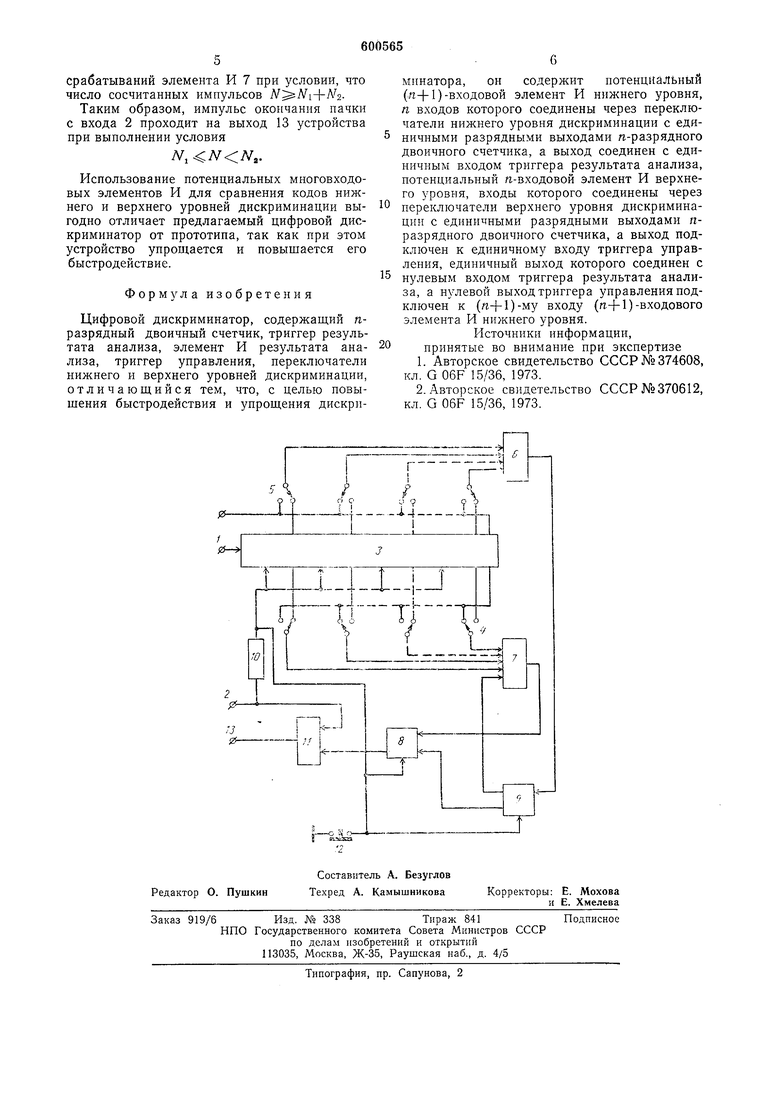

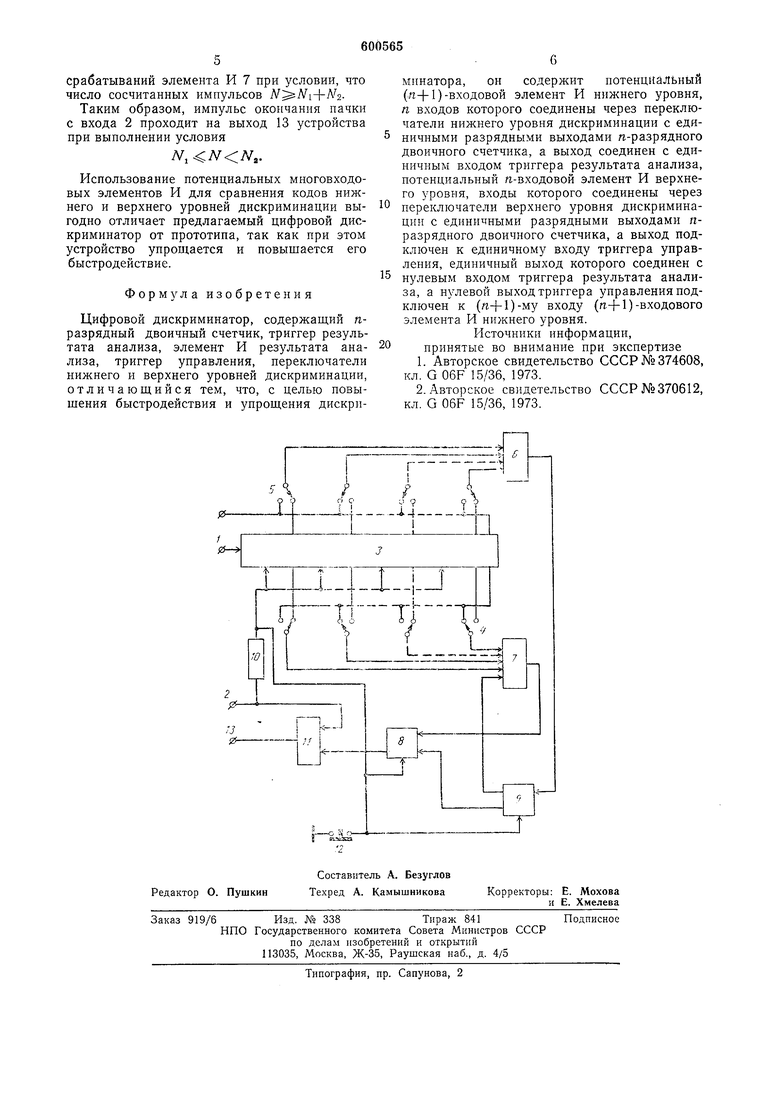

Это достигается тем, что цифровой дискриминатор содержит потенциальный (/г-fl)входовой элемент И нижнего уровня, п. входов которого соединены через переключатели нилснего уровня дискриминации с единичными разрядными вы.ходами я-разрядного двоичного счетчяка, а выход - с единичным входом триггера результата анализа, потенциальный д-входовой элемент И верхнего уровня, входы которого связаны через переключатели верхнего уровня дискриминации с единичными разрядными выходами л-разрядного двоичного счетчика, а выход подключен к единичному входу триггера уиравления, единичный выход которого соединен с нулевым входом триггера результата анализа, а нулевой выход триггера унравлениянодключен к )-иу входу (n-fl)-входового элемента И нижнего уровня. Входам элементов И ннл :него и верхнего уровней дискриминации, не иодключенным к единичным разрядиым выходам двоичного счетчика, соответствует единичный уровень нанряжеиия на них. В предложенном дискриминаторе минимальный нериод следования импульсов начки на входе счетчика в общем случае зависит от устаиовлеииых уровней анализа или, иначе, от места и числа иодключснных входов элемента И нижнего уровня анализа (или верхнего) к разрядам счетчика. Если к разрядам счетчика подключено k входов элемента И (, 2, 3, ...,п), но с условием, что иодключеиные разряды счетчика представляют собой последовательно соединенную группу разрядов, то в этом случае дискриминатор обладает наибольшим быстродействил и время задерлши /о определяется выражением тр + 4 const, где tti - время задержки срабатывания многовходового элемента И; k - число подключенных входов элемента И к разрядам счетчика. В других случаях для каждого числа подключениых входов элемента И имеет место такое подключение, которое обеспечивает максимальное время 4 для данного k, определяюидееся выражением (ft) n, Oinliimax а для всех прочих подключений (для данного fe) to заключено мелсду Ak)Ak) dmin min fOmfn max Таким образом, для предложенного устройства время о определяется выражением ,n () j. 1 j. Qmin min : тр P H Анализ выралсений для времени /о прототипа и предложенного устройства показывает, что в зависимости от установленных уровней анализа соотношение максимальных частот импульсов па входе счетчика предложенного устройства и прототипа определяется выралсением f/f-9 I maxapo o иn -- Т. е. предложенное устройство имеет значительно большее быстродействие по сравнению с прототипом. На чертеже- представлена структурная схема предлагаемого дискриминатора. Цифровой дискриминатор состоит из входной клеммы 1 двоичного счетчика, входной клеммы 2 имиульса окончания пачки импульсов, п-разрядного двоичного счетчика 3,переключателей 4 и 5 нижнего и верхнего уровней дискриминации соответственно, потенциального п-входового элемента И 6 верхнего уровня анализа, нотенциального {п+1)-входового элемента И 7 нижнего уровня анализа, триггера 8 результата анализа, триггера 9 управления, линии 10 задержки, элемента И 11 результата анализа, кнопки 12 приведения устройства в исходное состояние, выходной клеммы 13. Работает цифровой дискриминатор совместно с блоком амплитудного преобразования, который нреобразует амплитуду входного сигнала в пачку импульсов и вырабатывает также импульс ее окончания. Перед началом работы с помощью кнопки 12 дискриминатор приводится в исходное состояиие. Переключатели нижнего 4 и верхнего 5 уровней дискриминации подключаются к тем единичным разрядным выходам двоичного счетчика, прямые коды которых соответствуют величинам нижнего NI и верхнего NZ уровией дискриминации. Если на входе 1 появляются импульсы, то двоичный счетчик начинает их сосчитывать. В процессе счета в момент времени, когда число сосчитаниых импульсов Л становится равным нижнему уровню дискриминации что соответствует появлению единичных уровней напряжения на входах элемента И 7 нижнего уровня, подключенных к счетчику, элемент И 7 срабатывает на совпадение и онрокидывает триггер 8 результата анализа, выходе которого образуется единичный разрешающий уровень напряжения. Если число импульсов в начке больше или равно Ль но меньше верхнего уровня N, то импульс окончания начки, ноступающий на вход 2, проходит на выход элемента ИИ, так как на втором его входе стоит разрешающий уровень, Этот же импульс через линию 10 задержки приводит устройство в исходное положение, осуществляя сброс всех триггеров устройства. Если число сосчитанных импульсов Л становится равным верхнему уровню дискриминации NZ, то ироисходит срабатывание элемента И 6 верхнего уровня, который опрокидывает триггер 9 управления. В свою очередь, риггер 9 по единичиому выходу опрокндыват в исходное состояние триггер 8, на выходе оторого при этом разрещающий потенциал, становленный при срабатывании элемента 7, сменяется запрещающим для элемента И, и импульс окончания пачки в этом слуае не проходит на выход элемента И 11. Одновременно с блокировкой элемента И 1 триггер 9 по нулевому выходу производит локировку элемеита И 7 нижнего уровня искриминации для исключения повторных

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифровой дискриминатор | 1975 |

|

SU591854A1 |

| ЮЗНАЯ | 1973 |

|

SU370612A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ ДИСКРИМИНАТОР | 1973 |

|

SU378859A1 |

| Цифровой дискриминатор | 1983 |

|

SU1128247A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Цифровой дискриминатор | 1979 |

|

SU881732A1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| ЦИФРОВОЙ ДИСКРИМИНАТОР | 1993 |

|

RU2072552C1 |

| СПЕКТРОМЕТРИЧЕСКИЙ СПОСОБ ИЗМЕРЕНИЯ ЯДЕРНЫХ ИЗЛУЧЕНИЙ И РЕАЛИЗУЮЩАЯ ЕГО СПЕКТРОМЕТРИЧЕСКАЯ СИСТЕМА | 2002 |

|

RU2269798C2 |

Авторы

Даты

1978-03-30—Публикация

1975-02-27—Подача