1

Настоящее изобретение относится к области цифровой вычислительной техники и может быть использовано при построении интегрирующих вычислительных устройств, цифровых дифференциальных 5 анализирующих систем и цифровых интегрирующих машин.

Известен цифровой интегратор 1 имеющий низкое быстродействие, посколькуЮ на отработку каждой точки в устройстве затрачивается и (где И -разрядность) тактов для суммирования приращения функции, поступающих на вход одноразрядного сумматора функции с содержимым регистра функции и для последовательного суммирования содержимого регистра функции с содержиким регистра интеграла.20

Наиболее близким по технической сущности является цифровой интегратор 2, содержащий первый решающий блок, состояп№1й из сумматора функции, сумматора интеграла, .блока, выделения при- gg ращения и преобразователя кода, причем первый выход сумматора функции соединен с его первым входом, второй j вход сумматора функции соединен с первым входом преобразователя кодов, ход которого подключен к первому входу сумматора интеграла, первый выход которого соединен с первым входом блока выделения приращения, первый выход которого подключен ко второму входу сумматора интеграла.

Недостатком известного устройства является низкое быстродействие.

Целью изобретения является повышение быстродействия.

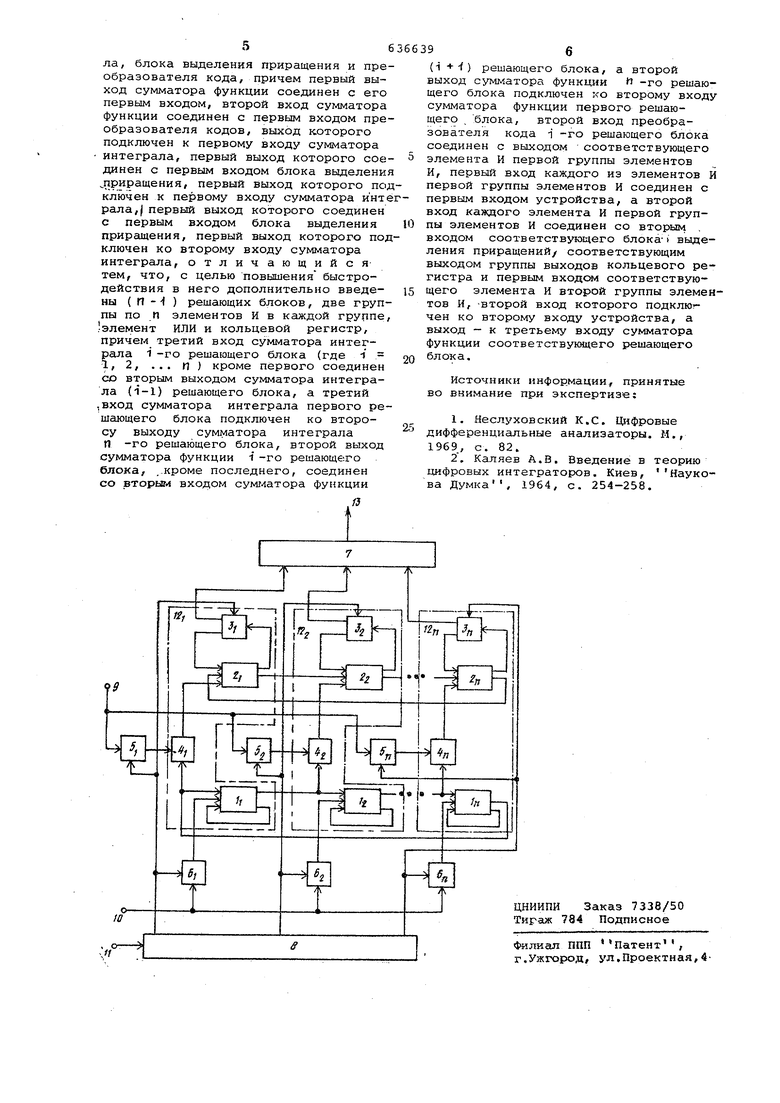

Поставленная цель достигается тем, что в известное устройство введены (И -1)решающих блоков, две группы по п элементов И в каждой группе, элемент ИЛИ и кольцевой регистр, причем третий вход сумматора интеграла 1-го решающего блока (где 1 1,2,.... п)/ кроме первого соединен со вторым выходом сумматора интеграла ( i -1) решающего блока, а третий вход сумматора интеграла первого решгиощего. .блока подключен ко второму выходу сумматора интеграла It-го решающего блока, второй выход сумматора функции i -го решающего блока, кроме последнего, соединен со вторым входом сумматора функции ( i +1) решающего блока, а второй выход сумматора функции П-го решающего блока подключен ко второму входу сумматора функции первого решающего блока, второй вход преобраэователя кода i -го решающего блока сое динен с выходом соответствующего элемента И первой группы элементов И, первый вход каждого из элементов И первой группы элементов И соединен с первым входом устройства,- а второй вход каждого элемента И первой группы элементов И соединен со вторым входом соответствующего блока выделе,ния приращений соответствующим выхо дом группы выходов кольцевого регистра и первым входом соответствующего элемента И второй группы элементов И, второй вход которого подключен ко второму входу устройства, а выход - к третьему входу сумматора функции соот ветствующего решающего блока. Блок-схема устройства представлена на чертеже. Устройство содержит Я сумматоров функции, П сумматоров 2.-2 интеграла. Г) блоков выделения приращений, п преобразователей кода, первую группу элементов И, содержащую П элементов И ), вторую группу элементов И 6, содержащую П элементов И , элемент ИЛИ 7 и кольцевой регистр 8, первый и второй вход 9, 10 устройства, вход 11 ререшающие блоки 12 -12, выход гистра 13 устройства. Устройство работает следуюидам образом. На входы 10 последовательно во времени поступают приращенля зависимой переменной, которые суммируются на сумматорах 1, .... 1 ( функции с предыдущими значениями подынтеграль ной функции. Одновременно с этим значения подынтегральной функции поступа ют на входы сумматоров 2, 2, ... 2 интеграла через преобразователи 4, 4, ..., 4j кода, управляемые сигналами на входе 9 приращения независимой переменной. На одноразрядных сумматорах 2 , 2 , 2 интеграла последовательно во времени производится суммирование предыдущих значений интеграла со значениями подынтегральной функции, пред ставленными последовательным кодом на выходах одноразрядных сумматоров In функции, с выходов пе реноса одноразрядных сумматоров 2 f, функции сигналы переноса - 3, поступают на блоки 3, выделения приращения, которые производят выдачу приращений на выходы устройства, под воздействием сигналов, поступающих последовательно во времен При интегрировании по Риману входы преобразователей 4, 2. П код необходимо соединить между собой и подключить к общему входу независимой переменной, а преобразователи 4.), 2 ... 4 кода в этом случае представляю собой обычные элементы И, через кото рые коды с выходов сумматоров 1, 1, ,.., Ij функции поступают на входы сумматоров 2, 2, -, 2j интеграла. Для сокращения количества выводов интегратора и упрощения коммутации между интеграторами выходы блоков 3, 32 , ... 3 выделения приращения объединяются с помощью элемента ИЛИ 7 и подключаются к общему выходу 13 устройства, а другие входы блока выделения приращения 3, 3, ..., 3ц подключаются к управляющей шине. Третьи входы одноразрядных сумматоров 1 ..., ifj функции через вторую г-руппу элементов И 6, 6, ..., бг подключенных первыми входами к управляющей шине, соединены с общим входом зависимой переменной. Тогда информация со входа коммутируется последовательно,- под воздействием импульсов на управляющей шине, на входы суммато ров 1, Ig, ,.., If, функции. При интегрировании по Стилтьесу другие входы преобразователей. 4, 4, , . ,,; 4f, кода через первую группу элементов И 5, 5, ..., 5, подключаются к общему входу независимой переменной, а первые входы первой группы элементов И 5, 5, ..., 5 соединяются с управляющей шиной. Количество управляющих входов может быть сокращено в П раз, если в устройство ввести кольцевой сдвиговый регистр 8, вход которого соединен с общим управляющк&з входом, а выходы подключены к другим входам бловыделения приращений и к первы л входам первой и второй групп элементов И 5 , Зуг , .,, 5 и 6 , б2, ..., б п , Тогда по сигналу на входе производится сдвиг единицы последовательно по разрядив кольцевого сдвигового регистра 8, управляющие сигналы с выходов которого обеспечивают управление работой устройства. Предлагаемое устройство имеет регулярную структуру по каждому из разрядов, чем обеспечивается простота реализации интегратора в виде БИС. Данное устройство превосходит по быстродействию в П раз известные интеграторы последовательного действия при незначительном увеличении объема оборудования. Оно превосходит по быстродействию .также и интеграторы параллельного типа, имеющие большее количество оборудования, в которых такт работы устройства равен времени суммирования И -разрядных чисел, в то время как в предлагаемом устрфйстве тактовая частота определяется временем суммирования одноразрядных чисел. Формула изобретения Цифровой интегратор, содержащий первый решающий блок, состоящий из сумматора функции, сумматора интегра

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство масштабирования цифрового дифференциального анализатора | 1983 |

|

SU1156069A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1980 |

|

SU879586A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

Авторы

Даты

1978-12-05—Публикация

1975-04-21—Подача