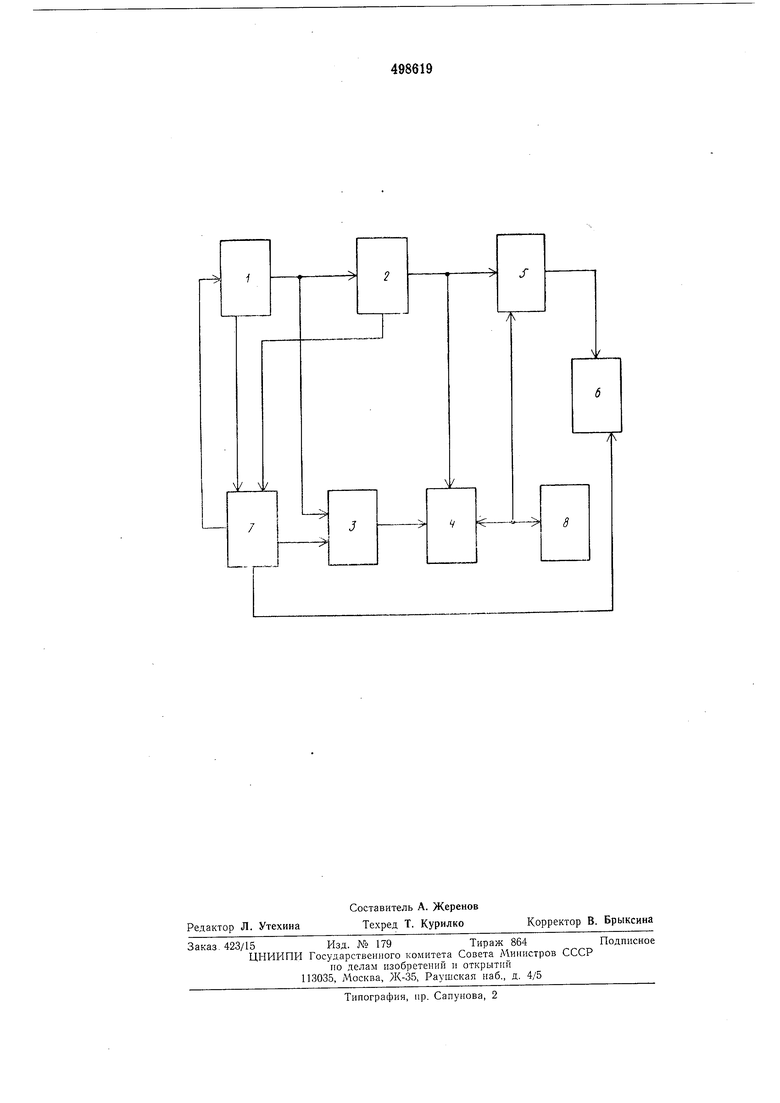

Блок 7 управления организует работу всех блоков устройства, т. е. управляет записью информации из блока 1 ввода в блок 2 памяти и регистр настройки 3, управляет работой блока 6 индикации и осуществляет управление однократным и циклическим режимами работы.

Контроль проверяемого узла осуществляется с помощью тестов, состоящих из последовательности элементарных тестов, разрядность которых равна чнслу внешних контактов проверяемого узла.

Каждый элементарный тест включает в себя стимулы и эталоны. Стимулы - совокупность сигналов, одновременно подаваемых на входные контакты, эталоны - совокупность сигналов, которые должны появиться на выходах исправного узла при подаче на его входы стимулов.

Устройство работает следующим образом.

Командная информация из блока 1 ввода поступает в блок управления и включает следующие команды «Начало, «Запись 1, «Запись 2, «Проверка и «Конец.

По команде «Начало, все блоки устройства устанавливаются в исходное состояние. По команде «Запись 1 в регистр настройки 3 записывается информация о входных контактах проверяемого узла. По команде «Запись 2 тестовая информация записывается в блок 2 памяти. По команде «Проверка начинается считывание информации из блока 2. Очередной элементарный тест поступает на первые входы коммутатора 4, который выделяет стимулы из элементарного теста и подает их на входы проверяемого узла. Работой коммутатора 4 управляет регистр Настройки 3, в котором хранится информация о входных контактах проверяемого узла.

Одновременно элементарный тест поступает и на первые входы блока 5 сравнения. Стимулы, выделенные коммутатором из элементарного теста, поступают на входы проверяемого узла, а затем вместе с сигналом последнего поступают на вторые входы блока 5 сравнения.

В однократном режиме работы элементарные тесты на вход проверяемого узла подаются однократно, и по команде «Конец на блэке индикации фиксируется результат контроля. В случае несравнения каких-либо сигналов в блоке индикации отражается номер элементарного теста, в котором обнаружено несоответствие, и номер контакта, на котором произошло несравнение.

В циклическом режиме работы любая группа элементарных тестов циклически подается

на входь проверяемого узла, что позволяет проследить, например, с помощью осциллографа, прохождение сигналов внутри проверяемого узла и определить место неисправности. Таким образом, в блоке сравнения не только сравниваются коды эталонов с кодами реакции, но в каждом элементарном тесте проверяется правильность подачи стимулов на входы проверяемого узла. В результате повышается достоверность контроля, что особенно

важно для проверки узлов, имеющих много внешних контактов и содержащих сложные коммутаторы.

Предмет изобретения

Устройство для контроля цифровых узлов, содержащее блок ввода, блок памяти, коммутатор, блок сравнения, блок индикации, блок управления, причем первый выход блока ввода соединен со входом блока памяти, выход которого подключен к первому входу коммутатора, выходами соединенного с внешними контактами контролируемого узла, второй выход блока ввода соединен со входом блока управления, выходы которого подключены соответственно к управляющим входам блока ввода, блока памяти и блока индикации, соединенного входом с выходом блока сравнения, отличающееся тем, что, с целью упрощения и повышения достоверности работы устройства, в него введен регистр настройки, соединенный входом с первым выходом блока ввода, управляющим входом - с выходом блока управления, выходом - со вторым входом коммутатора; выход блока памяти подключен к первому входу блока сравнения, второй вход которого соединен с выходом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1977 |

|

SU643876A2 |

| Устройство для контроля логических блоков | 1978 |

|

SU734694A1 |

| Устройство для контроля цифровых узлов | 1980 |

|

SU932497A1 |

| Устройство для контроля логическихблОКОВ | 1978 |

|

SU813430A1 |

| Устройство для тестового контроля блоков радиоэлектронной аппаратуры | 1980 |

|

SU905887A1 |

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1003090A1 |

| Устройство для контроля цифровых блоков | 1978 |

|

SU746553A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1518906A2 |

Авторы

Даты

1976-01-05—Публикация

1974-07-02—Подача