(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1305681A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1277107A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

| Мультимикропрограммная управляющая система | 1989 |

|

SU1631542A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

1

Изобретение относится к области вычислительной техники и предназначено для применения в устройствах управления электронных цифровых вычислительных машин.

Известно устройство микропрограммного управлсння, содержащее генератор тактовых импульсов, запоминающее устройство, вход которого подключен к выходу схемы формирования адреса, а выход -- к входу регистра микрокоманд; регистр микрокоманд состоит из операционной и адресной частей, причем выход операционной части подключен к входу дешифратора микроопераций, а выход адресной части - к входу схемы формирования адреса, которая также подключена к, шине условий переходов {1|.

Недостатками известного устройства являются большой объем памяти и низкие функциональные возможности.

Наиболее близким к предложенному по технической сущности является устройство микропрограммного управления, содержащее запоминающнй блок, вход которого соединен с выходом блока формирования адреса, а выход через регистр микрокоманд - с входом дешифратора микроопераций, выходы которого являются выходами устройства, регистр адресов микрокоманд, первый вход которого являегся

первым входом устройства, вторым входом устройства является первый вход блока формирования адреса 2J.

Известное устройство обладает большим объемом микропрограммной памяти и низкими функциональными возможностями при добавлении новых микропрограмм.

Действительно, уменьшение объема микрогфограммной памяти в тиком устройстве достигается за счет объедннения одинаковых участ.- ков микропрограмм, иначе говоря, за счет мнкропрограммных подпрограмм. Это требует при каждом переходе на подпрограмму запоминания адреса возврата и затем его восстанавлиаання. Кроме того, оказывается невозможной компоновка подпрограмм, объединяющих мнкS рокоманды, не являющиеся алгорнтмическн (со держательно) с .вязанными последовательностями в других микропрограммах.

Цель изобретения - уменьшение объема микропрограммной памяти и увеличение функциональных возможностей устройства микропрограммного управления.

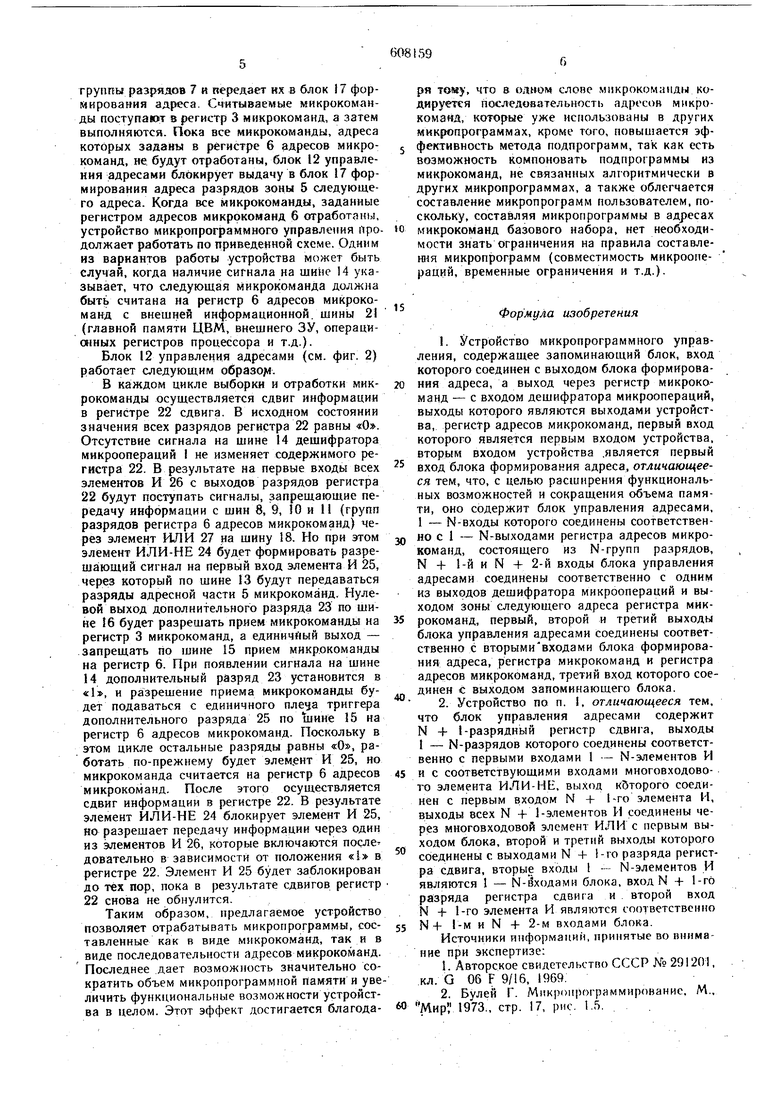

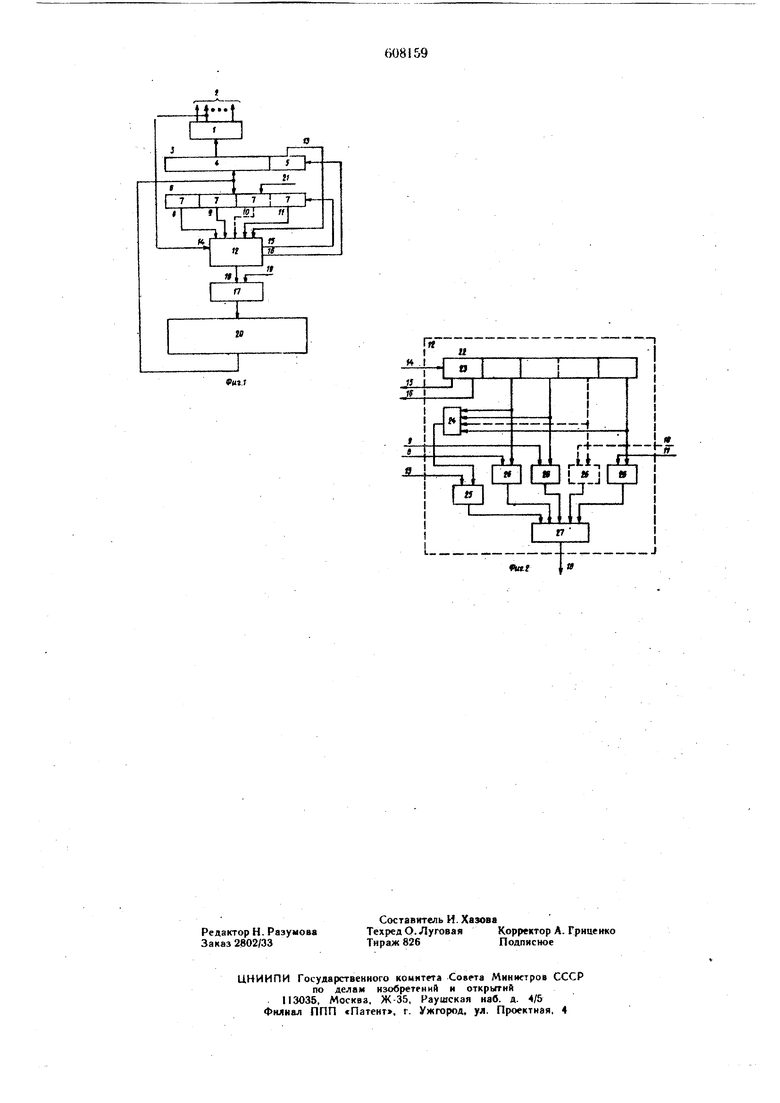

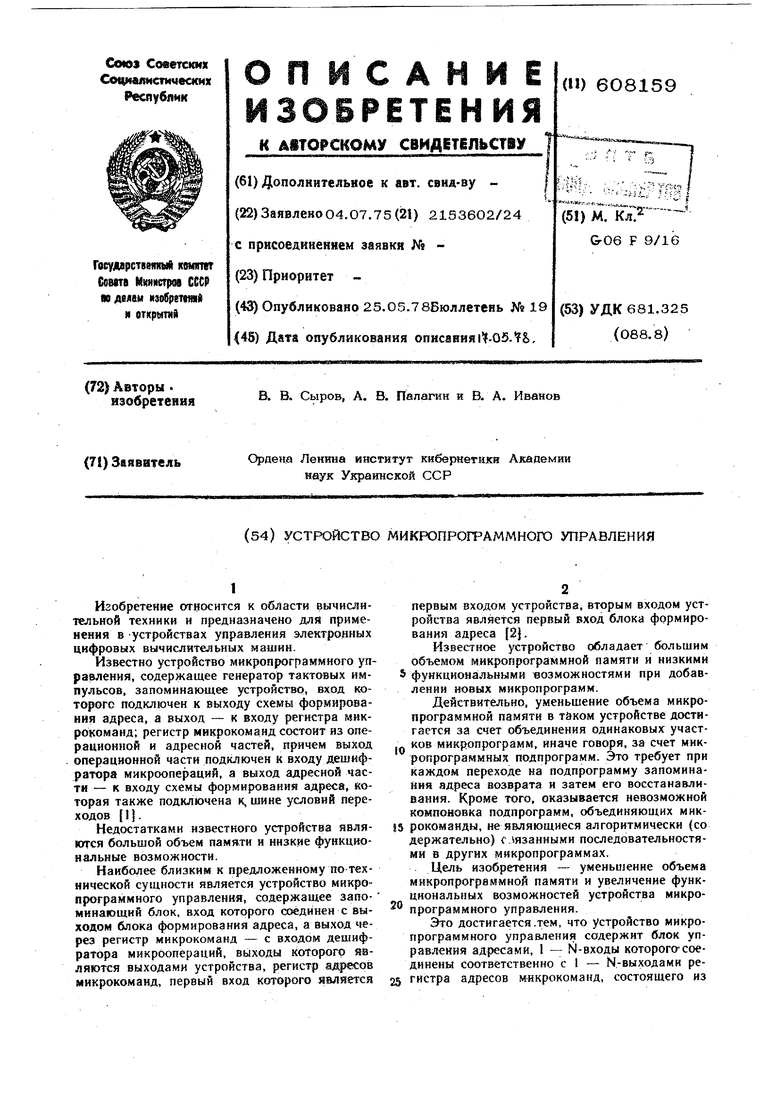

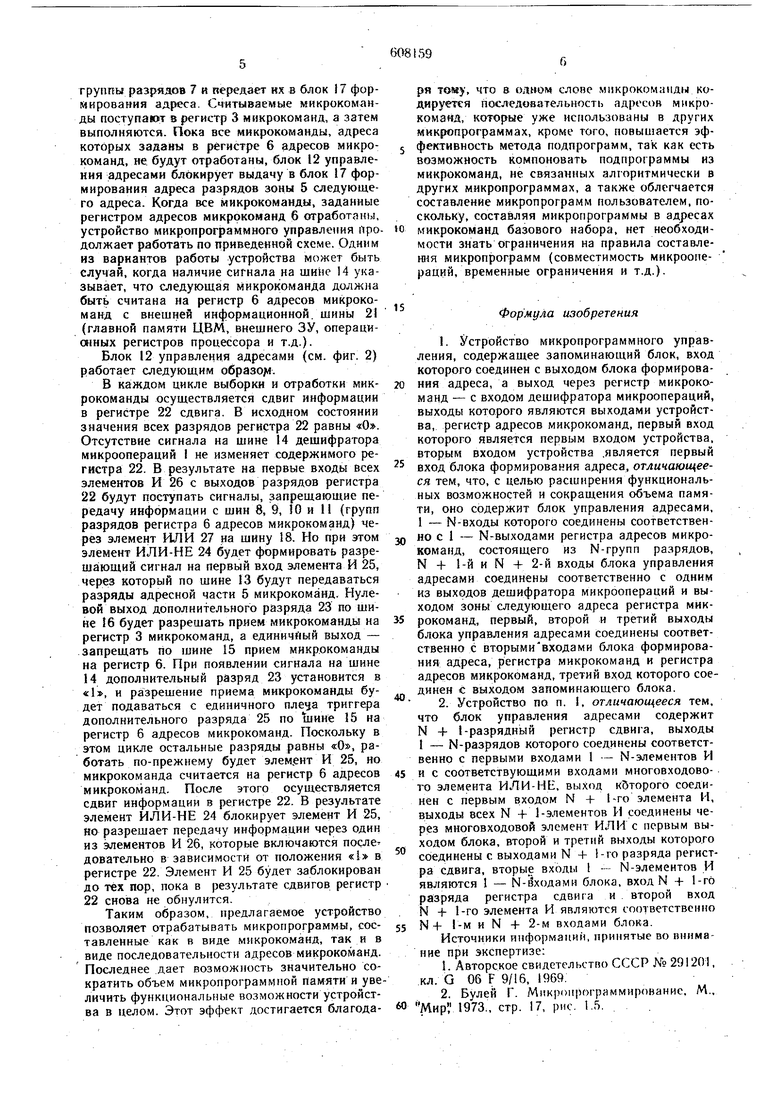

Это достигается .тем, что устройство микропрограммного управления содержит блок управления адресами, I - N-входы которого-соединены соответственно с I - N-выходами регистра адресов микрокоманд, состоящего из N-групп разрядов, N + 1-й и N + 2-й входы блока управления адресами соединены соответственно с одним из выходов Дешифратора микроопераций и выходом зоны следующего адреса регистра микрокоманд, первый, второй и третий выходы блока управления адресами соединены соответственно с вторыми входами блока формирования адреса, регистра микрокоманд и регистра адресов микрокоманд, третий вход которого соединен с выходом запоминающего блока, а блок управления адресами содержит N -f I-разрядный регистр сдвига, выходы 1 - N-разрядов которого соединены соответственно с первыми входами 1 - N элементов И и с соответствующими входами многовходового элемента ИЛИ-НЕ, выход которого соединен с первым входом N + 1-го элемента И, выходы всех N Ч- 1-элементов И соединены через многовходовой элемент ИЛИ с первым выходом блока, второй и третий выходы которого соединены с выходами N -f 1-го разряда регистра сдвига, вторые входы 1 - Ылэлементов И являются 1 - N-входами блока, вход N -f 1-го разряда регистра сдвига и второй вход N -J- ifo элемента И являются соответственно N -f- 1-м и N -Ь 2-м входами блока. Устройство микропрограммного управления позволяет отрабатывать микропрограммы, составленные как в виде микрокоманд, так и в виде последовательности адресов микрокоманд. Это дает возможность значительно сократить объем микропрограммной памяти и увеличить функциональные возможности устройства в целом за счет того, что в одном слове микрокоман; ы может кодироваться последовательность адресов нескольких микрокоманд, которые уже использованы в других микропрограммах. На фиг. 1 приведена принципиальная схема устройства; на фиг. 2 - структурная схема блока управления адресами. Устройство микропрограммного управления содержит дешифратор I микроопераций с выходами 2, регистр 3 микрокоманд с операцион. ной зоной 4 и зоной 5 следующего адреса, регистр 6 адресов микрокоманд, содержащий .Nrrpynn разрядов 7, которые по шинам 8, 9, 10. И подключены к соответствующим входам блока 12 управления адресами. К блоку 12 по шине 13 подключены также разряды зоны 5 (едующего адреса регистра 3 микрокоманд, а по шине 14 - один из выходов 2 дешифратора I микроопераций. Выходы 15 и 16 блока управления 12 адресами подключены к управляющим входам регистра 3 микрокоманд и регистра 6 адресов микрокоманд соответственно. Выходы блока 17 формирования адреса (микрокоманды) по шине 18 подключены к выходу блока 12 управления адресами, а по шине 19 - к схемам, вырабатывающим сигналы, кото рые должны вызвать ветвления в микропрограммах (на схеме не показаны). Выход блока 17 подключен к входу запоминающего блока 20, причем выход последнего подключен к входам регистра 3 микрокоманд и регистра б адресов микрокоманд. Цифрой 21 обозначена шина, по которой регистр 6 адресов микрокоманд может соединяться с регистрами или главной памятью зычислительной машины. В качестве регистра 6 адресов микрокоманд может использоваться одни из регистров операционного устройства цифровой вычислительной машины. Блок 12 управления адресами (см. фиг. 2) содержит N I-разрядный регистр сдвига 22 с N -Ь 1-ым дополнительным разрядом 23, многовходовый элемент ИЛИ-НЕ 24, многоразрядный элемент И 25, многоразрядные элементы И 26 и многовходовый элемент ИЛИ 27. Вход N -f 1-го разряда 23 подключен к шине 14, а прямой и инверсный выходы - к шинам 15 и 16 соответственно. Единичные выходы остальных N-разрядов подключены к входам элемента ИЛИ-НЕ 24 и к первым входам элементов И 26, к вторым входам которых подключены шнны 8, 9, 10 и П соответственно. Выход элемента ИЛИ-НЕ 24 подключен к первому влоду элемента И 25, к второму входу которого подключена шиНа 13. Выходы всех элементов И 25, 26 подключены к входам элемента ИЛИ 27, имеющего выход 18. Принцип работы устройства заключается в следующем. В первом такте на регистр 3 микрокоманд из запоминающего блока 20 считывается микрокоманда. Во втором такте в зависимости от значений разрядов операционной зоны 4 (микрокоманды) дешифратор 1 микроопераций вырабатывает управляющие сигналы, которые по шинам 2 поступают в устройства и схемы цифровой вычислительной машины. В этом же такте в блок 52 управления адресами по шине 13 из зоны 5 следующего адреса (микрокоманды) поступает код, определяющий адрес следующей микрокоманды, который затем передается в блок 17 формирования адреса. Этот адрес модифицируется в зависимости от выполнения различных логических условий (сигналов на щннах 19) и поступает на адресный вход запоминающего блока 20. На этом цикл выборкн и отработки микрокоманды заканчивается. Если в результате отработки микрокоманды на шине 14 не появляется сигнал, то в новом цикле в первом такте блок 12 управления адресами по шине 16 вырабатывает сигнал, разрешающий прием на регистр 3 микрокоманд новой микрокоманды, и устройство микропрограммного управления работает в дальнейшем по этой же схеме. Если же в результате отработки микрокоманды на шине 14 появляется сигнал, то в первом такте следующего цнкла блока 12 управления адресами по шнне 15 вырабатывает сигнал, разрешающий прием новой микрокоманды на регистр 6 адресов микрокоманд. На шине 16 при этом сигнал отсутствует. Микрокоманд, принятая на регистр 6 адресов микрокоманд, рассматривается как микрокоманда, содержащая совокупность адресов микрокоманд. Которые должны быть последовательно выполнены. Этн адреса располагаются в группах разрядов 7. Обработка микрокоманды, принятой на регистр 6 адресов микрокоманд, заключается в том, что блок 12 уп-. равления адресами последовательно выбирает

группы разрядов 7 и передает их в блок 17 формирования ад{№са. Считываемые микрокоманды поступают в регистр 3 микрокоманд, а затем выполняются. Пока все микрокоманды, адреса которых заданы в регистре 6 адресов микрокоманд, не будут отработаны, блок 12 управления адресами блокирует выдачу в блок 17 формирования адреса разрядов зоны 5 следующего адреса. Когда все микрокоманды, заданные регистром адресов микрокоманд 6 отработаны, устройство микропрограммного управления продолжает работать по приведенной схеме. Одним из вариантов работы устройства может быть случай, когда наличие сигнала на шине 14 указывает, что следующая микрокоманда должна быть считана на регистр 6 адресов микрокоманд с внешней информационной, шины 21 (главной памяти ЦВМ, внешнего ЗУ, операционных регистров процессора и т.д.).

Блок 12 управления адресами (см. фиг. 2) работает следуюш,им образод.

В каждом цикле выборки и отработки микрокоманды осушествляется сдвиг информации в регистре 22 сдвига. В исходном состоянии значения всех разрядов регистра 22 равны «О. Отсутствие сигнала на шине 14 дешифратора микроопераций I не изменяет содержимого регистра 22. В результате на первые входы Всех элементов И 26 с выходов разрядов регистра 22 будут поступать сигналы, запрешаюшие передачу информации с шин 8, 9, 0 и И (групп разрядов регистра 6 адресов микрокоманд) через элемент ИЛИ 27 на шину 18. Но при этом элемент ИЛИ-НЕ 24 будет формировать разрешающий сигнал на первый вход элемента И 25, через который по шине 13 будут передаваться разряды адресной части 5 микрокоманд. Нулевой выход дополнительного разряда 23 по шине 16 будет разрешать прием микрокоманды на регистр 3 микрокоманд, а единнчйый выход - запрещать по шине 15 прием микрокоманды на регистр 6. При появлении сигнала на шине 14 дополнительный разряд 23 установится в «1, и разрешение приема микрокоманды будет подаваться с единичного триггера дополнительного разряда 25 по шине 15 на регистр 6 адресов микрокоманд. Поскольку в этом цикле остальные разряды равны «О, работать по-прежнему будет элем.ент И 25, но микрокоманда считается на регистр 6 адресов микрокоманд. После этого осуществляется сдвиг информации в регистре 22. В результате элемент ИЛИ-НЕ 24 блокирует элемент И 25, но разрешает передачу информации через один из элементов И 26, которые включаются после довательно в зависимости от положения «1 в регистре 22. Элемент И 25 будет заблокирован до тех пор, пока в результате сдвигов регистр 22 снова не обнулится.

Таким образом, предлагаемое устройство позволяет отрабатывать микропрограммы, составленные как в виде микрокоманд, так и в виде последовательности адресов микрокоманд. Последнее дает возможность значительно сократить объем микропрограммной Памяти и увеличить функциональные возможности устройства в целом. Этот эффект достигается благодаря то«у, что в одном слоне микрокоманды кодируется последовательность адресов микрокоманд, которые уже использованы в других микропрограммах, кроме того, повышается эффективность метода подпрограмм, так как есть возможность компоновать подпрограммы из микрокоманд, не связанных алгоритмически в других микропрограммах, а также облегчается составление микропрограмм пользователем, поскольку, составляя микропрограммы в адресах микрокоманд базового набора, нет необходимости знать ограничения на правила составления микропрограмм (совместимость микроопераций, временные ограничения и т.д.).

15

Формула изобретения

. Устройство микропрограммного управления, содержащее запоминающий блок, вход которого соединен с выходом блока формироваНИН адреса, а выход через регистр микрокоманд - с входом дешифратора микроопераций, выходы которого являются выходами устройства, регистр адресов микрокоманд, первый вход которого является первым входом устройства, вторым входом устройства .является первый

вход блока формирования адреса, отличающееся тем, что, с целью расширения функциональных возможностей и сокращения объема памяти, оно содержит блок управления адресами, 1 - N-входы которого соединены соответственно с 1 - N-выходами регистра адресов микрокоманд, состоящего из N-rpynn разрядов, N + 1-й и N + 2-й входы блока управления адресами соединены соответственно с одним из выходов дешифратора микроопераций и выходом зоны следующего адреса регистра микрокоманд, первый, второй и третий выходы блока управления адресами соединены соответственно с вторымивходами блока формирования адреса, регистра микрокоманд и регистра адресов микрокоманд, третий вход которого соединен € выходом запоминающего блока.

и с соответствующими входами многовходовото элемента И Л И-НЕ, выход которого соединен с первым входом N + 1-го элемента И, выходы всех N + 1-элементов И соединены через многовходовой элемент ИЛИ с первым выходом блока, второй и третий выходы которого

соединены с выходами N + Ьго разряда регистра сдвига, вторые входы I - N-элементов И являются 1 - N-йходами блока, вход N -}- 1-го разряда регистра сдвига и . второй вход N -J. 1-го элемента И являются соответственно

N+ 1-м и N + 2-м входами блока.

Источники информации, принятые во нннманне при экспертизе:

Vut.J

«a

Авторы

Даты

1978-05-25—Публикация

1975-07-04—Подача