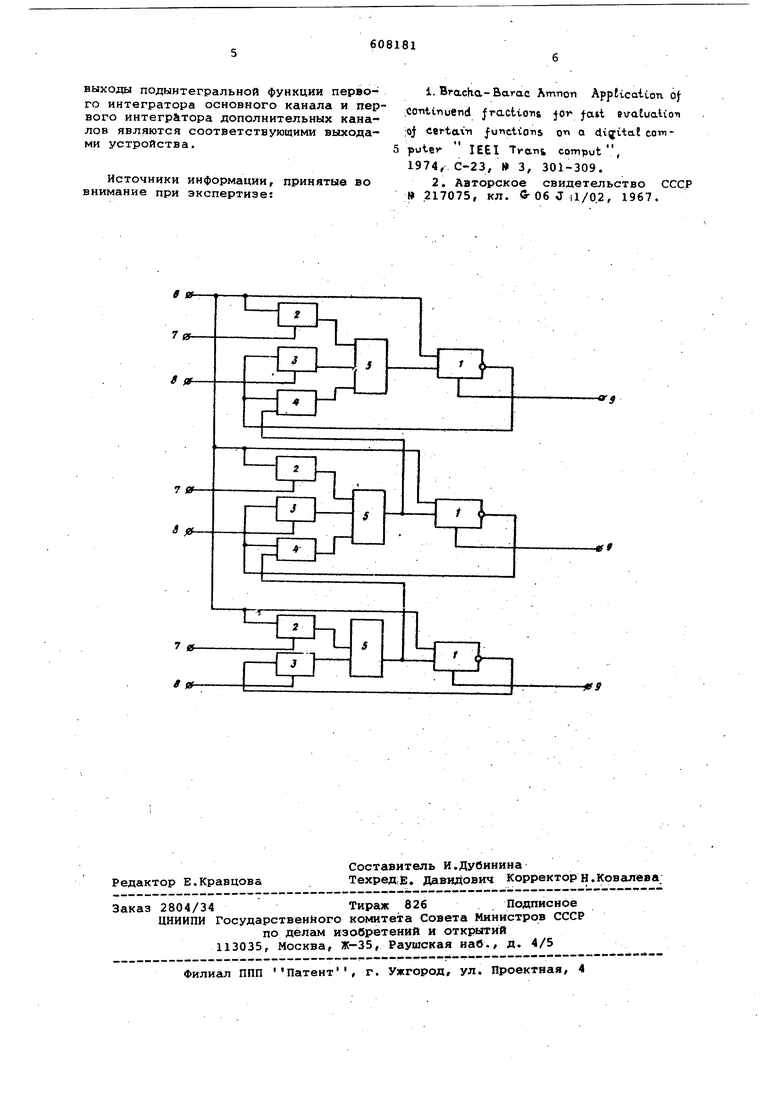

; .Это достигается тем, что в предложенное устройство введены п дополнительных каналов, каждый из которых состоит из четырех интеграторов и сум матора/ выход которого подключен ко входу приращения подынтегральной функ ции первого интегратора соответствующего .канала, выходы второго, третьего и четвертого интеграторов подсоединен ны к соответствующим входам сумматора данного канала, инверсный выход первого интегратора подключен ко входам приращений независимой переменной третьего и четвертого интеграторов данного канала, входы приращений независимой переменной первого и второг интеграторов основного и дополнительных каналов подсоединены к входной шине независимой машинной переменной, вход приращений подынтегральной функции четвертого интегратора подключен к выходу сумматора последующего канала, инверсный выход первого интегратора основного канала подсоединен к входу приращений независимой переменнйй третьего интегратора, выходы поды тегральной функции первого интегратора основного канала и первого интегратора дополнительных каналов явля ются соответствующими выходами устрой ства. На чертеже показана структурная схема предложенного устройства. Устройство содержит интеграторы 1-4, сумматор 5. Входа приращений независимой переменной интеграторов 1, 2 во всех п группах объединены и под соединены к шине 6j на которую поступают приращения &t независимой машинной переменной i. На входы 7 постоянных коэффициентов поступают значения Р , на входы 8 постоянных коэффициент поступают значения 0.. С выходов 9 подынтегральных функций снимаются результаты вычислений. В устройстве все звенья цепной дроби (1) вычисляются одновременно путем решения следующей системы неоднородных разностных уравнений qJyKi pK 4K(i o tK-ni Ц.1,г,... т,; о, 1.0,1, 2,..л,. Теоретически и практически установ леио, что итерационный процесс, соответствующий разностному уравнению, сходится, если ., Следовательно существует такой шаг ut 1, при котором, начиная с некоторого значения I t где U - заданная погрешность вычисле ний. Иными словами у, (,г,...,п.) являг ются результатами вычислений, а является значением вычисляемой цепной дроби. Работает предлагаемая цифровая моель следующим образом. Перед началом вычислений приращения At- отключаются и на входы 7 йнтегра торов 2 каждой группы К-того канала подаются Рк, а на входы & значения q, а регистры подынтегральной функции интеграторов 1, 4 записываются началбные значения (о&лчно нулевые). После этого на шину 6 подаются приращения tA , которые отключаются в тот момент, когда ду, . т.е. в момент дос- тижения требуемой точности вычислений. Использование решающих блоков цифгровых интегрирующих структур, а именно цифровых интеграторов и цифровых сумматоров, и объединение их в и идентичных дополнительных каналов позволяет получить быстродействующую, точную, однородную цифровую модель, удобную для изготовления на основе современной интегральной технологии. Формула изобретения Устройство для вычисления обыкновенных цепных дробей, содержащее основной канал, состоящий из интеграторов и сумматора, выход которого подключен ко входу приращения подынтегральной функции первого интегратора, выходы второго и третьего интегратора подсоединены к соответствующим входам сумматора, отличающееся тем/ что, с целью повышения быстродействия, в устройство введены п дополнительных каналоа, каждый из которых состоит из четырех интеграторов и сумматора, выход которого подключен ко входу приращения подынтегральной функции первого интегратора соответствующего канала, выходы второго, третьего и четвертого интеграторов подсоединены к соответствующим входам сумматора данного канала, инверсный выход первого интегратора подключен ко входам приращений независимой переменной третьего и четвертого интеграторов данного канала, входы приращений независимой переменной первого и второго интеграторов основного и дополнительных каналов подбоединены к входной шине независимой машинной переменной, вход приращений подынтег-ральной функции четвертого интегратора подключен к выходу сумматора последукйдего канала, инверсный выход первого интегратора основного канала подсоединен к входу приращений независимой переменной третьего интегратора.

выходы подынтегральной функции первого интегратора основного канала и первого интегратора дополнительных каналов являются соответствующими выходами устройства.

Источники информации, принятые во внимание при экспертизе:

1. ВгасКа-Вагас Атлог Appiicaitou oj:Conti uend fracttoTis jor faii evatuaUon -oj certaxTi functions O о dijitat сотп5 puter lEEl Tranb comput, 1974, C-23, 3, 301-309.

2. Авторское свидетельство СССР .217075, кл. 06J|1/0.2, 1967.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство вычисления цепных дробей | 1981 |

|

SU991425A1 |

| Устройство для вычисления цепных дробей | 1981 |

|

SU1008748A1 |

| Устройство для моделирования нейрона | 1979 |

|

SU883927A2 |

| Устройство для деления частоты пов-ТОРЕНия иМпульСОВ | 1979 |

|

SU817891A1 |

| Цифровой интегратор для воспроизведения многомерных функций | 1974 |

|

SU519736A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU409248A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Детерминированно-вероятностный цифровой интегратор | 1975 |

|

SU600574A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

f efв «f.

if 9

Авторы

Даты

1978-05-25—Публикация

1976-08-01—Подача