Изобретение относится к вычислительной технике. Известно устройст во вычисления цепных дробей, содержащее один канал, состоящий из- одного или нескольких цифровых интеграторов. Этот кансш последовательно используется для вычисления всех звеньев цепной дроби fl.

Недостатком такого устройства является малое быстродействие.

Наиболее близким по технической сущности к предложенному является цифровое специализированное устройство, предназначенное для параллельного вычисления обыкновенных цепных (Дробей

СО :

Оно содержит п-каналов, каждый из которых состоит из четырех цифровых интеграторов и трехвходовогр, комбинационного сумматора, выход которого подключен к входу приращений подынтегральной функции второго интегратора соответствукхдего канала, выходы пер,вого, третьего и четвертого интеграторо. подсоединены к входам сумматора данного канала, инверсный выход второго интегратора

подключен к входам -х риращений неза- висимой переменной третьего и четвертого интеграторов данного канала, входы приращений независимой переменной первого и второго интеграторов подсоеда1нены к входной шине независимой машинной переменной, вход приращений подынтегральной функции четвертого интегратора подключен

10 к выходу сумматора последующего канала, выходы подынтегральной функции вторых интеграторов являются соответствующигли выходами устройства, причем первый выход является основным. В

15 устройстве все звенья цепной дроби (1 вычисляются одновременно путем реализации в каждом К-ом канале слег дующего неоднородного разностного 51 уравнения

СчмГ- к.01 % кИ -Ркй1 W

УИ4-1 0.

где К 1, 2, 3,..

--./ J ffll I

Ранение уравнения ,2) имеет вид

25

K(,H)(KH)i- «VK tf+C4()PK, СЬ) где - значение yj. - при 1 0

30 обычно Уцо

Из выражения (З; видно, что если выполняется условие

.НЧЧи 1 +-ЧкМ| С4)

то при 1-«.%А+1)(, т.е. все подходящие дроби и сама у стремятся к значениям, определяемым соотношение (1). В свою очередь, неравенство (4 справедливо при выполнении условия

0 A.t wi-in 1(Чек.ч.1Я- -СУцГЛ :оторое определяет сходимость итерационного процесса (2 и одновременно определяет устойчивость реаизующей его цифровой модели. Из анализа неравенства (5 видно/ что устойчивость известного устройства ограничена. Действительно, если в вычисляемой дроби встетится хотя бы одно такое отрицательное значение Vn/ для которого

1Чк1М к+1)Л, ,.

где/( /VK-UJI - модули соответствующихвеличин, то условие устойчивости (5 к-го канала устройства будет нарушено, что приведет к неустойчивости всей модели 2j .

Последнее обстоятельство существенно сужает область устойчивости известного устройства и ограничивает его функциональные возможности, поскольку затрудняет его использование для вычисления цепных дробей (1) с произвольными значениями Ру.С)/ Кроме того, в известном устройстве каждый канал содержит лишний интегратор, используемый для формирования приращений VK. как следст-. вие, каждый сумматор содержит лишний вход, поскольку приращения 0 д t можно формировать одновременно с формированием приращений У, )i к iAt и использовать в каждом канале не. трёхвходовой,-а двухвходовой сумматор. Действительно, как видно из уравнения (2) величина 0, не зависит от i и может быть задана в качестве начальной в интегратор. Тогда в процессе вычислений в этом интеграторе будет динамически формироваться сум-,

.H.MM K--Vl)V

a на выходе этого интегратора будет формироваться произведение

))iut .

Цель изобретения - повышение устойчивости и упрощение конструкции устройства вычисления цепных дробей.

Поставленная цель достигается тем, что в устройстве, содержащем п каналов (.где п - количество членов цепной дроби;, каждЕфй из которых состоит из четырех интеграторов и сумматора, причем вход начального значения

подынтегральн9й функции первого интегратора подключен к входу значения первого слагаемого знаменателя соответствующего члена цепной дроби устройства, выход инверсии приращений

подынтегральной функции второго интегратора соединенс входом приращений независимой переменной первого интегратора, выход которого соединен с первым входом сумматора, второй

0 вход которого подключен к выходу

третьего интегратора, вход начальной установки которого соединен с входом числителя соответствующего члена цепной дроби устройства, вход прираще5 ния независимой переменной устройст ва подключен к входам приращений независимых переменных второго и третьего интеграторов, выход подынтегральной функции второго интегратора подQ ключен к выходу устройства, в каждом канале входы приращений подынтегральной функции первого и четвертого интеграторов подключены к вьоходу четвертого интегратора.последующего канала, выход приращений независимой переменной.четвертого интегратора соединен с выходом сумматора, выход этого интегратора подключен к входу приращений подынтегральной функции второго интегратора, а вход началь0 ного значения подынтегральной функции подключен к входу значения первого слагаемого знаменателя соответствующего члена цепной дроби устройства. На чертеже представлена структур5дная схема устройства вычисления цепных дробей.

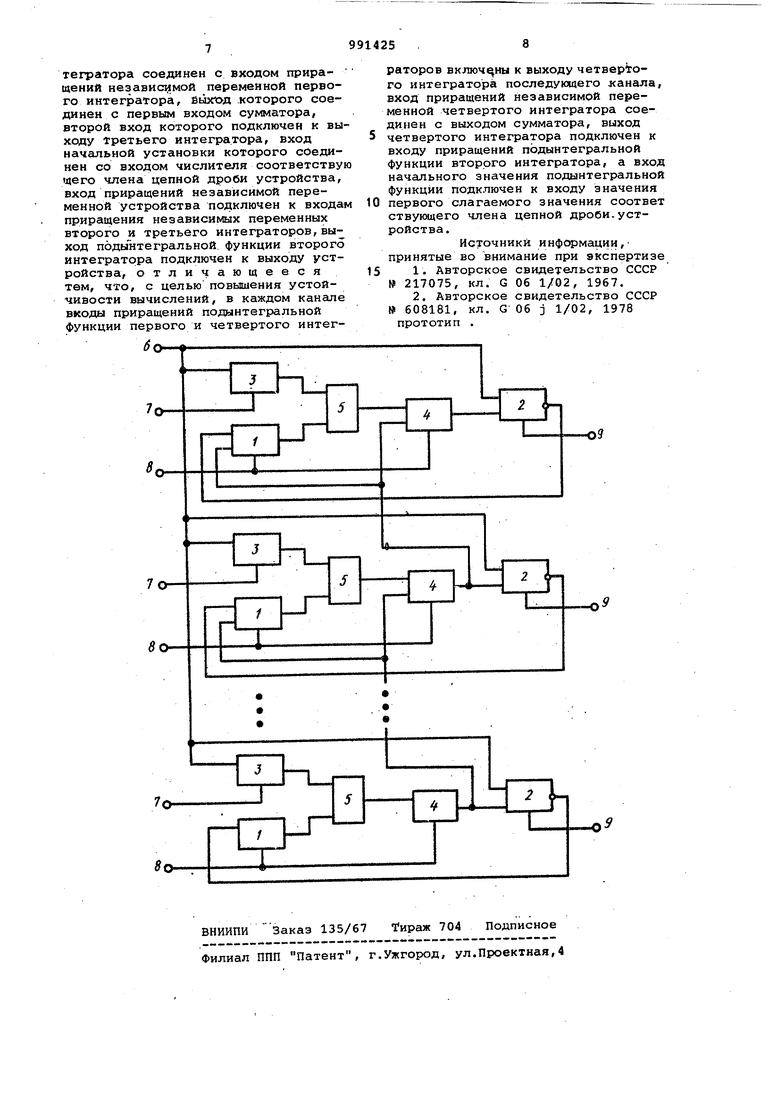

Устройство состоит из п-каналов, каждый из которых содержит интеграторы 1-4 и двухвходовой сумматор 5.

0 Шина б - шина приращения независимой машинной переменной At. На входы 7 постоянных коэффициентов поступают значения Р, на входы 8 постоянных коэффициентов поступают знаf чения ,,, шина 9-- выходная шина.

Выходы интеграторов 3-4 соединены с соответствующими входами сумматора 5. Выход сумматора 5 соединен с входом приращений независимой переменной интегратора 1, выход которого соединен со входом приращений подынтегральной функции интегратора 2. Инверсный выход интегратора 2 соединен с входом приращений независимой переменной интегратора 4, вход

5 подынтегральной функции которого

объединен с аналогичным входом интегратора 1 и подсоединен к шине 8 постоянных коэффициентов, а входы приращений подынтегральных функций этих

0 интеграторов также объединены и под. соединены к выходу первого интегратора последующего канала. С выходов 9 подынтегральных функций интеграторов 2 всех каналов снимаются резуль5 таты вычислений. Причем с верхнего выхода 9 снимается искомое значение у цепной дроби (.1), ас выходов 9 о тальных каналов снимаются значения соответствующих подходящих дробей. В устройстве все звенья цепной дроби . 1 ) вычисляются одновременно путем параллельного решения системы неоднородных разностных уравне fK(.Ui))i V Kiu-t PK -b CY K+,) к-п.ъ.-.и, Чин- 0,4--о,1,..,е. Записывая решение системы (6 ) для К-го канала, получим (к1и.Аг(со-(СкмН Я/кГР 0-СУ к..)к)/ tfVi4tK.,).{V ЗЛз равенства (7) следует, что уеловне устойчивости для предлагаемого устройства имеет вид - - - ,)) Следовательно, если выбирать шаг ,At из условия o At vviiiHaCY t+i)-i Ягк)Т С«; 1ч. Т-, то Вычислительный процесс в предлагаемом устройстве будет устойчивым при любых знаках коэффициентов Cj., поскольку в этом случае всегда Wtt.iM Vtj-O, По этой причине устойчивость предл гаемого устройства бущественно выш чем у известного. Если величина ша га At удовлетворяет условию (8, т итерационный процесс (6) сходится при любых знаках коэффициентов Р| . Иными словами, начиная с некот рого значения i Е выполняется не венство (Ui)cr, (9) где (CVvoi K.) - заданна погрешность вычисления цепной дроби ; (5 -погрешность вычислений в устройстве. Работает устройство следующим об разом. Перед началом вычислений приращения At отключаются и на входы 7 и теграторов 3 К-го канала подаются соответствующие значения Р, а. на входы 8 подаются значения q,. В регистры подынтегральной функции интегратора 2 записываются нулевые наI чальные условия.После этого на шину б подаются приращения&t.На выходе инте ратора 3 К-го канала появляются при ращения Рц At, которые суммируются в сумматора 5 с приращениями (9(lJ + K) поступёисщими с выхрда интегратора 4. Ввиду того, что в регистре подынтегральной функции ийт гратора 1 формируются величины 5(и41),-Як f а на вход приращений независимой переменной этого интегратора с выхода сумматора 5 поступает сумма-у A-tCVK(444)).b-b ,на выходе интегратора 4 образуются приращения определяемые выражением (б) .Эти при ращения поступают на вход приращений подынтегральной функции интегратора 2, накапливаются в этом интеграторе и используются для формирования выходных приращений V(c,- ut , которые по цепи обратной связи с инверсного выхода интегратора 2 поступают н.а вход независимой переменной интегратора 1. Аналогичные процессы протекают в каждом : i-м итерационном цикле вычислёний (1 0, 1, 2, ..., Е . После достижения требуемой тояности вычислений, определяемой соотношением (9) для первого канала (лу f -fief) , приращения.Atотключаются, и содержимое регистра подынтегральной интегратора 2 первого канала считывается с выхода 9 как искомое значение вычисляемой цепной дроби (1), а содержимое регистров подынтегральной функции интеграторов 2 остальных каналов считывается как начения соответствующих подходящих Дфобей. Использование в каждом канале двухвходового сумматора вместо трехвходового и сокращение оборудования каждого канала на один интегратор упрощает конструкцию устройства и повышает его надежность, а введение в каждый канал дополнительного интегратора увеличивает его устойчивость, последнее обстоятельство существенно расширяет функциональные возможности устройства, поскольку позволяет использовать его для вычисления цепных дробей (1) не только с положительными, но и с отрицательными значениями коэффициентов Р| , )., а также упрощает подготовку устройства к работе, так как исключает необходимость в априорном исследовании цепнбй дроби и таком ее преобразовании, при котором возможно ее решение на известном устройстве. Формула изобретения Устройство для вычисления цепных дробей, содержащее п-каналов { где п - количество членов цепной дроби, каждый из которых состоит из четырех интеграторов и сумматора, причем вход начального значения подынтегральной функции первого интегратора подключен к входу значения первого слагаемого знаменателя соответствующего члена цепной дроби устройства, выход инверсии приращений подынтегральной функции второго ин

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления обыкновенных цепных дробей | 1976 |

|

SU608181A1 |

| Устройство для вычисления цепных дробей | 1981 |

|

SU1008748A1 |

| Устройство для вычисления обратной функции | 1982 |

|

SU1137478A1 |

| Цифровой интегратор | 1979 |

|

SU805362A1 |

| Интегрирующее устройство | 1978 |

|

SU781849A1 |

| Устройство для деления частоты пов-ТОРЕНия иМпульСОВ | 1979 |

|

SU817891A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU409248A1 |

| Модель адаптивного нейрона | 1978 |

|

SU765823A1 |

| ИНТЕГРАТОР ДЛЯ ПАРАЛЛЕЛЬНОЙ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ МАШИНЫ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1973 |

|

SU388278A1 |

| Устройство для моделирования нейрона | 1977 |

|

SU682910A1 |

Авторы

Даты

1983-01-23—Публикация

1981-04-10—Подача