Дится ИзоытоЧность 3 схему для зааержк-и к в колечнОМ счете согласаза1н;ия ояг.налОЗ.

В лопичаокон схеме из-за наличия :неист1|ра;вностей возможны различные случаи .ис к;ажения сигналов л 3 :лерзую очарадь лскаясенс ьч, цроявляющиеся з том, что в.место логического нуля формируется логическая еди-ш-ща, и наоборот.

В известном устройстве ампл;итудный селектор прОпускает лишь те сирналы, котОрые удовлетзаряют задаваемым nporipa iMHO требова|Н-ия,м по амплитуде. Сладователько прелиТола.гается ,наперед :известны)м по крайней мере логич-еское значен1ие контролируемого сигнала. Это может дризести, например, к тому, что вместо ожидаемого логического нуля гаастуиит искаженлая eдиiHlИцa, и эта леиспраанасть не будет обнаружена.

Цель изобретения - повышение полноты контроля.

Постазл&нная цель достигается тем, что з устройство введен блок форМ11фоза1н;ия кода реакции, прячем входы устройства ч:ерез блок nopOifOBbix элемантов соединены с первым входам блока фо1рмирован1ия кода реакци-и. Парвый и второй входы блока .времелиой селекцни соединены ссо1тзетстзенно с третьим выходок бло«а управления 1И с пятьпм выходом 6vTOiKa опвр:ативной памяти. Выходы блока времвн,ноп селекции СоедИ1наны соответственно с входом блока .пороговых элементов и с вторым входом блока форм:и(р.о зан:ия кода реакции, выход которого сооинек с вторым входом блока выявления .нейСПр ав;костей.

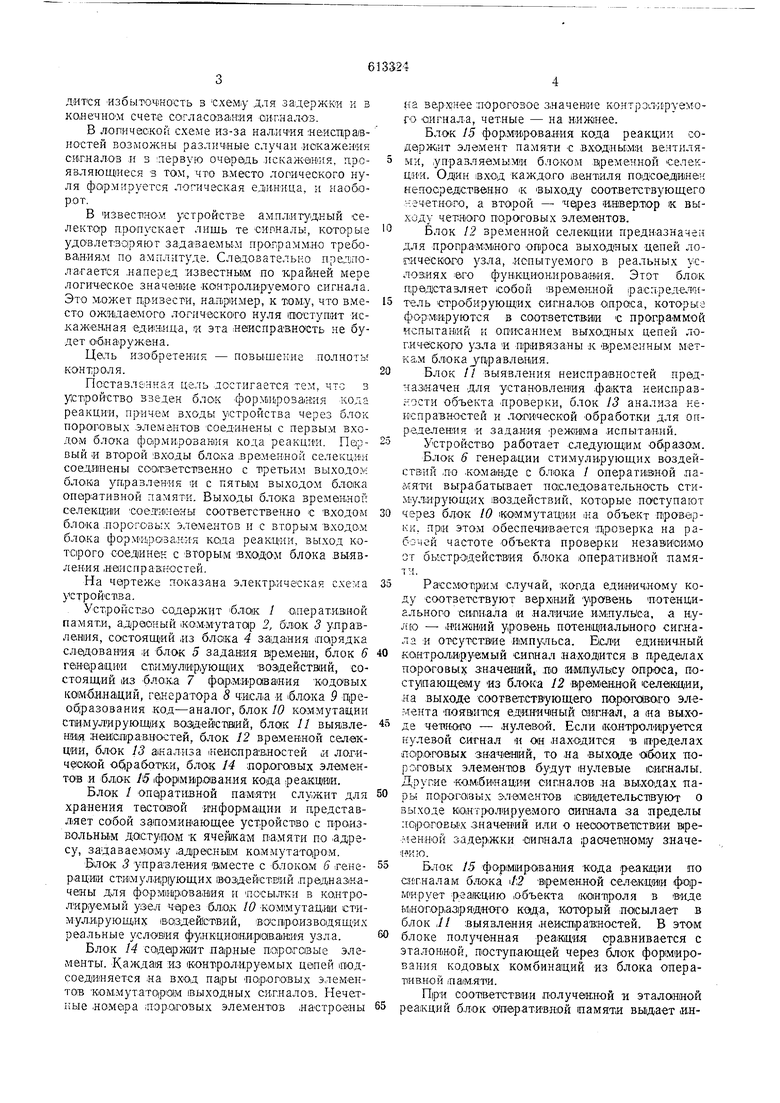

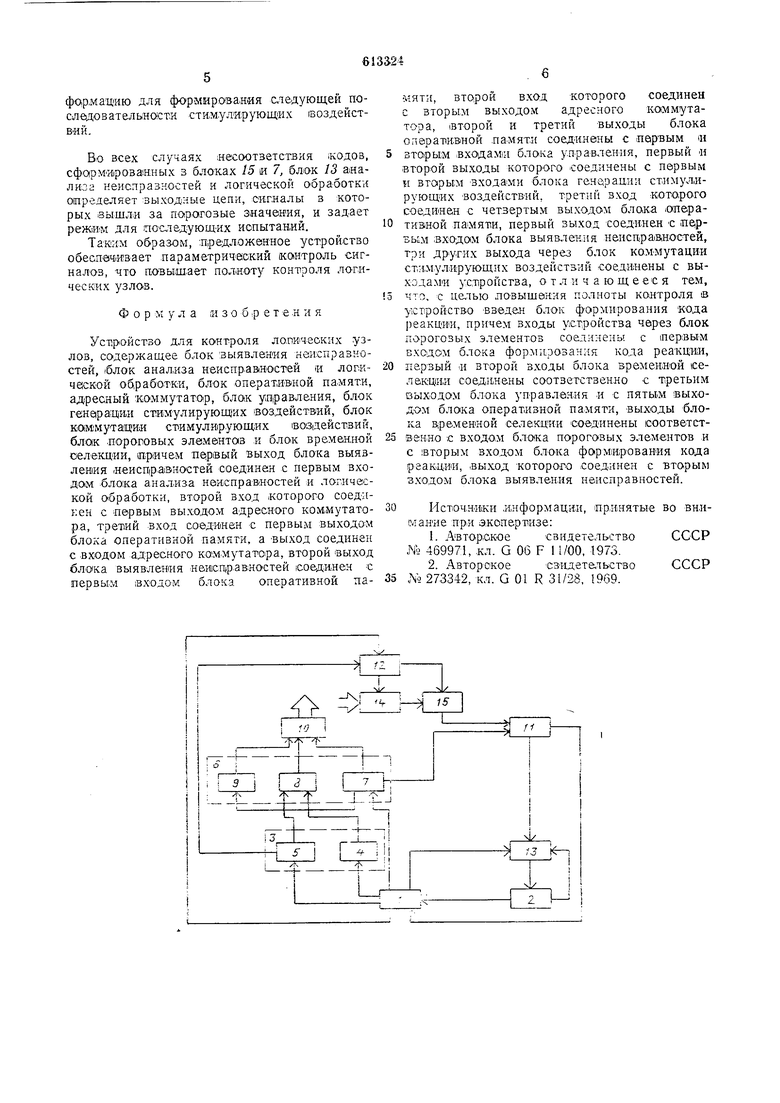

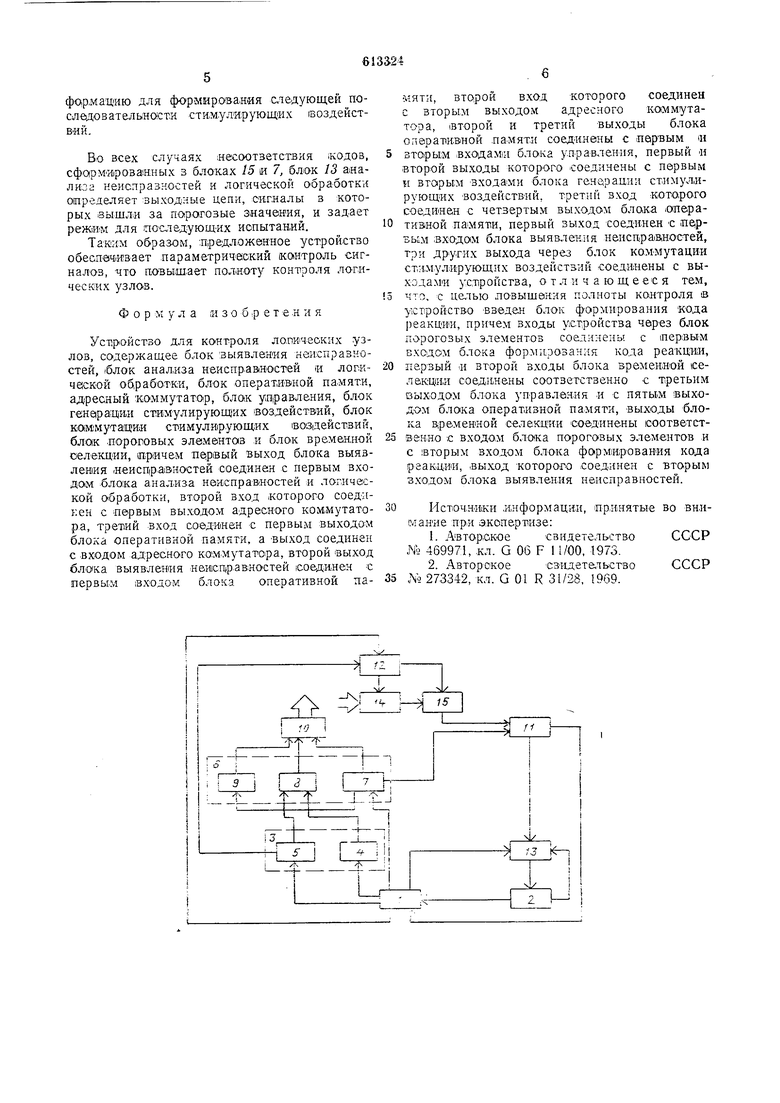

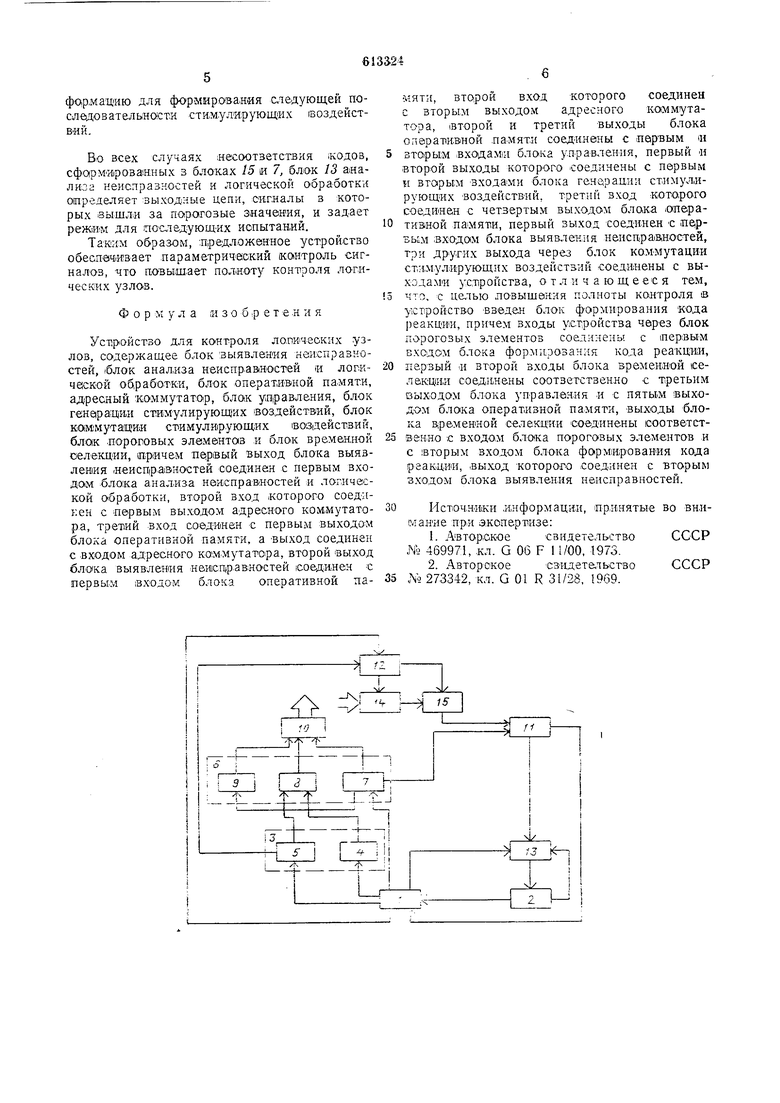

На чертеже показана электрическая схема устройст1ва.

Устройстз-о содержит блок / операткз1ной памяти, адресный жоммутатар 2, бло1К 3 управления, состоящий из блока 4 3:а да1ния иарядка сл едования и блок 5 задавия времени, блок 6 геяерациИ стимулирующих воэдействий, состоящий из блоха 7 формираващия кодовых 1С01Мби.наций, генератора 8 числа и (блока 5 цреооразования код-аналог, блок/(9 коммутации стимулирующих во13йеЙ1Спаий, блак 11 выявлени1я ;неи1с;П1р,ав.цостей, блок 12 времен1Н10Й селекции, блок 13 анализа 1неиоправлостей и логической об|работки, блок / пороговых элементов и блок Ш формирования кода реакции.

Блок / опе|рати;вной памяти служит для хранения тестовой инфорадации и представляет собой заиомивающее устройство с произвольным д«с:туао1м К ячейкам па.мяти по Зд ресу, задаваемому лд1ресны1м ко,ммутатО|ром.

Блок 3 упразления вместе с блоком 6 темерацим сти1мул.и;р|ующих воздействий лредназ ачены для формийрования и илссылки в контролируемый узел Че|рез блок 10 KOMiMyTauniH стимулирующих 1В-о.здей1ствий, восшроизво/дяших реальные условия функцианираздня я узла.

Блок 14 со|Д9рж1ит парны-е варогазые элементы. Каждая из 1конт1ролируемых цепей шодсоеднняется иа вход па|ры П01роговых элементов KOMiMyTaTOipioiM выходных сигналов. Нечетные ломера ;порО|Гозых элементов .настроены

на вер-хнее пороговое значение контрОЛ;1руемог-о сигнал-а, четные - на нижиее.

Блок i5 фор|МИ1розания кода реакции содержит элемент памяти с входньсми вент15лями, управляемыми блоком В)ремен.ной селекциИ, Од1ин вх€д каждого 1вентиля П01дсоед н1нек непосрежтвенно « выходу соответствующего нечетнОГО, а второй - через йнвер:т10р к выходу четкого пороговых элементов.

Блок 12 временной селекции предн:азначен для nponp.a M;MiHoro onipoca выходных цепей лорического узла, испытуемого в реальных условиях его фу акционирования. Этот представляет собой временной распред-е-титель строби:рующих сигналов опроса, которые формируются в соответствии € программой испытан1Ий к описанием выходных цепей логическо-го узла и привязаны к Беременным меткам блока уп(равлбния.

Блок // выявления неисправностей предназначен для установления факта неисправгости объекта проверки, блок / анализа неисправностей и логи ческой обработки для определеш1я и задания режима испытаний.

Устройство работает следующим образом.

Блок 6 генерации стимулирующих воздейстВИЙ ,по команде с блока / операти:вной памяти вырабатывает последовательность стимулирующих воздействий, которые поступают через блок W 1коадмутаци:и на объект шрозеркк, при этом обеспечивается дроверка на рабочей частоте объекта проверки незав ИОимо от быстр-здейстзия блока оперативной ламяPaccMOT.piHM случай, когда единичному коду соответствуют верхний уровень потенциального ояпн-ала и наличие нм пулыса, а н,укк - 11ГИЖНИЙ уровень потевцмалыного сигнала и отсутств ие ампульса. Бели единичный контролируемый сипнал наход ится в пределах пороговыз зн-аченяк, ло импульсу опроса, постунающвму ИЗ блока 12 «ременной с-елеюции, на выходе соответствующего порогаваго элемента ПОЯВИТСЯ еди№ИЧ1Ный оигЛЭЛ, а «а выходе че-рн.ого - .нулеВОй. Если кон-тролдаруется нулевой сигнал iH он на.ХОдится В гоределах пороговых зНач1ен1ий, то На Выхояе абоих порСГовых элем-внт10в будут нулевые сигналы. Другие ко.м.бинациИ сигналов на выходах ттарь порог01зых ЭЛаментов юзидетельствуют о выходе контролируемого аипнала за лороговых значений или о неаоот&ет( Bipeменной задержки Оилнала 1раачет1НОму значеWKO.

Блок /5 формирования кода реакции по си:гналам блока /.2 временной се«1екци1И фармирует -реакцию объекта 1К10нт1роля в Виде М|НОгор,аз)ряд1НОго код-а, который Лосылает в блок ,// выявления .неИСИравлостей. В это1М блоке получанная реакция сравнивается с эталонной, поступающей через блок формирования кодовых комбинаций из блока оперативной ,па1М.ят1и.

Нри ооот ветств ии ПОлучекной и эталонной реакций блок оибративной памяти выдает анфо,р,мащию для формирозания следующей поел адов ат ел ьности стимулирующих воздействий.

Во всех случаях «ессютветствия кодов, сформированных з блоках 15 и 7, блок 13 анализа кеиспразностей и логической обработки определяет выходные цепи, сигналы з которых вышли за пороговые значения, и задает режвм для последующ-их испытаний.

Таклм обраэом, лредложвнное устройство обеспечивает параметрич е ск;ий контроль сигналов, что аовыш.ает полноту контроля лотичесюкх узлов.

Фор м у л а и 3 о б :р е т е .к и я

Ус-пройстзо для контроля лопичеоких узлов, содержащее блок выявления неисправностей, |блок анализа неиспр.ав(ностей и логической обработки, блок оперативной па.мят.и, адресный коммутатор, блок уцравления, блок гене|ра;П(Ии стимулирующих воздействий, блок каммутащии стимули1руюЩ|ИХ воздействий, блок .пороговых элементов и блок временной селекции, тричем пе р1вый выход блока выявлен1ия (Неисправностей соединен с первым входам блока анализа неисправиостей и логической обработки, второй вход которого соединен с первым выходом адресного коммутатор.а, третий вход соединен с первым выходом блока оперативной памяти, а Выход соединен с входом адресного кам мутатора, второй выход бло1ка выявления «еи1СП(рав.ностей соединен с первы м входом блока оперативной иамяти, второй вход которого соединен с вторым выходом адресного коммутатора, второй и третий выходы блока оперативной па-мяти соединены с парвым и вторым входам1И блока управления, первый « второй выходы которого соединены с первым и вторы;м входами блока генерации стимулирующих воздействий, третий вход которого соединен с четвертым выходом блока оперативной памяти, первый выход соединен € iie,pБЫ.М ;входом блока выявления неиспрааностей, три других выхода через блок коммутации стимулирующих воздействий соединены с выходами устройства, отличающееся тем, что, с иелью ловышекия полноты кантроля в устройство введен блок формирования кода реакции, причем входы устройства через блок пороговых элементов соединены с первым входом блока формирования кода реакции, первый и второй входы блока временной iceлекЦаш соединены соответственно с третьим выходом блока управления и с пятым выходом блока оперативной , выходы блока в;ремен1ной с-елекции соединены соответствен.но ;с входом блока пороговых элементов и с вторым входом блока форм ирования кода реакции, выход которого соединен с вторым входом блока выявления неисправностей.

0 Источ.ники .информации, пр.инятые во вникание при экспертизе:

1.Авторское свидетельство СССР № 46997:1, .кл. G 06 F 1 1/00, 1973.

2.Авторское свидетельствоСССР 5 № 273342, кл. G 01 R 31/28, 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля логических узлов | 1973 |

|

SU469971A1 |

| Устройство для контроля логических узлов | 1976 |

|

SU612247A2 |

| Устройство для контроля логических узлов | 1978 |

|

SU666544A2 |

| Устройство для контроля логическихузлОВ | 1978 |

|

SU813431A2 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для диагностирования логических узлов | 1979 |

|

SU892447A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU991430A1 |

| Устройство для контроля адресных цепей боков памяти | 1985 |

|

SU1274007A1 |

Авторы

Даты

1978-06-30—Публикация

1976-03-16—Подача