1

Изобретение относится к запоминающим устройствам.

Известны устройства для контроля блоков постоянной памяти 1, 2.

Одно из известны.х устройств использует принцип сравпення данных, содержащихся в контролируемой памяти, с данными, имеющимися в эталонной памяти 1. В нем схема задержки воздействует на входной и выходной регистры. При этом проверка правильности работы выходного регистра осуществляется с определенным запаздыванием по отношению к проверке входного регистра. Устройство содержит в своем составе эталонную память с быстродействием, равным или более высоким, чем у проверяемого блока иостоянной памяти, и имеет ограничения по времени работы.

Наиболее близким техническим рещением к пзобретеиию является устройство для контроля блоков постоянной памяти, содержащее дещифратор команд, подключенный к счетчику адреса и блоку управления, соединенному с блоком задания программы, блоки приема и выдачи чисел 2. Реальная частота проверки блоков постоянной памяти этим устройством оиределяется быстродействием блока задания программы, которое значительно ннже максимальной рабочей частоты контролируемого блока постоянной памяти; устройство не предусматривает возможности автоматической регистрацни результатов контроля и, следовательно, не обеспечивает требуемого быстродействия и достовериости контроля блоков постоянной памяти.

Пель изобретения - увеличение быстродействия устройства.

Это достигается тем, что в устройство введены дополнительный счетчик и регистр контрольной пнформаци, вход и выход которого

подключены соответственно к выходу блока приема чисел и одному из входов блока выдачи чисел, другим входом соединенного с выходом дешифратора команд, вход дополнительного счетчика подключен к выходу блока

управления, а выходы дополнительного счетчика соединены соответственно с входами блока приема чисел и блока управления. Устройство контроля постояииых запоминающих блоков соединяется с малой серийной ЦВМ каналами выдачи и приема числовой контрольной информации, каналом выдачи команд.

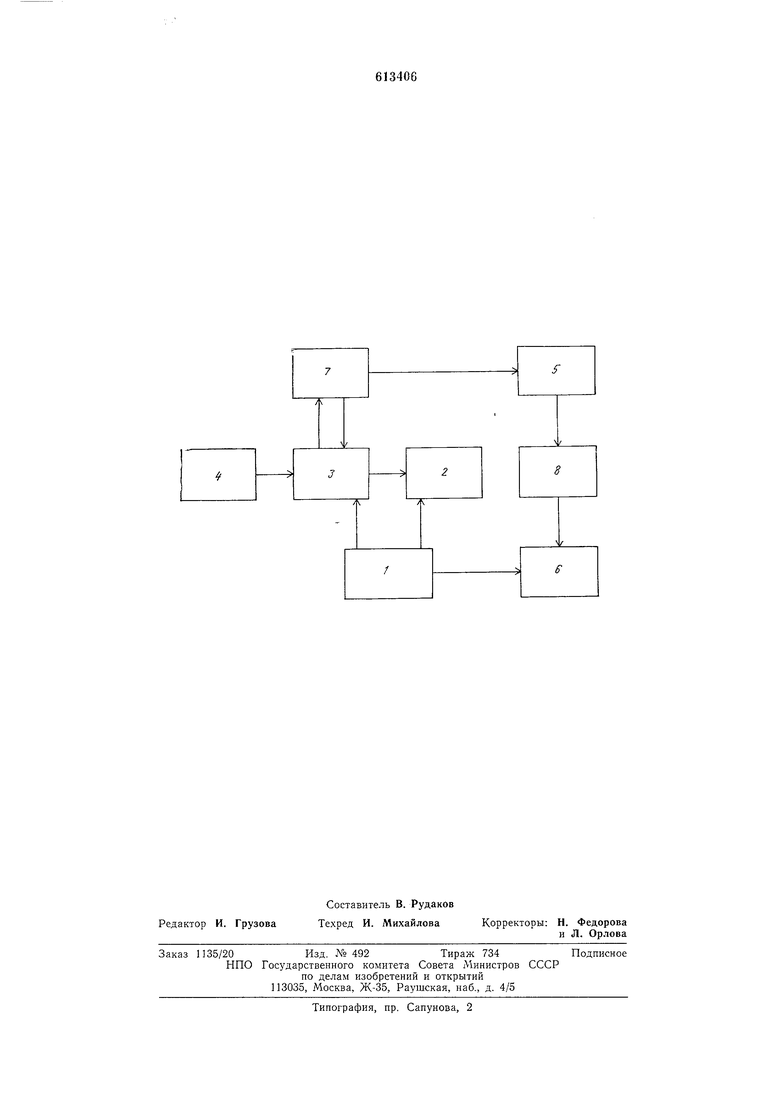

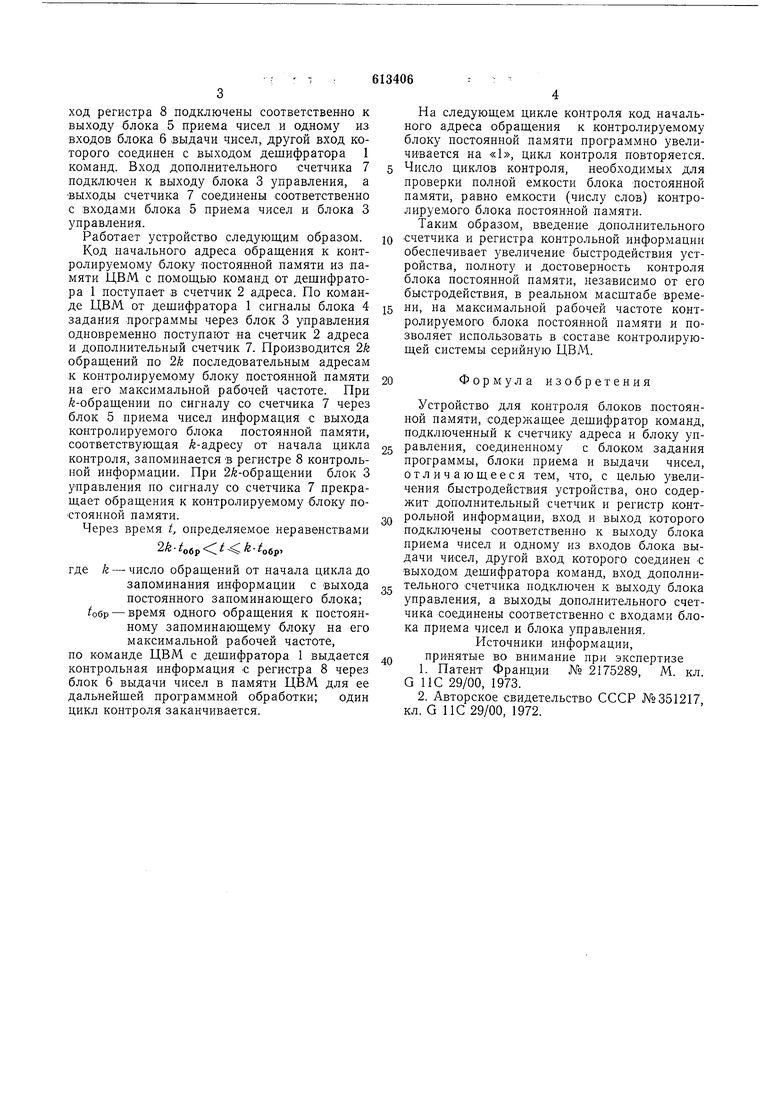

На чертеже представлена структурная схема предлагаемого устройства. Устройство для контроля блоков постоянной

памяти содержит дещифратор 1 команд, подключенный к счетчику 2 адреса п блоку 3 управления, соединенному с блоком 4 задания ирограммы, блок 5 ириема чисел и блок 6 -выдачи чисел, дополнптельный счетчик 7 и регистр 8 контрольной информации. Вход и выход регистра 8 подключены соответственно к выходу блока 5 приема чисел и одному из входов блока 6 выдачи чисел, другой вход которого соединен с выходом дешифратора 1 команд. Вход дополнительного Счетчика 7 подключен к выходу блока 3 управления, а выходы счетчика 7 соединены соответственно с входами блока 5 приема чисел и блока 3 управления.

Работает устройство следующим образом.

Код начального адреса обращения к контролируемому блоку постоянной памяти из памяти ЦВМ с помощью команд от дешифратора 1 поступает в счетчик 2 адреса. По команде ЦВМ от дешифратора 1 сигналы блока 4 задания программы через блок 3 управления одновременно поступают на счетчик 2 адреса и дополнительный счетчик 7. Производится 2 обращений по 2k последовательным адресам к контролируемому блоку постоянной памяти на его максимальной рабочей частоте. При -обращении по сигналу со счетчика 7 через блок 5 приема чисел информация € выхода контролируемого блока постоянной -памяти, соответствующая А-адресу от начала цикла контроля, запоминается в регистре 8 контрольной информации. При 2й-обращении блок 3 управления по сигналу со счетчика 7 прекращает обращения к контролируемому блоку постоянной памяти.

Через время t, определяемое неравенствами

.

где k - число обращений от начала цикла до запоминания информации с выхода постоянного запоминающего блока; обр - время одного обращения к постоянному запоминающему блоку на его максимальной рабочей частоте, по команде ЦВМ с дешифратора 1 выдается контрольная информация с регистра 8 через блок 6 выдачи чисел в памяти ЦВМ для ее дальнейшей программной обработки; один цикл контроля заканчивается.

На следующем цикле контроля код начального адреса обращения к контролируемому блоку постоянной памяти программно увеличивается на «1, цикл контроля повторяется.

Число циклов контроля, необходимых для проверки полной емкости блока достоянной памяти, равно емкости (числу слов) контролируемого блока постоянной памяти. Таким образом, введение дополнительного

счетчика и регистра контрольной информации обеспечивает увеличение быстродействия устройства, полноту и достоверность контроля блока постоянной памяти, независимо от его быстродействия, в реальном масштабе времени, на максимальной рабочей частоте контролируемого блока постоянной памяти и позволяет использовать в составе контролирующей системы серийную ЦВМ.

Формула изобретения

Устройство для контроля блоков постоянной памяти, содержащее дешифратор команд, подключенный к счетчику адреса и блоку управления, соединенному с блоком задания программы, блоки приема и выдачи чисел, отличающееся тем, что, с целью увеличения быстродействия устройства, оно содержит дополнительный счетчик и регистр контрольной информации, вход и выход которого подключены соответственно к выходу блока приема чисел и одному из входов блока выдачи чисел, другой вход которого соединен с выходом дешифратора команд, вход дополнительного счетчика подключен к выходу блока управления, а выходы дополнительного счетчика соединены соответственно с входами блока приема чисел и блока управления. Источники информации,

принятые во внимание при экспертизе

1.Патент Франции № 2175289, М. кл. G ПС 29/00, 1973.

2.Авторское свидетельство СССР №351217 кл. G ПС 29/00, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоковпОСТОяННОй пАМяТи | 1979 |

|

SU824318A1 |

| Устройство для контроля блоков постоянной памяти | 1982 |

|

SU1049984A1 |

| Устройство для контроля оперативнойпАМяТи | 1978 |

|

SU822297A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Устройство для контроля постоянной памяти | 1977 |

|

SU693442A1 |

| Устройство для тестового контроля блоков памяти | 1988 |

|

SU1541678A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1619284A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Микропроцессор для вводавывода данных | 1976 |

|

SU618733A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

Авторы

Даты

1978-06-30—Публикация

1976-10-04—Подача