1

Изобретение относится к запомина ющим уст.ррйствам.

Известно устройство для контроля оперативной памяти, содержащее счетчик адреса, соединенный с адресными входами накопителя, регистры числа, подключенные к числовым входам накопителя, логические схемы, элементы задержки, схемы фиксации ошибки, регистры управления и контроля и одноразрядный счетчик 1.

Недостатками этого устройства являются большие аппаратурные затраты и малая эффективность контроля.

Наиболее близким техническим решением к предлагаемому изобретению является устройство для контроля оперативной памяти, содержащее блок згшания прогрс1ммы, блрк управления, счетчик, первый регистр числа, блок местного управления, дешифратор команд, блок приема чисел,, второй регистр числа и блок вьадачи чисел, причем первый и второй входы блока управления подключены соответственн к выходу блока задания программы и первому ВЕлходу дешифратора команд, первый и второй выходы блока управления соединены соответственно с певыми входами счетчика и первого регистра числа, второй, третий и четвертый выходы дешифратора команд подключены соответственно ко второму входу счетчика, входу блока местного управления и второму входу первого, регистра числа, третий вход которого соединен с первым выходом блока местного управления, второй выход которого подключен к первому входу блока приема чисел, вход второго регистра числа соединен с выходом блока приема чисел, а выход - с первым входом блока выдачи чисел,второй вход которого подключен к пятому выходу дешифратора команд 2.

Однако это устройство не обеспечивает эффективности контроля оперативных блоков памяти по всему набору контролирующих тестов, а также не позволяет использовать его в составе автоматизированной контролирующей системы с использованием малой ЦВМ. Указанные недостатки снижают надежность устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что устройство.содержит допопнительный счетчик, вход которого подк.пючен к первому выходу блока управения, первый выход - к третьему вхоу блока управления, второй выход четвертому входу первого регистра исла, третий выход дополнительного четчика соединен со вторым входом лока приема чисел.

Устройство соединяется с малой ВМ.каналами приема и выдачи числоой информации, а также каналом переачи командной информации.

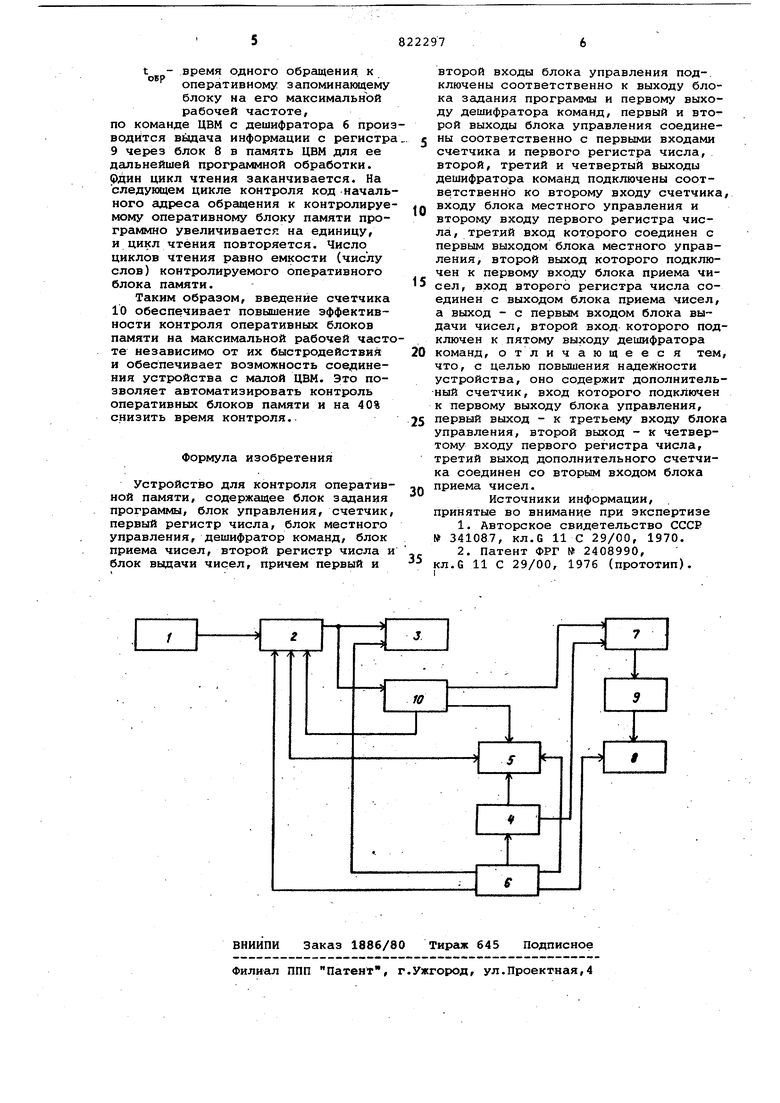

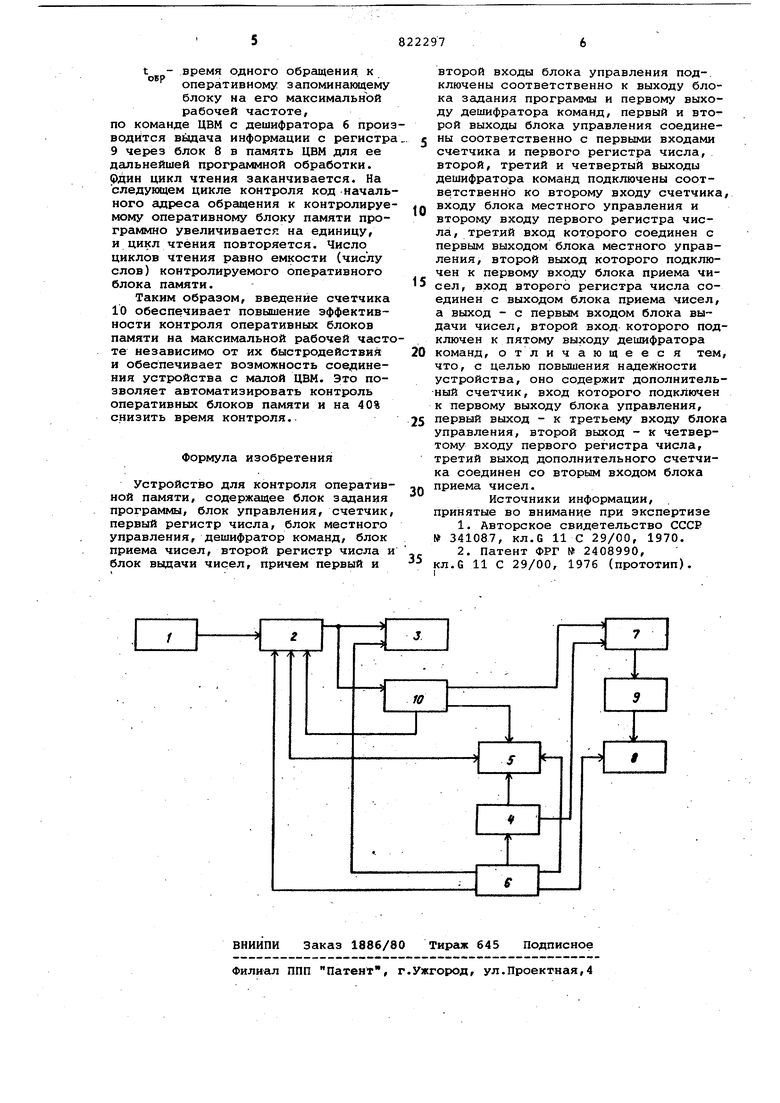

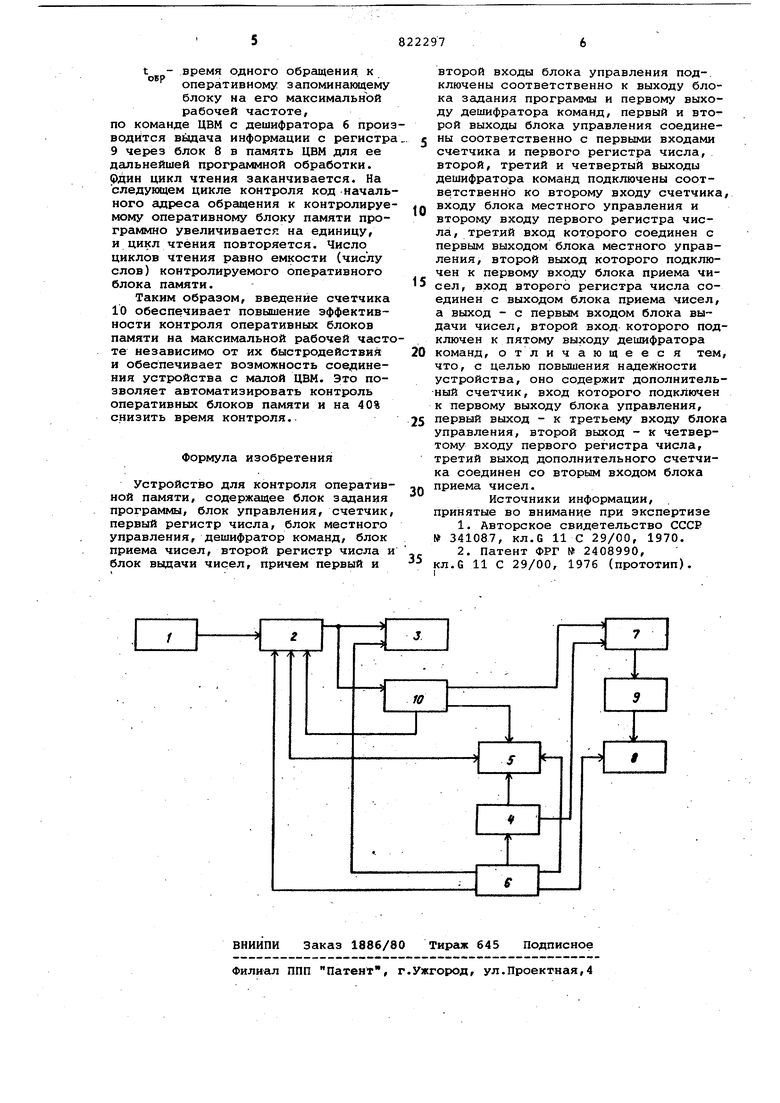

На чертеже представлена блок-схеа предложенного устройства.

Схема устройства содержит блок 1 задания программы, блок 2 управления, счетчик 3, блок 4 местного управления, служащий для управления записью, первый регистр 5 числа, дешифратор 6 команд, блок 7 приема чисел, блок 8 выдачи чисел, второй регистр 9 числа, дополнительный счетчик 10.

Первый и второй входы блока 2 подключены соответственно к выходу блока 1 и первому выходу дешифратора 6. Первый и второй выходы блока 2 соединены соответственно с первыми входами счетчика 3 и регистра 5.- Второй, третий и четвертый выходы дешифратора 6 подключены соответственно ко второму входу счетчика 3, входу блока 4 и второму входу регистра 5, третий вход которого соединен с первым выходом блока 4, второй выход которого подключен к первому входу блока 7. Вход регистра 9 соединен с выходом блока 7, а выход - с первым входом блока 8, второй вход которого подключен к пятому выходу дешифратора 6. Вход счетчика 10 подключен к первому выходу блока 2, первый выход - к третьему входу блока 2, второй выход - к четвертому входу регистра 5, третий выход - ко второму входу блока 7.

Устройство работает следующим образом. .

Режим записи. Код начального адреса обреидения к контролируемому оперативному блоку памяти из ЦВМ с по.мощью команд от дешифратора б поступает в счетчик 3. Код записываемого числа поступает в регистр 5 числа, По команде ЦВМ сигнал с выхода дешифратора б поступает на вход блока 4. Сигнал с первого выхода блока 4 поступает на один из входов регистра 5 числа, разрешая его работу, сигнал со второго выхода блока 4 поступает на один из входов блока 1, запрещая его работу. .

По команде ЦВМ от дешифратора 6 сигналы с выхода блока 1 через блок 2 одновременно поступают да входы счетчиков 3 и 10. Производится 2 К обращений по 2 К последовательным адpecciMK контролируемому оперативному блоку памяти на его максимальной рабочей частоте. При К-м обргцдении си,гнал с выхода счетчика 10 разрешает вцдачу кодов числа с регистра 5. По

сигналу с блока 1,поступающему через блок 2 на один из входов регистра 5,1 код записываемого числа с выхода регистра 5 поступает на контролируемый оперативный блок памяти. При 2 К-м обращении блок 2 по сигналу с выхода счетчика 10 прекращает обращение к контролируемому оперативному блоку памяти. Один цикл записи заканчивается. На следующем цикле код начального адреса обращения к контролируемому оперативному блоку . памяти программно увеличивается на единицу. .

Через время t , определяемое неравенством

t 2 К

-оер

где К - число обращений от начала цикла до записи кода числа в контролируемый оперативный блок памяти; время одного обращения к

ОБр оперативному блоку памяти на его максимальной рабочей частоте, цикл записи повторяется.

Число циклов записи равно емкости (числу слов) контролируемого оперативного блока памяти.

Режим чтения. Код начального адреса обращения к контролируемому оперативному блоку памяти из ЦВМ с помощью команд от дешифратора б по.ступает в .счетчик 3. По команде ЦВМ сигнал с выхода дешифратора б поступает на вход блока 4. Сигнал с первого выхода блока 4 поступает на один из входов регистра 5, запрещая его работу, сигнсШ со второго выхода блока 4 поступает на один из входов блока 7, запрещая его работу.

По команде ЦВМ от дешифратора б сигналы с выхода блока 1 через блок 2 одновременно поступают на входы счетчиков 3 и 10. Производится 2 К обращений по 2 К последовательным адресам к контролируемому оперативному блоку памяти на его максимальной рабочей частоте. При К-м обращении по сигналу со счетчика 10 через блок 7 информация с выхода контролируемого оперативного блока памяти, соответствующая К-му адресу от начала цикла контроля, запоминается в регистре 9.

При 2 К-м Обращении блок 2 по сигналу со счетчика 10 прекращает обращение к контролируемому оперативному блоку памяти.

Через время t , определяемое неравенствами

2K-t,

t К

Овр - IOBP

где к - число обращений от начала

цикла до запоминания информации с выхода оперативного блока памяти;

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Устройство для контроля блоков постоянной памяти | 1982 |

|

SU1049984A1 |

| Устройство для контроля блоковпОСТОяННОй пАМяТи | 1979 |

|

SU824318A1 |

| Устройство для контроля блоков постоянной памяти | 1976 |

|

SU613406A1 |

| Устройство для контроля постоянной памяти | 1977 |

|

SU693442A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для отладки программ | 1988 |

|

SU1552190A2 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1619284A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для контроля хода программ ЭВМ | 1987 |

|

SU1430960A1 |

Авторы

Даты

1981-04-15—Публикация

1978-05-04—Подача