, . Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано при. изготовлении и испыта НИИ блоков постоянной памяти. ; Известно устройство, содержащее считывающий блок, подключ.енный к вхо дам блока управления и регистра адреса, и блок сравнения, счетчик и сумматор, входы которого подключены к выходам, регистра адреса и одним входам блока сравнения, а выходы к входам счетчика, выходы которого соединены с другими входами блока сравнения, выход которого подключен, к блоку управления Щ Однако устройство содержит в своем составе считывающий блок, что они жает быстродействие устройства. Кроме того, недостатком я.вляется отсутствие схем, позволяющих использовать устройство в составе автоматизирован ной контролирующей системы с использованием малой ЦВМ. Наиболее близким к .предлагаемому по технической сущности является уст ройство, содержащее дешифратор команд, подключенный к счетчику адреса и блоку управления, соединенному с блоком задания программы, блоки прйе ма и выдачи чисел, дополнительный .счетчик и регистр контрольной информации, вход и выход,которого подключены соответственно к выходу блока приема чисел и одному из входов блока выдачи чисел, другой вход которого соединен с выходом дешифратора команд, вход дополнительного счетчика подключен, к выходу блока управ тения, а выходы дополнительного счетчика соединены соответственно с входами блока приема чисел и блока управления 2 . Однако устройство содержит в своем составе один регистр контрольной информации, что позволяет принимать на контроль только одно число в течение цикла контроля и требует для полной проверки блока постоянной памяти проведения, N циклов контроля, где N-емкость (число слов) контролируемого блока постоянной памяти, что снижает быстродействие устройства. Цель изобретения - увеличение быстродействия устройства и повышение достоверности контроля блоков постоянной памяти. Поставленная цель достигается тем, что в устройство, содержащее управления, первый вход которого соеинен с выходом блока задания прораммы, счетчик адреса, первый вход оторого соединен с выходом блока правления, дешифратор, первый -выод которого соединен со вторым вхоом блока управления, второй выход ешифратора соединен со вторым вхо- . ом сче.тчика адреса, блоки записи и хранения информации, причем первый вход блока хранения информации соединен с третьим выходом .дешифратора,и счетчик, вход которого соединен с выходом блока управления, первый выход счетчика соединен с третьим входом блока управления, второй и третий выходы - со входом.блока записи информации, введены блок коммутаций входов, вход которого соединен с выходом блока записи информации,блок коммутации выходов, один из входов которого соединен с четвертым выходом дешифратора, а выход соединен со втоpbJM входом блока хранения информации, и блок регистров числа, входы которого соединены с выходами блока коммутации входов, а выходы блока регистров числа соединены с другими входами блока коммутации выходов. Устройство соединяется с малой ЦВМ каналами приема и выдачи числовой информации, а также каналом передачи командной информации.

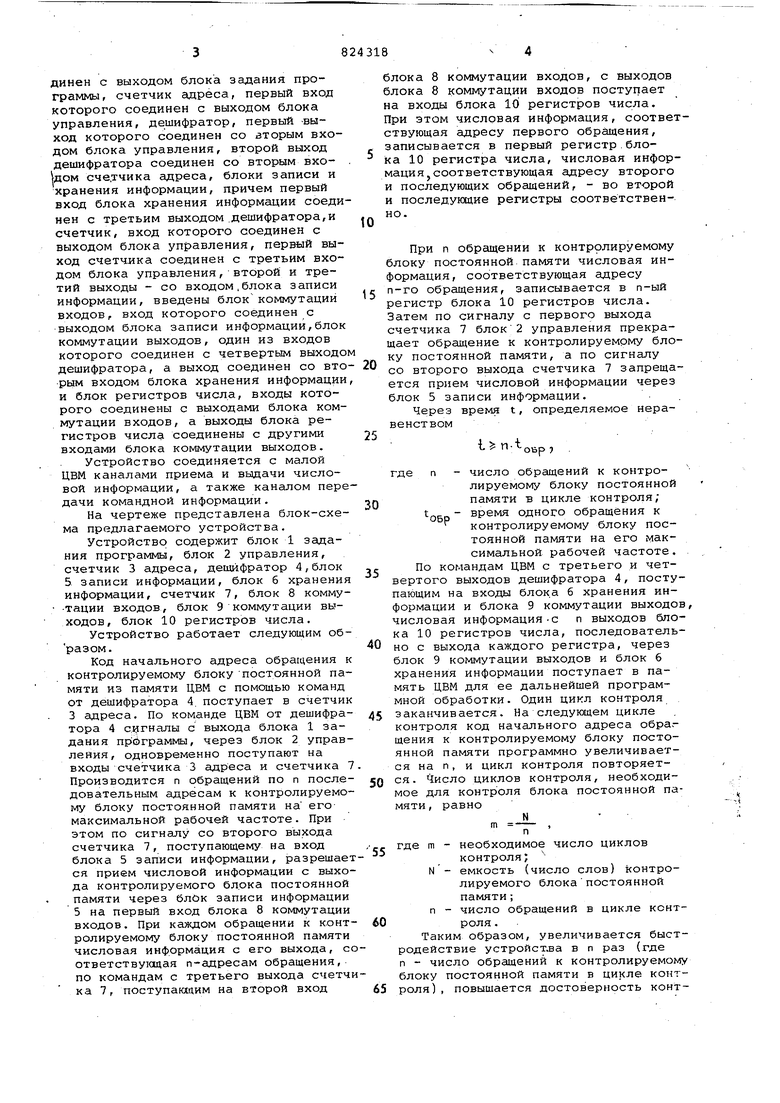

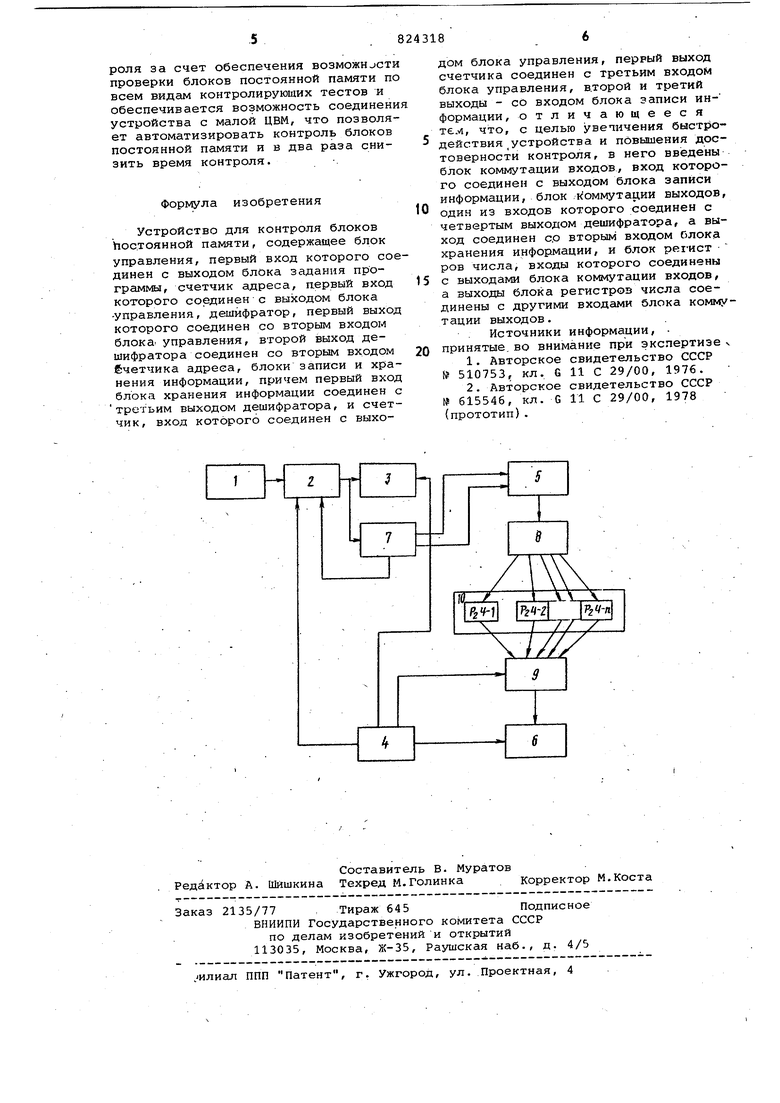

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит блок 1 задания программы, блок 2 управления, счетчик 3 адреса, дешифратор 4,блок 5 записи информации, блок б хранения информации, счетчик 7, блок 8 комму-тации входов, блок 9 коммутации выходов, блок 10 регистров числа.

Устройство работает следующим образом.

Код начального адреса обращения к контролируемому блоку постоянной памяти из памяти ЦВМ с помощью команд от дешифратора 4, поступает в счетчик 3 адреса. По команде ЦВМ от дешифратора 4 сигнешы с выхода блока 1 задания пр сЗграммы, через блок 2 управления, одновременно поступают на входы счетчика 3 адреса и счетчика 7. Производится п обращений по п последовательным адресам к контролируемому блоку постоянной памяти на егомаксимальной рабочей частоте. При этом по сигналу со второго выхода счетчика 7, поступающему на вход блока 5 записи информации, разрешается прием числовой информации с выхода контролируемого блока постоянной памяти через блок записи информации 5 на первый вход блока 8 коммутации входов. При каждом обращении к контролируемому блоку постоянной памяти числовая информация с его выхода, соответствугацая п-адресам обращения, по командам с третьего выхода счетчика 1, поступающим на второй вход

блока 8 коммутации входов, с выходов блока 8 коммутации входов поступает на входы блока 10 регистров числа. При этом числовая информация, соответствующая адресу первого обращения, записывается в первый регистр,блока 10 регистра числа, числовая информация соответствующая адресу второго и последующих обращений, - во второй и последующие регистры соответственно.

При п обреицении к контррлируемому блоку постоянной памяти числовая информация, соответствующая адресу

п-го обращения, записывается в п-ый регистр блока 10 регистров числа. Затем по сигналу с первого выхода счетчика 7 блок2 управления прекращает обращение к контролируемому блоку постоянной памяти, а по сигналу

со второго выхода счетчика 7 запрещается прием числовой информации через блок 5 записи информации.

Через время t, определяемое неравенством

, .

,

где п - число обращений к контролируемому блоку постоянной памяти в цикле контроля; время одного обращения к

ОБр контролируемому блоку постоянной памяти на его максимальной рабочей частоте. По командам ЦВМ с третьего и четвертого выходов дешифратора 4, поступающим на входы блок.а 6 хранения информации и блока 9 коммутации выходов, числовая информация-с п выходов блока 10 регистров числа, последовательно с выхода каждого регистра, через блок 9 коммутации выходов и блок 6 хранения информации поступает в память ЦВМ для ее дальнейшей программной обработки. Один цикл контроля заканчивается. На следующем цикле контроля код начального адреса обращения к контролируемому блоку постоянной памяти программно увеличивается на п, и цикл контроля повторяется. Число циклов контроля, необходимое для контроля блока постоянной памяти, равно

JL

п

где m - необходимое число циклов контроля;

емкость (число слов) контроN лируемого блокапостоянной памяти;

число обращений в цикле контроля .

Таким образом, увеличивается быстродействие устройст.ва в п раз (где п - число обращений к контролируемо лу блоку постоянной памяти в цикле контроля), повышается достоверность контроля за счет обеспечения возможност проверки блоков постоянной памяти п всем видам контролирующих тестов и обеспечивается возможность соединен устройства с малой ЦВМ, что позволя ет автоматизировать контроль блоков постоянной памяти и в два раза снизить время контроля. Формула изобретения Устройство для контроля блоков постоянной памяти, содержащее блок управления, первый вход которого сое динен с выходом блока задания программы, счетчик адреса, первый вход которого соединен с выходом блока -управления, дешифратор, первый выход которого соединен со вторым входом блока1 управления, второй выход дешифратора соединен со вторым входом йчетчика адреса, блоки записи и хранения информации, причем первый вход блока хранения информации соединен с третьим выходом дешифратора, и счетчик, вход которого соединен с выходом блока управления, первый выход счетчика соединен с третьим входом блока управления, в.торой и третий выходы - со входом блока записи информации, отличающееся тем, что, с целью увечичения 6HcTiioдействия устройства и повышения достоверности контроля, в него введены блок коммутации входов, вход которого соединен с выходом блока записи информации, блок /коммутации выходов, один из входов которого соединен с четвертым выходом дешифратора, а выход соединен с.о вторым входом блока хранения информации, и блок регист ров числа, входы которого соединены с выходами блока коммутации входов, а выходы блока регистров числа соединены с другими входс1ми блока коммутации выходов. Источники информации, принятые, во внимание при экспертизе ч 1.Авторское свидетельство СССР № 510753, кл. G 11 С 29/00, 1976. 2.Авторское свидетельство СССР № 615546, кл. G 11 С 29/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1982 |

|

SU1049984A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Устройство для контроля оперативнойпАМяТи | 1978 |

|

SU822297A1 |

| Устройство для контроля блоков постоянной памяти | 1976 |

|

SU613406A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для контроля постоянной памяти | 1977 |

|

SU693442A1 |

| Устройство для обмена информацией | 1979 |

|

SU849193A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1619284A1 |

Авторы

Даты

1981-04-23—Публикация

1979-06-14—Подача