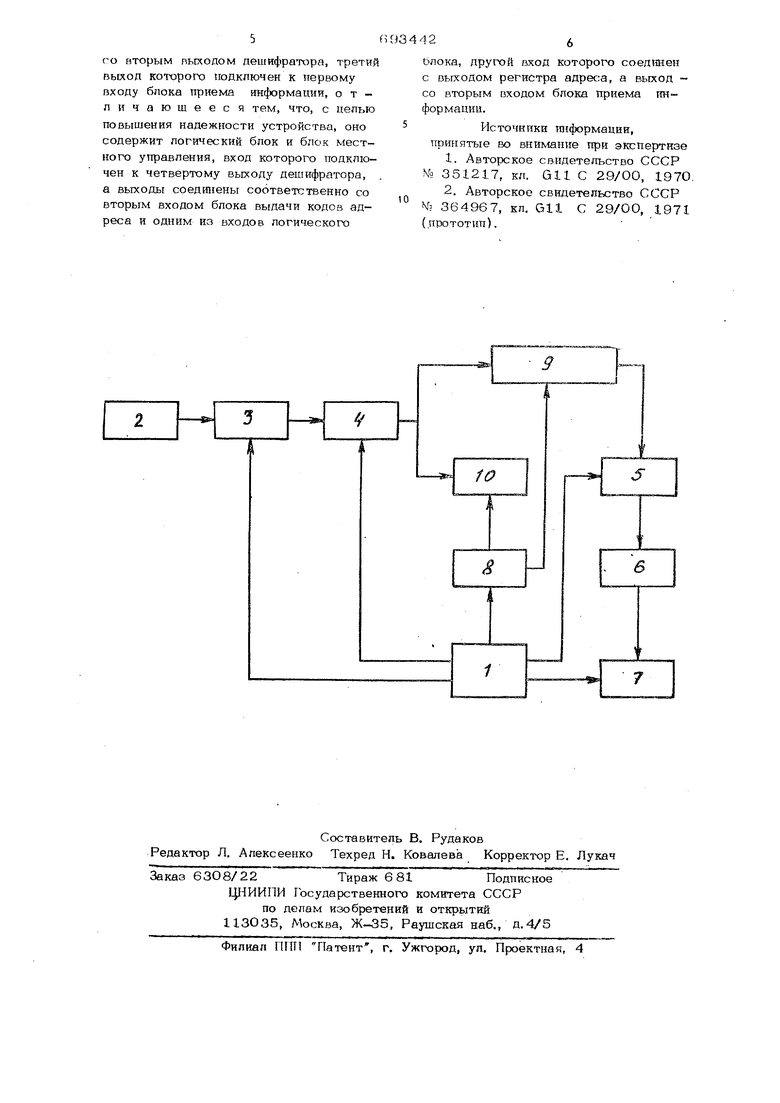

(54) УСТГОЙСТЮ ДЛЯ КОНТРОЛЯ ГОСТОЯННОЙ ПАМЯТИ роля блоков постоянной памяти, а такж не предусматривается работа устройства с 1ШМ, что приводит к сниженшо надежности устройства. Цепь изобретения - повышение надежности устройства. Поставленная цель достигается тем, что устройство содержит логический блок и блок местного управления, вход которого тюдключен к четвертому выходу дешифратора, а выходы соединены соответственно со вторым входом блока выдачи кодов адреса и одним из входсЗв логического блока, другой вход которого соединен с выходом регистра адреса, а вькод - со вторым входом блоки приема информации. На чертеже представлена блок-схема предложенного устройства. Устройство для контроля постоянной памяти соединяется с ЦВМ каналами вы дачи и приема числовой контрольной информации, каналом выдачи кома1щ (на чертеясе не показаны). Устройство содержит дешифратор 1, блок 2 задания програмьо,, блок 3 управления, регистр 4 адреса, блок 5 приема информации, регистр 6 контроль ной информации, блок 7 выдачи информации, блок 8 местного управления, ло гический блок 9, служаший для выдачи тестов самоуправления, блок Ю выдачи йодов адресов. Входы регистра 4 подключены к выходу блока 3 и первому выходу дешифр тора 1, а выход соединен с первым вхо дом блока 10. Вход и выход регистра подключены соответственно к выходу блока 5 и одному из входов блока 7, другой вход которого соединен со вторы выходом дешифратора 1, третий выход которого подключен к первому входу блока 5. Вход блока 8 подключен к четвертому выходу детцифратора 1, а выходы соединены соответственно со вторым входом блока 10 и одним из входов блока 9, дрУгой вход которого соединен с выходом регистра 4, а выход со вторым входом блока 5. Устройство работает следующим образом. Код адреса обращения к контролируе мому блоку постоянной памяти от ЦВМ с помощью команд от дешифратора I поступает в регистр 4 адреса, сигнальт блока 2 задания программы через б;юк управления по команде с деи1нфр),чторл поступают в регистр 4 адрег;а с его выхода, через открытый сигналом от злока 8 блок 10 выдачи кодов адреса, на вход контролируемого блока постоянт ной памяти (на чертеже не показан).При этом блок 9 закрыт. Выходные сигналы с выхода иэнтролируемого блока постоянной памяти принимаются по команде с дешифратора 1 через блок 5 в регистр 6 контрольной информации и по команде с дешифратора 1 через блок 7 поступают на вход ЦВМ для дальнейшей программной-обработки. Цикл контроля повторяется для следующего шэда адреса. Самопроверка устройства производится следуюшюуд образом. По команде дешифратора 1 блок 8 вырабатывает сигналы: закрывающий блок 10 и открывающий блок 9. Код теста самопроверки из ЦВМ с помошью команд от дешифратора 1 поступает в регистр 4 и с его выхода по команде от дешифратора 1 через блок 9 и блок 5 в регистр 6 контрольной информации. С выхода регистра контрольной информации 6 через блок 7 по команде с дешифратора 1 код теста.самопроверки поступает в ЦВМ для дальнейшей программной обработки. Циклы самопроверки могут повторяться различньми кодами теста самопроверки. Таким образом, описанное устройство повышает надежность работы устройства для контроля постоянной памяти за счет повышения достоверности контроля постоянной памяти, обеспечивая возможность реализации оперативной самопроверки устройства в процессе контроля постоянной памяти, без отключения последнего от устройства, а также обеспечивает необходимую полноту самопроверки устройства для контроля постоянной памяти... Формула изобретения Устройство для контроля постоянной памяти, содержашее регистр адреса, входы которого подключены к выходу блока управления и первому выходу дешифратора, а выход соединен с первым входом блока выдачи кодов адреса, регистр контрольной информации, вход и выход которого подключены соответственно к выходу блока приема информации и одному из входов блока выдачи информации., друтх)й вход которого соединен

со вторым выходом дешифратора, третий выход которого подключен к первому входу блока приема информации, отличающееся тем, что, с цепью повышения надежности устройства, оно содержит логический блок и блок местного управления, вход которотх подключен к четвертому выходу дешифратора, а выходы соединены соответственно со вторым входом блока выдачи кодов адреса и одним из входов логического

блока, другой вход которого соединен с выходом регистра адреса, а выход со вторым входом блока приема информации.

Источники информации, принятые во внимание при экспертизе

1.Авторское св.и4етепьство СССР № 351217, кл. 011 С 29/00, 1970,

2.Авторское свидетельство СССР Мз 364967, кп. G11 С 29/00, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1982 |

|

SU1049984A1 |

| Устройство для контроля оперативнойпАМяТи | 1978 |

|

SU822297A1 |

| Устройство для контроля блоковпОСТОяННОй пАМяТи | 1979 |

|

SU824318A1 |

| Устройство для контроля блоков постоянной памяти | 1976 |

|

SU613406A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1619284A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

Авторы

Даты

1979-10-25—Публикация

1977-07-11—Подача