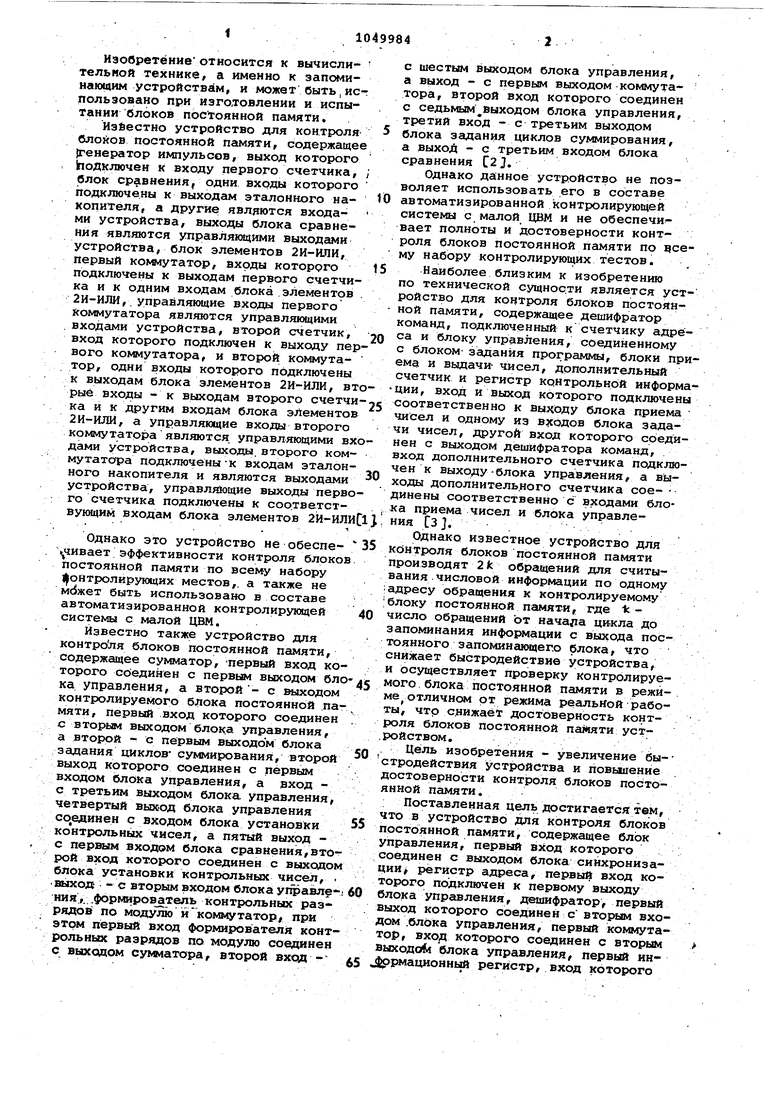

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть,исг пользовано при изготовлении и испытании блоков постоянной памяти. Известно устройство для контроля блоков постоянной памяти, содержащее генератор импульсов, выход которого Иодключен к входу первого счетчика, блок сравнения, одни входы которого подключены к выходам эталонного накопителя, а другие являются входами устройства, выходы блока сравнения являются управлякнцими выходами устройства, блок элементов 2И-ИЛИ, первый кокмутатор/ входы которого подключены к выходам первого счетчика и к одним входам блока элементов 2И-ИЛИ,, управляющие входы первого Коммутатора являются управляющими .входами устройства, второй счетчик, вход которого подключен к выходу пер вого коммутатора, и второй коммутатор/ одни входы которого подключены к выходам блока элементов 2И-ИЛИ, вт рые входы - к выходам второго счетчи ка и к другим входам блока элементов 2И-ИЛИ, а управляющие входы второго коммутатора являются управляющими вх дами устройства, выходы, второго коммутатсра подключены-к входам эталонного накопителя и являются выходами устройства, управляющие выходы перво го счетчика подключены к соответствующим входам блока элементов 2Й-ИЛИ Однако это устройство не обеспе чивает. эффективности контроля блоков постоянной памяти по всему набору | онтролирующих местов,. а также не мйжет быть использовано в составе автоматизированной контролирующей системы с малой ЦВМ. Известно также устройство для контроля блоков постоянной памяти, содержащее сумматор, первый вход которого сЬединен с первым выходом бло ка управления, а второй- с млходом контролируемого блока постоянной памяти, первый вход которого соединен с вторым выходом блока управления, а второй - с первым выходом блока задания циклов суммирования, второй выход которого соединен с первым входом блока управления, а эход с третьим выходом блока управления, четвертый выход блока управления со единен с входом блока установки контрольных чисел, а пятый выход с первым входом блока сравнения,второй вход которого соединен с выходом блока установки контрольных чисел, . выход - с вторым входом блока угфавления,. .формирователь контрольных разрядое по модули) и коммутатор, при этом первый вход формирователя контрольных разрядов по модулю соединен с выходом су матора, второй вход с шестым выходом блока управления, а выход - с первым выходом коммутатора, второй вход КОТОРОГО соединеи с седьмым выходом блока управления, третий вход - с третьим выходом блока задания циклов суммирования, а выход - с третьим входом блока сравнения C2J. Однако данное устройство не позволяет использовать .его в составе автоматизированной контролирующей системы с малой ЦВМ и не обеспечивает полноты и достоверности контроля блоков постоянной памяти по всему набору контролирующих тестов. . Наиболее близким к изобретению по технической сущности является устройство для контроля блоков постоянной памяти, содержащее дешифратор команд, подключенный к счетчику адреса и блоку управления, соединенному с блоком- задания программы, блоки приема и выдачи- чисел, дополнительный счетчик и регистр контрольной информации, вход и выход которого подключены соответственно к выходу блока приема чисел и одному из входов блока задачи чисел, другой вход которого соединен с выходом дешифратора команд, вход дополнительного счетчика подключен к выходу-блока управления, а выходы до полните ль.но го счетчика сое- динены соответственно с входами блока приема чисел и блока управления Сз J. Однако известное устройство для контроля блоков постоянной памяти производят 2fc обращений для считывания .числовой информации по одному адресу обращения к контролируемому блоку постоянной памяти, где число обращений от нача/ia цикла до запоминания информации с выхода постоянного запоминаннцег.о блока, что снижает быстродействие устройства, и осуществляет проверку контролируемого блока постоянной памяти в режиме отличном от режима реальной работы, чтр с.нижаёт достоверность контроля блоков Постоянной пайяти устройством. Цель изобретения - увеличение бы-стродействия устройства и повышение достоверности контроля блоков постоянной памяти. Поставленная цель достигается тем, что в устройство для контроля блоков постоянной памяти, содержащее блок управления, первый вход которого соединен с выходом блока синхронизации регистр адреса, первый вход которого подключен к первому выходу блока управления, дешифратор; первый выход которого соединен свторым входом ,блйка управления, первый коммутатор, Bxoja которого соединен с вторым выходов блока управления, первый ин ррмационный регистр, вход которого подключен к выходу первого коммутатора, второй коммутатор,, первый вход которого соединен с первым выходом первого информационного регистра/ . второй вход - с вторым выходом дешиф ратора/ блок сравнения, первый вход которого подключен к второму выходу первого информационного регистра,: первый выход - к третьему входу второго коммутатора/ а второй выход к третьему входу блока управлений, второй информационный регистрj первый выход которого соединен с вторым входом блока сравнения, а второй выход - с четвертым входом второго ком мутатора, счетчик адреса, первый вхо которого подключен к третьему вьохбду блока управления, второй вход - к третьему выходу дешифратора, а первый йыход соединен с пятым входом второго коммутатора, введены первый {второй накопители, третий и четверты коммутаторы, причем первый вход первого накрпителя соединен с вторым выходом счетчика адреса/ второй вход с выходом третьего коммутатора, а вы ход - с вторым входом регистра адреса, первый вход второго накопителя подключен к третьему выходу счетчика адреса, в торой вход - к выхрДУ четве того коммутатора, а выход - к входу второго информационного регистра/ входы третьего и четвертого коммутаторов соединены с четвертвым и пятым выходами дешифратора соответственно, ;. Устройство для контрюля блоков . постоянной памяти соединяется с ЦВМ каналами выдачи и приема числовой ин формации, каналом выдачи команд. На фиг. 1 представлена блок-схема устройства; -на фиг..2 - блок-схема счетчика адреса; на фиг. 3 - блоксхема третьего комму та тора у на фи1,4 блок-схема четвертого, коммутатора. Устройство содержит блок 1 синхро низации, блок 2 управления, регистр 3 адреса/ дешифратор 4, первый коМму та тор 5, первый инфор.мационный регистр 6, второй коммутатор 7/ блок 6 сравнения/ второй информашюнный регистр 9, счетчик 10 адресу, первый 11 и второй 12 накопители, третий : 13 и. четвертый 14 коммутаторы, CieTчик 10 адреса содержит счетчик 15 и три группы усилителей 1€-1би,17-17 / 18-18п (где 11 - число разрядов счетчика 15) развязки. Третий коммутатор 13 содержит уби лйтель 19 команды и группу элементов И 20-20п (где п - число разрядов ка налов вывода ЦВМ), Четвертый комму татор 14 содержит усилитель 21 ко- . манды и группу элементов И ; (где п - число разрядов канала выво.да ЦВМ).. : Устройство работает следунадим об Вазом. Коды адресов обращений, к контролируемому блоку постоянной памяти и числовая эталонная информация/ соответствующая каждому гщресу контролируемой информации блока постоянной памяти из памяти ЦВМ, последовательно поступают на входы третьего 13 и четвертого 14 коммутаторов. С помощью команд отдешифратора 4, дешифрирующего команды от ЦВГ1, сигналы с выходов коммутаторов 13 и 14 последовательно поступают на входы первого накопителя 11, где хранятся адреса, и второго накопителя 12, геде хранится числовая информация. Выбор адреса записи в накопители 11 и 12 производится сигналами, поступающими с выходов счетчика 10 адреса, установка которого в необходимое состояние производится командами, поступающими из памяти ЦВМ, с помсэдью сигналов от дешифратора 4. После окончания записи вз памяти ЦВМ в идентичных адресах накопителей 11 и 12 размещаются коды адресов и числовая информация данных адресов : выбранного контролирукицего теста. По команде ЦВМ, с помощью сигнала с |выхода дешифратора 4, сигналы с вы- . . хода блока 1 синхронизации через блок 2 управления поступают на вход счетчика 10 адреса. Сигналы кода начального адреса с выходов счетчика 10 адреса одновременно поступают на входы первого 11 и второго 12 нако- пителей. С выхода первого накопителя 11сигналы кода адреса обращения к контролируемому блоку постоянной памяти поступают на вход регистра 3 адреса. С выхода второго накопителя 12сигналы числовой информации, соответствующей выбранному коду адреса контролирующего теста/ поступают йа вход второго информационного регистра 9 и далее с первого его вы- . хода на один из входов блрк-а 8 сравнения. Сигналы с выхода блока 1 синхронизации через блок 2 управления поступают на входы регистра 3 адреса и первого коммутатора 5. Производится один цикл обращения k контролируемому блоку постоянной памяти, Сигналы с выхода контролируемого блока постоянной памяти через первый комт мутатор 5/ по команде с выхода блока 2 управления поступают на вход пергвого информационного регистра б и с дного из его выходов на первый вход блока В сравнения, где сравниваются сигналами с выхода второго информаионного регистра 9. При сравнении сигналом с выхода. блока 1 синхронизации через блок 2 управления- состояние счетчика 10 адреса увеличивается на единицу, и цикл работы устройства повторяется. При несравнении сигналом с второго выхода блока 8 сравнения запрещается

работа блока 2 управления, и сигнал с первого выхода блока 8 сравнения через второй коммутатор 7 поступает в ЦВМ, сигнализируя о наличии неиспраности контролируемого блока постоянной памяти. По сигналам от дешифратора 4:выходные сигналы с выхода регистра 3 адреса, первого 6 и второго

9информационных регистров, счетчика

10адреса, соответствукяцие адресу обращения и контролируемому блоку постоянной памяти, при контроле которого зафиксировано несравнение считанного

и эталонного значения числовой информации, .через второй, коммутатор поступают в память ЦВМ для их даль нейшей обработки.

Продолжение работы устройства производится по следующей команде ЦАМ, сигнсшом с выхода.дешифратора 4, поступающим на вход блока 2 управления Цикл работы устройства повторяется. Производятся обращения к контролируемому блоку постоянной памяти по всему контролируемому тесту, кода адресов которого занесены в накопитель 11, а числовая этгшонная информация b накопитель 12. Команды ЦВМ с помощью сигналов от дешифратора 4, адреса обращения к контролируемому блоку постоянной памятк и числовая информация следующего контролирующего . теста через третий 13 и четвертый 14 коммутаторы вносятся в накопители 11 и 12 соответственно.

Работа устройства повторяется для следующего контролир1 щего теста.

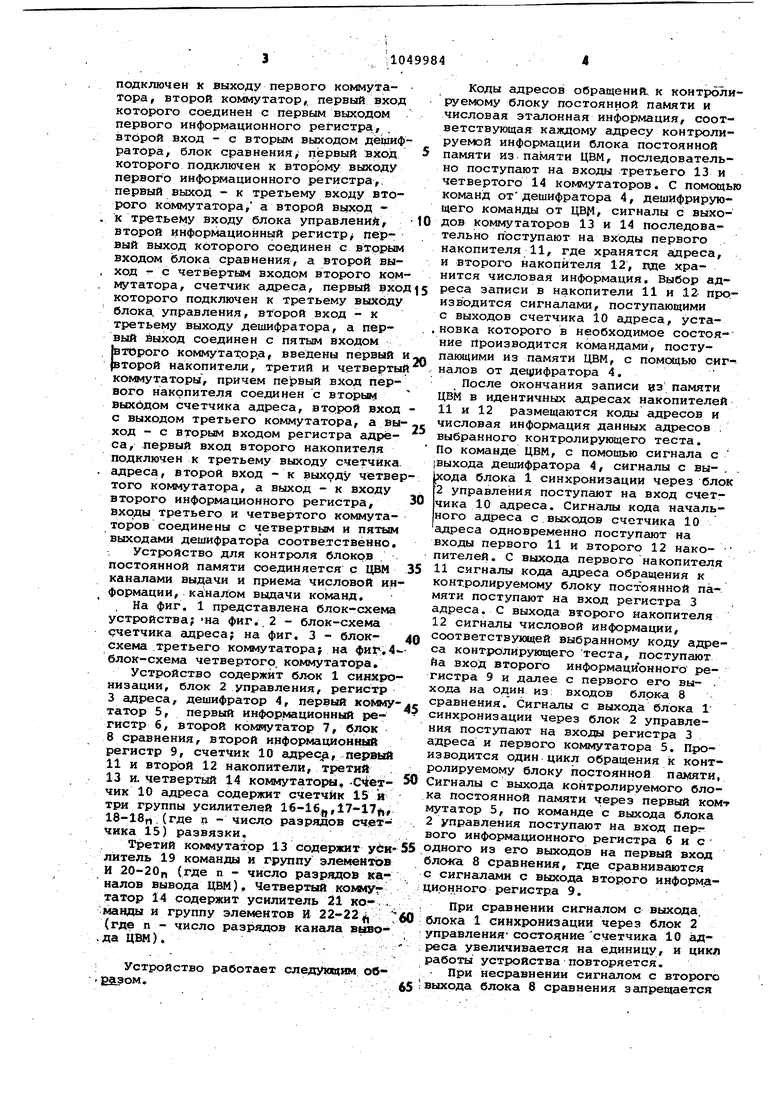

Счетчик 10 адреса работает следуквдим образом.

На первый вход счетчика 15 в режиме обращения к контролируемому блоку постоянной памяти поступаьрт сигналы с одного из выходов блока 2 управления, на второй вход - сигналы А(|.дд, с одного из выходов дешифратора 4 в режиме записи кодов адресов и числовой информации из памяти ЦВМ в накопители,11 и 12, сигналы параллельного кода адреса с выходов ра эрядов счетчика 15 через три группы усилителей 1б-1бр, 17-17,18 -1В„ развязки (где h - число разрядов

счетчика 15/ поступают соответственно на входы первого 11 и второго 12 накопителей и второго коммутатора 7. ,

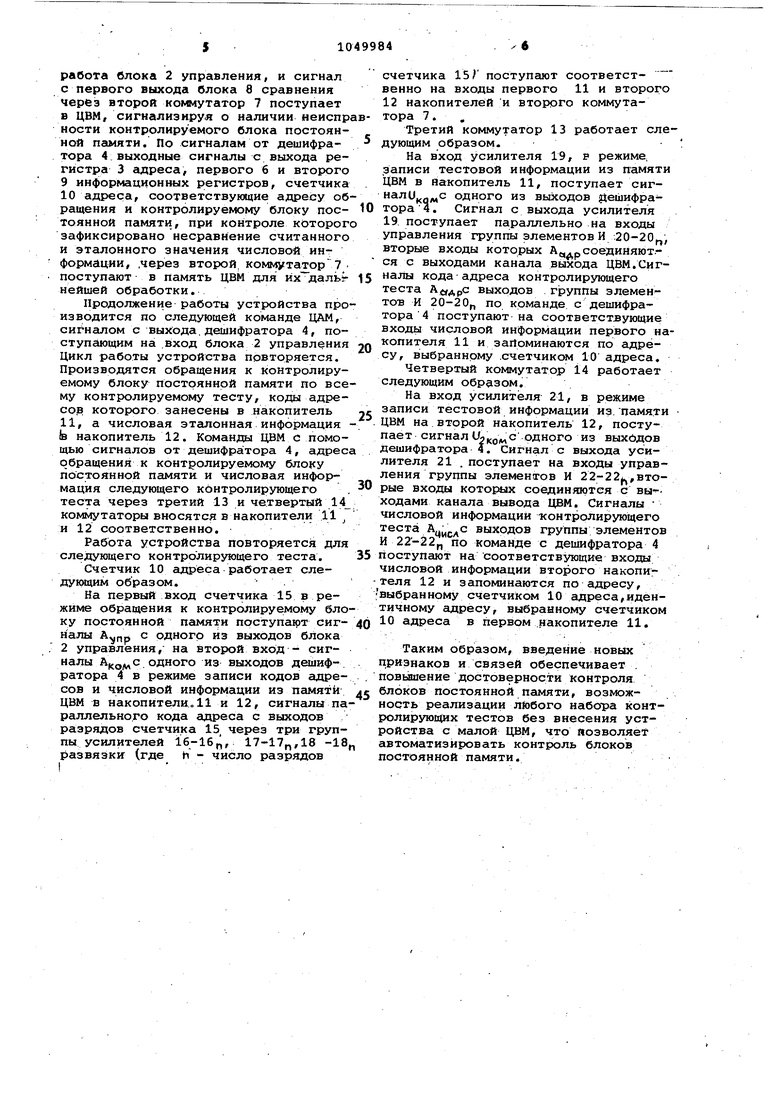

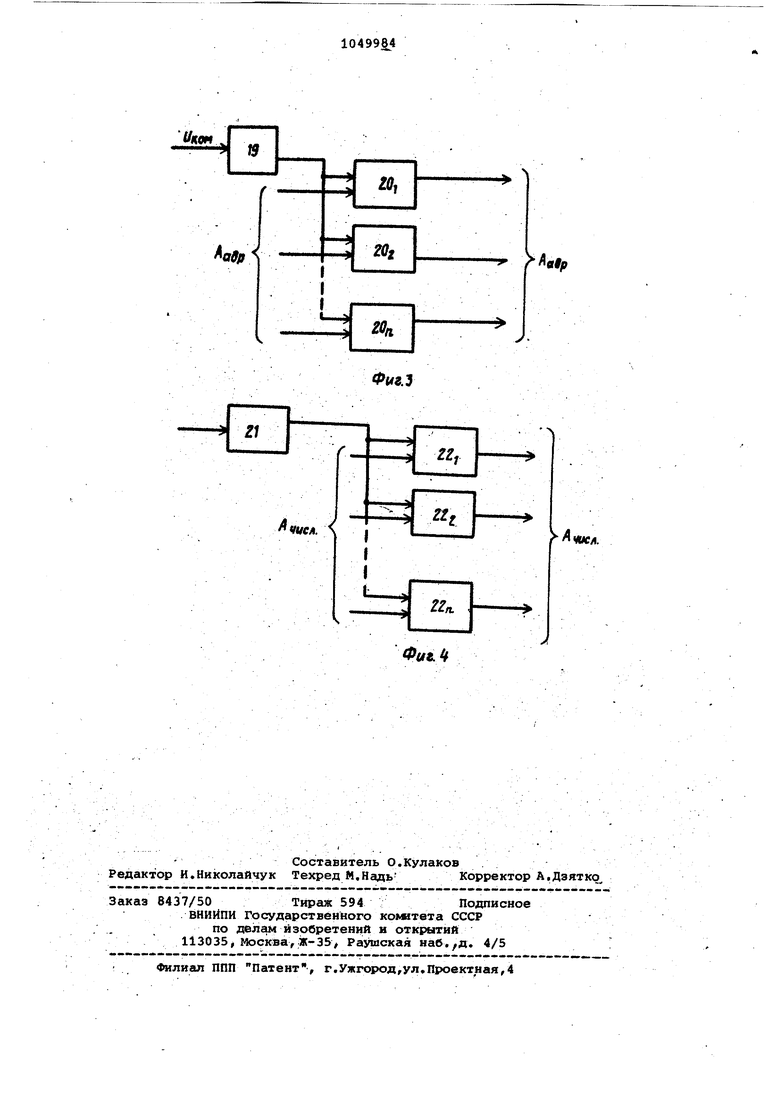

Третий коммутатор 13 работает следующим образом.

На вход усилителя 19, Р режиме, записи тестовой информации из памяти ЦВМ в накопитель 11, поступает сигналОцп с одного из выходов дешифратора 4. Сигнал с выхода усилителя 19. поступает параллельно на входы управления группы элементов И .20-20, вторые входы которых А,рСоединяют.ся с выходами канала выхода ЦВМ.Сигналы кода адреса контролирующего теста AffApC выходов группы элемен тов И 20-20„ по команде, с дешифратора 4 поступают на соответствующие входы числовой информации первого накопителя 11 и запоминаются по адресу, выбранному .счетчиком 10 адреса.

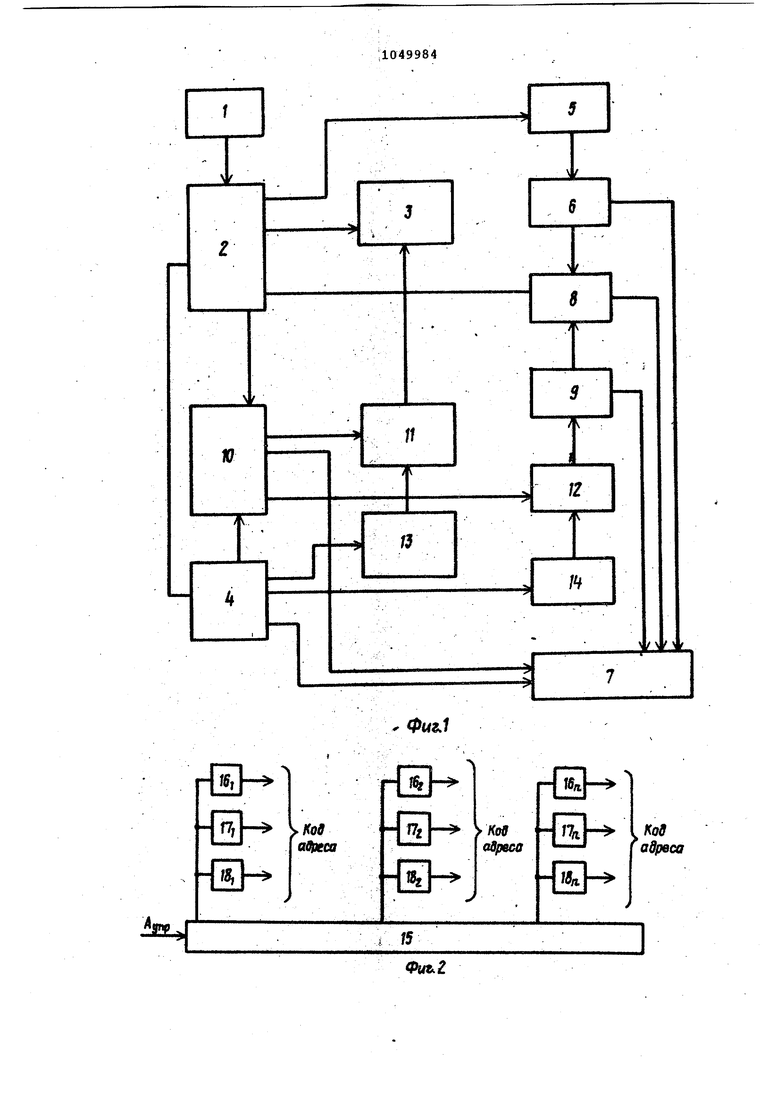

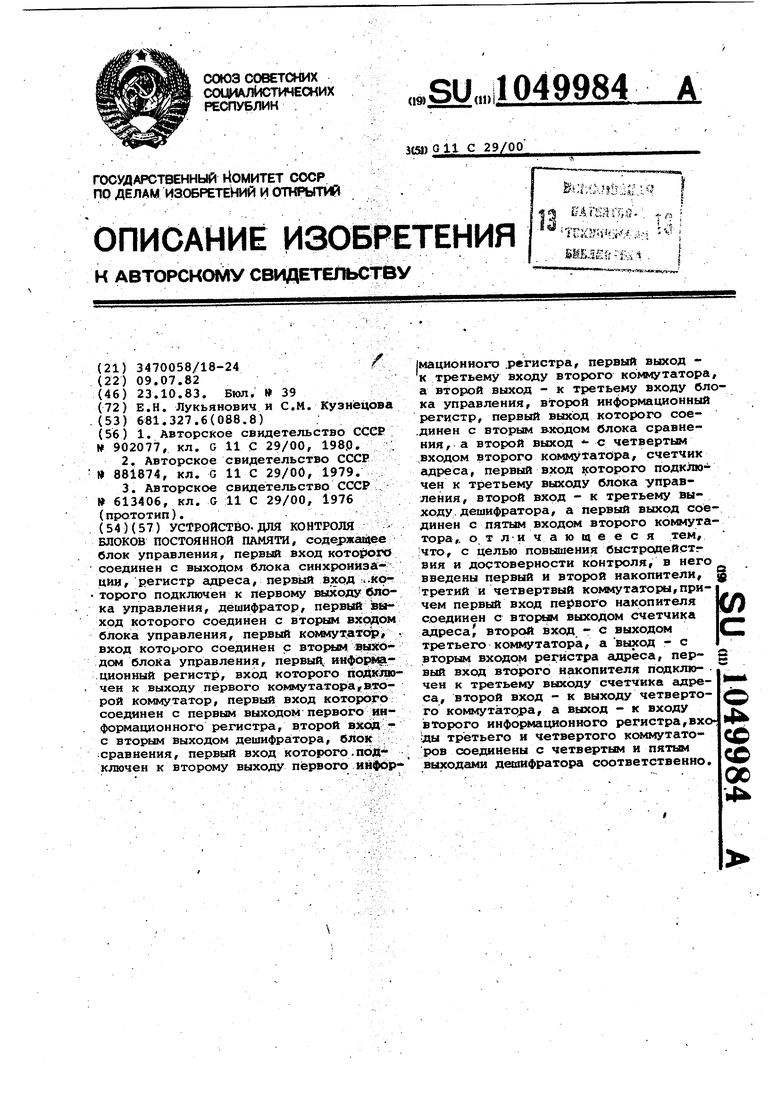

Четвертый коммутатор 14 работает следующим образом.

На вход усилителя 21, в режиме записи тестовой информации из памяти ЦВМ на второй накопитель 12, поступает сигнал с одного из выходов дешифратора 4. Сигнал с выхода усилителя 21 . поступает на входы управления группы элементов И 22-22j BTOрые входы которых соединя1ртся с ходами канала вывода ЦВМ. Сигналы числовой информации контролирующего теста .c выходов группы элементов }Л 22-22„ по команде с дешифратора 4 поступают иа соответствующие входы числовой информации второго накопителя 12 и запоминаются по адресу, выбранному счетчиком 10 адреса,идентичному адресу, выбранному счетчиком 10 адреса в первом накопителе 11.

Таким образом, введение новых признаков и связей обеспечивает . повышение достоверности контроля блоков постоянной памяти, возможность реализации любого набора контролирующих тестов без внесения устройства с малой ЦВМ, что позволяет автоматизировать контроль блоков постоянной памяти.

Фм&

Koff

Kotf аарвса адреса

н

jlCL

5

Ф8Л2

a9p

Аавр

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Устройство для контроля оперативнойпАМяТи | 1978 |

|

SU822297A1 |

| Устройство для контроля блоковпОСТОяННОй пАМяТи | 1979 |

|

SU824318A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для контроля постоянной памяти | 1977 |

|

SU693442A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Устройство для обмена информацией | 1979 |

|

SU849193A1 |

| Устройство для контроля блоков постоянной памяти | 1976 |

|

SU613406A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1619284A1 |

УСТРОЙСТВО- ДЛЯ КОНТРОЛЯ БЛОКОВ ПОСТОЯННОЙ ПАМЯТИ, содержащее блок управления, первый вход котоЕ)ОГО соединен с выходом блока синхронизации, регистр адреса, первый вход ..которого подключен к первому выходу блока управления, дешифратор, пврв1яй выход которого соединен с вторалм входом блока управления, первый ко1имутатср, . вход которого соединен с вторым выходом блока управления, первый, информационный регистр, вход которого подключен к выходу первого коммутатора,второй коммутатор, первый вход которого соединен с первым выходом первого информационного регистра, второй вход с вторым выходом дешифратора, блок сравнения, первый вход которого.подключен к второму выходу первого имфор {мационного .регистра, первый выход к третьему входу второго коммутатора, а второй выход - к третьему входу блока управления, второй информационный регистр, первый выход которого сое.динен с вторым аходом блока сравнения , а второй выход с четвертым .входом второго коммутатора, счетчик адреса, первый вход 1 соторого подключен к третьему выходу блока управления, второй вход - к третьему выходу, дешифратора, а первый выход соединен с пятым входом второго коммутатора,, от л-и ча ю адее с я тем, что, с целью повышения быстродейстг ВИЯ и достоверности контроля, в него введены первый и второй накопители, щ третий и четвертвый коммутаторы,причем первый вход первого накопителя соединен с вторым выходом счетчика гщреса) второй вход - с выходом третьего коммутатора, а выход - с вторьо4 входом регистра адреса, первый вход второго Накопителя подклю- чен к третьему выходу счетчика гшреса, второй вход - к выходу четвертого коммутатора, а выход - к входу 4Si iBToporo информационного регистра,вхо СО СО 00 4s даы третьего и четвертого коммутаторов соединены с четвертым и пятым выходами дешифратора соответственно.

Фиг.У

VttCA

ZZn.

Фиг.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU902077A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-10-23—Публикация

1982-07-09—Подача