(54) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированная вычислительная система | 1989 |

|

SU1798946A1 |

| Многоканальная система обмена для управления электропитанием вычислительного комплекса | 1988 |

|

SU1654830A1 |

| Система обработки данных | 1979 |

|

SU849219A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Адаптивное вычислительное устройство | 1980 |

|

SU957214A1 |

| Отказоустойчивая вычислительная система | 1981 |

|

SU1077070A1 |

| Устройство сопряжения процессоров в многопроцессорной вычислительной системе с изменяемой конфигурацией | 1984 |

|

SU1259278A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

,. 1 Известны вычислительные- систе1.1Ы, содержацие блоки запоминающих устройств, процессоров и устройств обме на, связанные межлу собой через коммутаторы , В этих системах возможно изменение путей передачи информации между блоками путем реконфигурации с помощью коммутаторон. В известных системах отсутствует .возможность автоматической перестройки структуры при возникновении неисправностей. Это снижает надежность работы. Наибол«-е близкой к изобретению по технической сущности является вычислительная система,содержащая К запоминающих устройств,М процессоров, |ч| устройств обмена, ко мутатор памя коммутатор процессоров, коммутатор системы, L устройств контроля, блок распределения и блок управления, при чем выходы К запоминающих устройств соединены с соответствующими входами группы входов коммутатора памяти выходы которого соединены с соответствующими входами М процессоров, выходы которых подключены к соответствующим входам группы входов коммутатора процессоров, выходы которьк подключены ко входам соответствующих К устройств обмена, выходы которых соединены с группой входов коммутатора системы, выход которого подключен ко входу блока распределения, группа входов которого соединена с выходами устройств контроля, управ-г ляю.щий выход коммутатора системы соединен со входом блока управления, выход которого подключен к управляющим входам коммутатора памяти, коммутатора процессоров и .коммутатора системы 2|.Эта известная система характеризуется потерей работоспособности при отказе.управляющего процессора, несмотря на то, что в системе есть исправные процессоры. Отказ наступает потому, что в системе отсутствует возможность автоматической реконфигурации, о.беспечивающей отключение отказавшего процессора и. назначение вместо него управляющим одного из исправных. Все это снижает надежность работы системы, й,ель изобретения -. повышение надежности. В описываемой системе это достигается тем, что в нее введен блок переключения состояний, содержащий регистр состояиий, группу элементов И и группу элементов ИЛИ, Кроме того, группа выходов блока распределения соедииеиа с группой входов регистра состояний, вход которого соединен со входом блока управления, выход регистра состояний подклюнен к контрольному входу коммутатора системы. У .группы выходов рбгистра состояний каждый и i + 1 выходы соединены, соответственно, с первым и вторым входами соответствующего элемента И группы, при этом третьи/ входы всех элементов И группы подключены к выходу блока управления, входы каждого элемента ИЛИ группы соединены с выходами соответствующих элементов И группы, а выходы группы элементов ИЛИ подключены к группе входов блока управления.

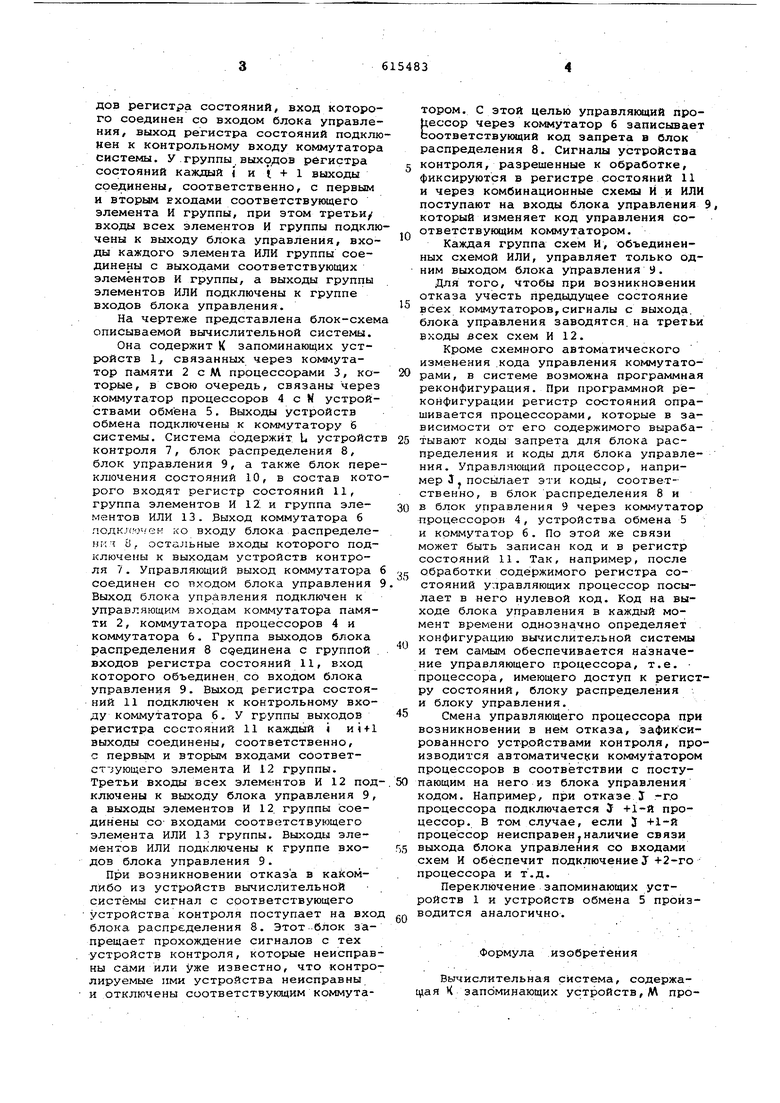

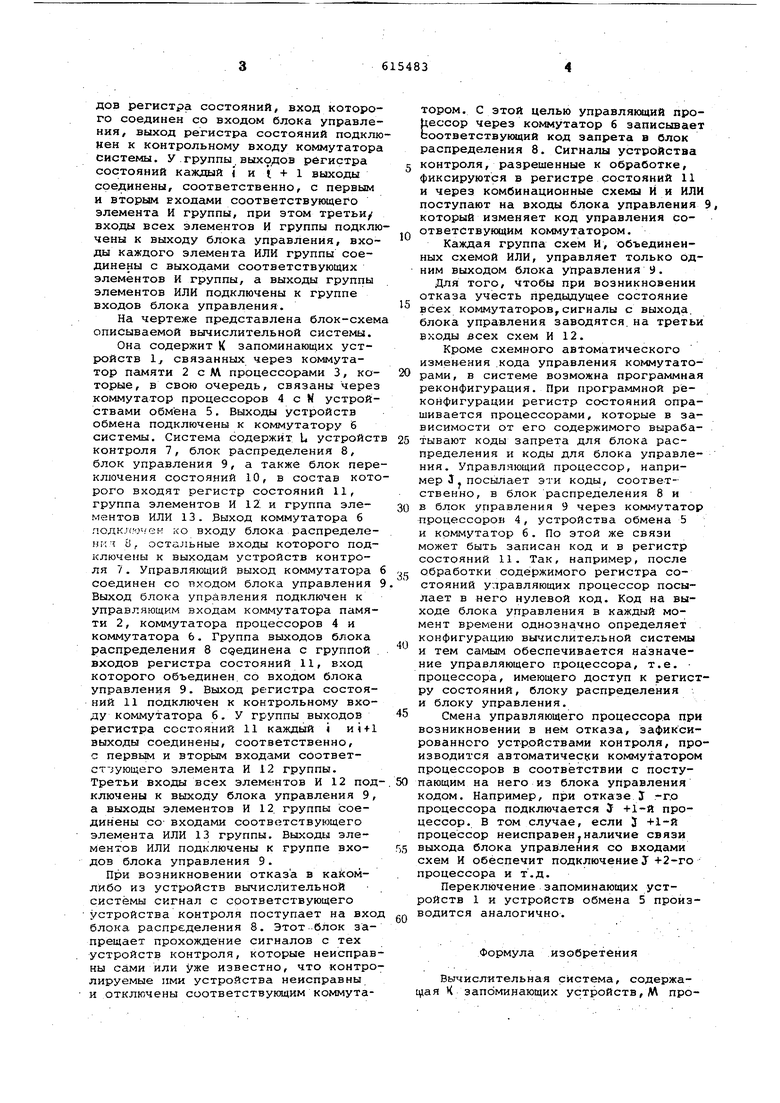

На чертеже представлена блок-схем описываемой вычислительной системы.

Она содержит К запоминающих устройств 1 связанных через коммутатор памяти 2 с АЛ процессорами 3, которые, в свою очередь, связаны через коммутатор процессоров 4 с V устройствами обмена 5, Выходы устройств обмена подключены к коммутатору 6 системы. Система содержит L устройст контроля 7, блок распределения 8, блок управления 9, а также блок переключения состояний 10, в состав которого входят регистр состояний 11, группа элементов И 12. и группа элементов ИЛИ 13. Выход коммутатора 6 г.одк.к.ючек ко входу блока распределент 8, остальные входы которого подключены к выходам устройств контроля 7. Управляющий выход коммутатора соединен со входом блока управления Выход блока управления подключен к управляющим входам коммутатора памяти 2, коммутатора процессоров 4 и коммутатора 6. Группа выходов блока распределения 8 сдединена с группой . входов регистра состояний 11, вход которого объединен, со входом блока управления 9. Выход регистра состояний 11 подключен к контрольному входу коммутатора 6. У группы выходов регистра состояний 11 каждый i выходы соединены, соответственно, с первым и вторым входами соответст- ующего элемента И 12 группы. Третьи входы всех элементов И 12 под ключены к выходу блока управления 9, а выходы элементов И 12. группы соединены со- входами соответствующего элемента ИЛИ 13 группы. Вы :оД1д элементов ИЛИ подключены к группе входов блока управления 9.

При возникновении отказа в кайомлйбо из устройств вычислительной системы сигнал с соответствующего устройства контроля поступает на вход блока распределения 8. Этот .блок запрещает прохождение сигналов с тех устройств контроля, которые неисправны сами или уже известно, что контролируемые ими устройства неисправны и отключены соответствующим коммутатором, с этой целью управлякяций процессор через коммутатор 6 записывает соответствующий код запрета в блок распределения 8. Сигналы устройства контроля, разрешенные к обработке, фиксируются в регистре состояний 11 и через комбинационные схемы И и ИЛИ поступают на входы блока управления 9, который изменяет код управления соответствукадим коммутатором.

0

Каждая группа схем И, объединенных схемой ИЛИ, управляет только одним выходом блока управления 9.

Для того, чтобы при возникновении отказа учесть предыдущее состояние

5 всех коммутаторов,сигналы с выхода, блока управления заводятся, на третьи входы всех схем И 12.

Кроме схемного автоматического изменения .кода управления коммутато0рами, в системе возможна программная реконфигурация. При программной реконфигурации регистр состояний опрашивается процессорами, которые в зависимости от его содержимого выраба5тывают коды запрета для блока распределения и коды для блока управления. Управляющий процессор, например J посылает эти коды, соотве.тственно, в блок распределения 8 и в блок управления 9 через коммутатор процессоров 4, устройства обмена 5 и коммутатор 6. По этой же связи может быть записан код и в регистр состояний 11. Так, например, после Обработки содержимого регистра со5стояний управляющих процессор посылает в него нулевой код. Код на выходе блока управления в каждый момент времени однозначно определяет конфигурацию вычислительной системы и тем carvibiM обеспечивается назначение управляющего процессора, т.е. процессора, имеющего доступ к регистру состояний, блоку распределения и блоку управления.

Смена управляющего процессора при возникновении в нем отказа, зафиксированного устройствами контроля, производится автоматически коммутатором процессоров в соответствии с поступающим на него из блока управления кодом. Например, при отказе J .-г.о процессора подключается J +1-й процессор. В том случае, если 3 +1-й процессор неисправен,наличие связи выхода блока управления со входами схем И обеспечит подключениеJ +2-го процессора и т .д.

Переключение запоминающих устройств 1 и устройств обмена 5 производится аналогично.

Формула изобретения

Вычислительная система, содержащая Ч запоминающих устройств,М проlieccopOB, М устройств обмена, комму татор памяти, коммутатор процессоров коммутатор системы, L устройств кон троля, блок распределения и блок управления, причем выходы Ц запоминающих устройств соединены с соответствующими входами группы входов коммутатора памяти, выходы которого сое динены с соответствующими входами М процессоров, выходы которых подключе ны к соответствующим входам группы входов коммутатора процессоров, выхо ды которого подключены ко входам соответствующих N устройств обмена, выходы которых соединены с группой входов коммутатора системы, выход которого подключен ко входу блока распределения, группа входов которого соединена с выходами устройств контроля, управляющий выход KOMf syTaтора системы соединен со входом блока управления, выход которого подклю чен к управляющим входам коммутатора памяти, коммутатора процессоров и коммутатора системы, о т л и чающаяс я тем, что, с целью повышения надежности, в нее введен блок переключения состояний, содержащий регистр состояний, группу эле3ментов И и группу элементов ИЛИ, причем группа выходов блока распределения соединена с группой входов регистра состояний, вход которого соединен со входом блока управления, выход регистра состояний подключен к контрольному входу коммутатора системы, каждый -I и i +1 выходы группы выходов регистра состояний соединены, соответственно, с первым и вторым входами соответствующего элемента И группы, третьи входы всех элементов И группы подключены к выходу блока управления, входы каждого элемента ИЛИ группы соединены с выходами соответствующих элементов И группы, а выходы группы элементов ИЛИ подключены к группе входов блока управления . Источники информации, принятые во внимание при экспертизе: 1.Дроздов Е.А. и Пятибратов А.П. Основы построения и функционирования вычислительных систем. М., Энергия, 1973, с.139, 140. 2.Организация машины SERP. Экспресс-и 11,юрмация, серия ЭВТ f 22, 1973.

Авторы

Даты

1978-07-15—Публикация

1974-01-07—Подача