(54) СИСТЕМА ОБРАБОТКИ ДАННЫХ Изобретение относится к вычисли тельной технике и может быть использовано при построении систем переработки цифровой информации. Известна управляющая цифровая вычислительная машина, содержащая две группы резервных модулей (арифметическое устройство, запоминающее устройство и устройство управления), связанные через коммутаторы. При от казе одного из модулей работоспособт ность сохраняется, так как вместо отказавшего подключается резервный модуль 1. Недостаток устройства - при исправной работе всех модулей создаетс неисполь зубмая производительность, так как ЦВМ не способна перерабатывать два потока информации. Известна также система, содержащая два идентичных процессора со сх мами доступа к ним. Один из процесс ров является активным и только его. схема доступа обеспечивает выход пр цессора на внешние щины. Второй процессор является резервным 2, Однако при исправности обоих процессоров система имеет неиспольз емую вычислительную избыточность. Наиболее близкой к изобретению является модульная цифровая вычислительная система, в которой имеется несколько процессоров с соответствующими управляющими запоминающими устройствами, общее устройство управления и схема переключения признаков процессоров. В известной системе при отказе одного из процессоров формируется признак, по которому задачи отказавшего берет на себя исправный процессор 3. Недостатком системы является то, что для обнаружения отказа в каждый из процессоров должно устанавливаться дополнительное контрольное оборудование, которое не может использоваться для повышения производительности. Цель изобретения - увеличение надежности и производительности повышением полноты использования оборудования. Поставленная цель достигается тем, что в систему, содержащую два вычислительных устройства, два блока памяти микропрограмм, первые и вторые выходы которых соединены соответственно с первым и вторым входами первого и второго вычислительных

устройств/ а входы-выходы первого и второго вычислительных устройств соединены соответственно с первым и вторым выходом-входом блока организации доступа, третий вход-рыход которого является входом-выходом системы, введены два формирователя адреса, блок анализа и коммутатор, первый выход которого соединен с первым входом первого формирователя адреса, а второй выход коммутатора подключен к входу блока организации доступа и первому входу второго формирователя адреса, первые и вторые выходы формирователей адреса подключены соответственно к первым и вторым входам соответствующих блоков памяти микропрограм; 1, третьи и четвертые выходы которых соединены соответственно с вторыми и третьими входами соответствующих формирователей адреса, входы-выходы которых подключены соответственно к первому и второму выходам-входам блока организации доступа, первые выходы вычислительных устройств соединены с четвертыми входами соответствующих формирователей адреса, пятые входы, которых соединены с первым выходом блока анализа, второй и третий выходы которого соединены соответственно с первым и вторым входами коммутатора и подключены к шестым входам соответственно первого и второго формирователей адреса, седьмые входы которых подключены к вторым выходам соответственно второго-и первого вычислительных устройств, третьи выходы которых подключены соответственно к первому и второму входу блока анализа и соединены с восьмыми входами соответственно первого и второго формирователей адреса, а первый и второй входы-выходы подключены соответственно к первому и второму выходу-входу блока организации доступа..

Кроме того, формирователь адреса содержит регистр кода операции, вычислительный узел, регистр прерываний и элемент ИЛИ, выход которого подключен к первому входу вычислительного узла, второй и третий входы которого являются соответственно вторым и третьим входами формирователя, а первый и второй выходы вычислительного узла являются соответственно первым и вторым выходом формирователя адреса, входом-выходом которого является вход-выход регистра кода операции, вход которого является четвертым входом формиро ателя адреса, первый, второй, третий, четвертый и пятый входы регистра прерываний являются соответственно первым, пятым, шестым, седьмым и восьмым входами формирователя адреса, второй вход-выход регистра кода операции подключен к выходу-входу

вычислительного узла и выходу-входу регистра прерываний,первый и второй выходЬ которого подключены соответственно к первому и второму входам элемента ИЛИ.

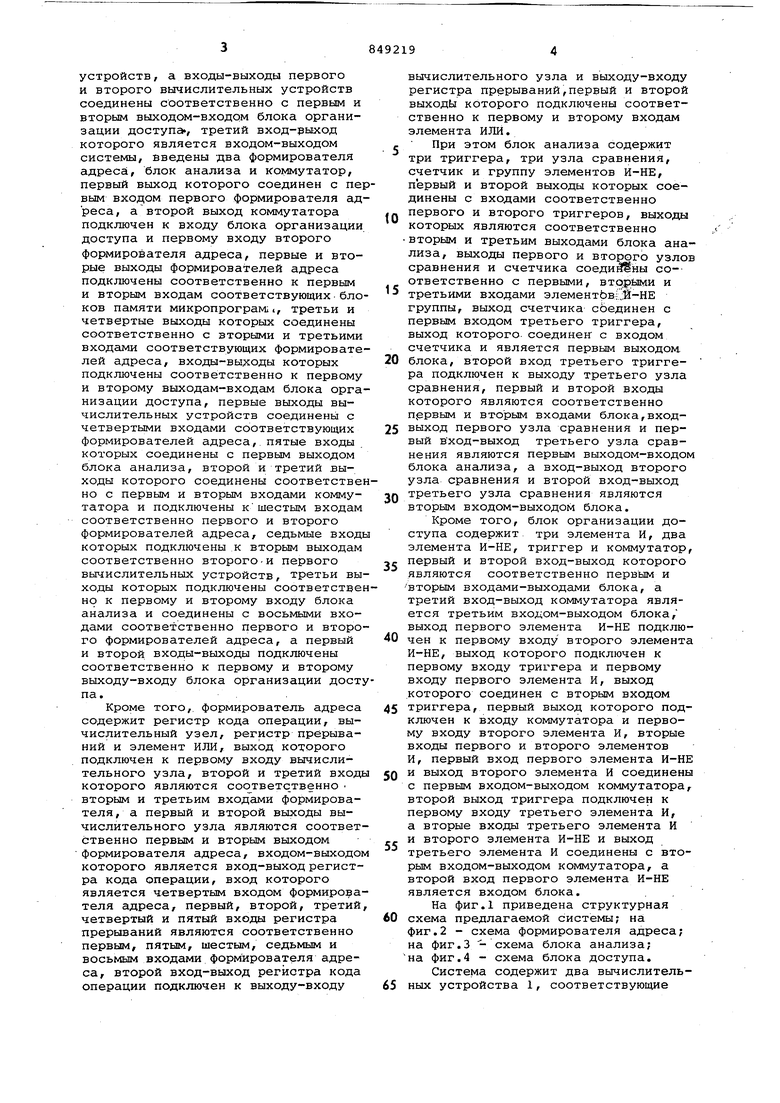

При этом блок анализа содержит три триггера, три узла сравнения, счетчик и группу элементов И-НЕ, первый и второй выходы которых соединены с входами соответственно первого и второго триггеров, выходы которых являются соответственно вторым и третьим выходами блока анализа, выходы первого и второго узло сравнения и счетчика соедий ны соответственно с первыми, втд|)ыми и третьими входами элементЬвШ-НЕ группы, выход счетчика соединен с первым входом третьего триггера, выход которого, соединен с входом счетчика и является первым выходом, блока, второй вход третьего триггера подключен к выходу третьего узла сравнения, первый и второй входы которого являются соответственно первым и вторым входами блока,входвыход первого узла сравнения и первый вход-выход третьего узла сравнения являются первым выходом-входо блока анализа, а вход-выход второго узла сравнения и второй вход-выход третьего узла сравнения являются вторым входом-выходом блока.

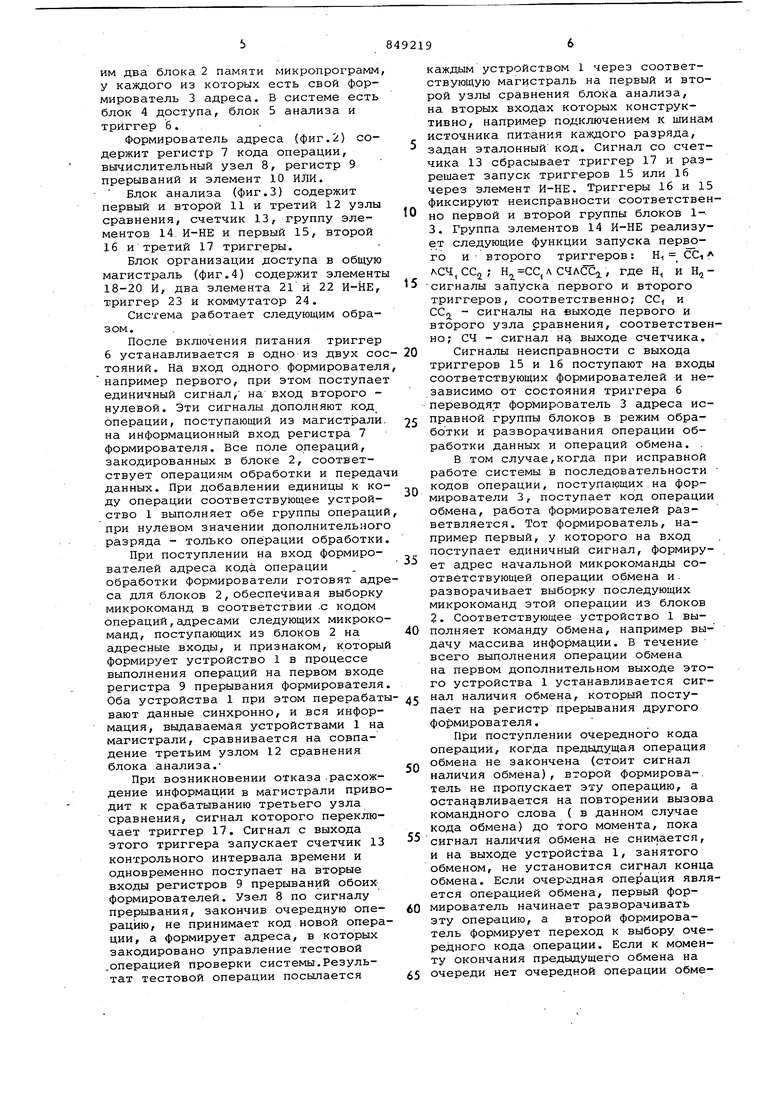

Кроме того, блок организации доступа содержит три элемента И, два элемента И-НЕ, триггер и коммутатор первый и второй вход-выход которого являются соответственно первым и вторым в ходами-выходами блока, а третий вход-выход коммутатора является третьим входом-выходом блока/ выход первого элемента И-НЕ подключен к первому входу второго элемент И-НЕ, выход которого подключен к первому входу триггера и первому входу первого элемента И, выход которого соединен с вторым входом триггера, первый выход которого подключен к входу коммутатора и первому входу второго элемента И, вторые входы первого и второго элементов И, первый вход первого элемента И-Н и выход второго элемента И соединен с первым входом-выходом коммутатора второй выход триггера подключен к первому входу третьего элемента И, а вторые входы третьего элемента И и второго элемента И-НЕ и выход третьего элемента И соединены с вторым входом-выходом коммутатора, а второй вход первого элемента И-НЕ является входом блока.

На фиг.1 приведена структурная схема предлагаемой системы; на фиг.2 - схема формирователя адреса; на фиг.З -схема блока анализа; на фиг.4 - схема блока доступа.

Система содержит два вычислительных устройства 1, соответствующие

им два блока 2 памяти микропрограмм, у каждого из которых есть свой формирователь 3 адреса. В системе есть блок 4 доступа, блок 5 анализа и триггер б.

Формирователь адреса (фиг.2) содержит регистр 7 кода операции, вычислительный узел 8, регистр 9 прерываний и элемент 10 ИЛИ.

Блок анализа (фиг.З) содержит первый и второй 11 и третий 12 узлы сравнения, счетчик 13, группу элементов 14. И-НЕ и первый 15, второй 16 и третий 17 триггеры.

Блок организации доступа в общую магистраль (фиг.4) содержит элементы 18-20 И, два элемента 21 и 22 И-НЕ, триггер 23 и коммутатор 24.

Система работает следующим образом.

После включения питания триггер 6 устанавливается в одно из двух состояний. На вход одного формирователя например первого, при этом поступает единичный сигнал, на вход второго нулевой. Эти сигналы дополняют код операции, поступающий из магистрали, на информационный вход регистра 7 формирователя. Все поле операций, закодированных в блоке 2, соответствует операциям обработки и передач данных. При добавлении единицы к коду операции соответствующее устройство 1 выполняет обе группы операций при нулевом значении дополнительного разряда - только операции обработки.

При поступлении на вход формирователей адреса кода операции обработки формирователи готовят адреса для блоков 2, обеспечивая выборку микрокоманд в соответствии .с кодом операций,адресами следующих микрокоманд, поступающих из блоков 2 на адресные входы, и признаком, который формирует устройство 1 в процессе выполнения операций на первом входе регистра 9 прерывания формирователя. Оба устройства 1 при этом перерабатывают данные синхронно, и вся информация, выдаваемая устройствами 1 на магистрали, сравнивается на совпадение третьим узлом 12 сравнения блока анализа.При возникновении отказа расхождение информации в магистрали приводит к срабатыванию третьего узла сравнения, сигнал которого переключает триггер 17. Сигнал с выхода этого триггера запускает счетчик 13 контрольного интервала времени и одновременно поступает на вторые входы регистров 9 прерываний обоих формирователей. Узел 8 по сигналу прерывания, закончив очередную операцию, не принимает код новой операции, а формирует адреса, в которых закодировано управление тестовой .операцией проверки системы.Результат тестовой операции посылается

каждым устройством 1 через соответствующую магистраль на первый и второй узлы сравнения блока анализа, на вторых входах которых конструктивно, например подключением к шинам источника пит/ания каждого разряда, задан эталонный код. Сигнал со счетчика 13 сбрасывает триггер 17 и разрешает запуск триггеров 15 или 16 через элемент И-НЕ. Триггеры 16 и 15 фиксируют неисправности соответствен0но первой и второй группы блоков 13. Группа элементов 14 И-НЕ реализует следующие функции запуска первого и- второго триггеров: HI CCi л ЛСЧ, CCj,- Н,.СС ЛСЧЛСС1, где Н., и Н,5сигналы запуска первого и второго триггеров, соответственно; СС и CCj - сигналы на выходе первого и второго узла сравнения, соответственно; СЧ - сигнал на выходе счетчика.

0

Сигналы неисправности с выхода триггеров 15 и 16 поступают на входы соответствующих формирователей и независимо от состояния триггера 6 переводят формирователь 3 адреса исправной группы блоков в режим обра5ботки и разворачивания операции обработки данных и операций обмена. .

В том случае,когда при исправной работе системы в последовательности кодов операции, поступающих на фор0мирователи 3, поступает код операции обмена, работа формирователей разветвляется. Тот формирователь, например первый, у которого на вход поступает единичный сигнал, формиру5ет адрес начальной микрокоманды соответствующей операции обмена и. разворачивает выборку последующих микрокоманд этой операции из блоков 2. Соответствующее устройство 1 вы0полняет команду обмена, например выдачу массива информации. В течение всего выполнения операции обмена на первом дополнительном выходе этого устройства 1 устанавливается сигнал наличия обмена, который посту5пает на регистр прерывания другого формирователя.

При поступлении очередного кода операции, когда предыдущая операция обмена не закончена (стоит сигнал

0 наличия обмена), второй формирова-. тель не пропускает эту операцию, а останавливается на повторении вызова командного слова ( в данном случае кода обмена) до того момента, пока

5 сигнал наличия обмена не снимается, и на выходе устройства 1, занятого обменом, не установится сигнал конца обмена. Если очер адная операция является операцией обмена, первый фор0мирователь начинает разворачивать эту операцию, а второй формирователь формирует переход к выбору очередного кода операции. Если к моменту окончания предыдущего обмена на очереди нет очередной операции обме5на, по сигналу конца обмена перед началом развертывания очередной опе рации оба формирователя переходят н операцию восстановления внутренней памяти первого устройства 1 пересыл кой данных из второго устройства 1 в первое через общую магистраль. После окончания этбй .операции принимается код очередной операции обработки данных, которую обе групп блоков 1-3 реализуют синхронно с контролем совпадения информации бл ком анализа. Для блокировки блока анализа.на время выполнения обмена одним из устройств 1 используется сигнал, наличияобмена, поступающий с выхода каждого формирователя на, соответствующий управлякл(ий вход блока анализа. Доступом в общую магистраль управляет Блок 4 доступа Приоритет одного из магистральны входов определяется сигналом на выходе триггера 6. При обнаружении от каза сигналом неисправности, поступающим на единичный или нулевой вхо триггер б устанавливается в состояние, соответствующее приоритету исправной группы блоков. В блоке 4 до ступа коммутатором.24, переключающи магистрали, управляет триггер 23. Первый 18 и второй 19 элементы И фо мируют сигнал разрешения доступа соответственно из первой и второй магистрали. Первый элемент 21 И-НЕ формирует сигнал запрета доступа одной из магистралей при наличии за проса из второй. Этим элементом управляет входной сигнал, приходящи в блок 4 с триггера 6. Второй элемент 22 И-НЕ и третий элемент 20 И устанавливают триггер 23, управляющий коммутатором, соответственно в нулевое и единичное значение. Изобретение позволяет обнаружить возникшие неисправности и повысить производительность системы за счет параллельного выполнения операций обработки данных и обмена. При обнаружении и локализации с помощью тестов неисправности работо способность системы сохраняется за счет снижения производительности, так как одно вычислительное устройство реализует и операции обмена и ведет обработку данных. Такая организация системы позволяет максималь но полно использовать имеющееся оборудование для увеличения производительности и надежности, что осо бенно важно для систем, к которым предъявляются жесткие требования по массе и габаритам аппаратуры. Формула изобретения 1. Система обработки данных, содержащая два вычислительных.устройства, два блока памяти микропрог рамм, первые и вторые выходы которых соединены соответственно с первым и вторым входами первого и второго,вычислительных устройств, а входы-выходя первого и второго вычислительных устройств соединены соответственно с первым и вторым выходом-входом блока организации доступа, третий вход-выход которого является входомвыходом системы, отличающаяся тем, что, с целью увеличения производительности и надежности, в нее введены два формирователя адреса, блок анализа и коммутатор, первый выход которого соединен с первым входом первого формирователя адреса, а второй выход коммутатора подключен к входу блока организации доступа и первому входу второго формирователя адреса, первые н вторые выходы формирователей адреса подключены соответственно к первым и вторым входам соответствующих блоков памяти микропрограмм, третьи и четвертые вы.ходы которых соединены соответственно с вторыми и третьими входами соогветствующих формирователей адреса, входы-выходы которых подключены соответственно к первому и второму выходам-входам блока организации доступа, первые выходы вычислительных устройств соединены с четвертыми входами соответствующих формирователей адреса, пятне входы которых соединены с первьдм выходом блока анализа, второй и третий выходы которого соединены соответственно с первым и.вторым входами коммутатора и подключены к шестым входам соответственно первого и второго формирователей адреса, седьмые входы которых подключены к вторым выходам соответственно второго и цервого вычислительных устройств, третьи выходы которых подключены соответственно к первому и второму входу блока анализа и соединены с восьмыми входами соответственно первого и второго формирователей адреса, а первый и второй входы-выходы подключены соответственно к первому и второму выходу-входу блока организации доступа. 2. Система по п.1, отличающая с я тем, что формирователь адреса содержит регистр кода one- . рации, вычислительный узел, регистр прерываний и элемент ИЛИ, выход которого подключен к первому входу вычислительного узла, второй и третий входы которого являются соответственно вторым и третьим входами формирователя,, а первый и второй выходы вычислительного узла являются соответственно первым и вторым выходом формирователя адреса, входом-выходом которого является входвыход регистра кода операции,вход которого является четвертым входом

формирователя адреса, первый, второ и третий, четвертый и пятый входы регистра прерываний являются соотвественно первым, пятым, шестым, седьмым и восьмым входами формирователя адреса, второй вход-выход регистра кода операции подключен к выходувходу вычислительного узла и выходувходу регистра прерываний, первый и второй выходы которого подключены соответственно к первому и второму входам элемента ИЛИ.

3. Система по, п,1, отличающая с я тем, что блок анализа содержит три триггера, три узла сравнения, счетчик и группу элементов И- НЕ, .первый и второй выходыкоторых соединены с входами соответственно первого и второго триггеров , выходы которых являются соответственно вторым и третьим выходами блока анализа, выходы первого и второго узлов сравнения и счетчика соединены соответственно с первыми, вторыми и третьими входами элементов И-НЕ группы, выход счетчика соединен с первым входом третьего триггера, выход которого соединен с входом счетчика и является первым выходом блока, второй вход третьего триггера подключен к выходу третьего узла сравнения, первый и второй входы которого являются соответственно первым и вторым входами блока, вход-выход первого узла сравнения и первый вход-выход третьего узла сравнения являются первым.выходом-входом блока анализа а вход-выход второго узла сравнения .и второй вход-выход третьего узла сравнения являются вторым входомвыходом блока.

4. Система по п.1, отличающая с я тем, что блок организации доступа содержит три элемента И, два элемента И-НЕ, триггер и коммутатор, первый и второй входвыход которого являются соответственно первым- и вторым входами-выходами блока, а третий вход-выход .коммутатора является третьим входомвыходом блока, выход первого элемента И-НЕ подключен к первому входу

o второго элемента И-НЕ, выход которого подключен к первому входу триггера и первому входу первого элемента И, выход которого соединен с вторым входом триггера, первый вы5ход которого подключен к входу коммутатора и первому входу второго элемента И, вторые входы первого и второго элементов И, первый вход первого элемента И-НЕ и выход второго элемента И соединены с первым

0 входом-выходом коммутатора, второй выход триггера подключен к первому входу третьего элемента И, а вторые входы третьего элемента И и второго элемента И-НЕ и выход третьего эле5мента И соединены с вторым входом- выходом коммутатора, а второй вход первого элемента И-НЕ является входом блока.

0

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 475145, кл. G Об F 15/46, 1973.

5

2.Патент tlUA № 3806887, кл. .G 06 F 11/00, 1974.

3.Патент Великобритании

№ .1466483,кл. G 06 F 11/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

| Устройство для управления обменом информацией накопителя на магнитной ленте с электронно-вычислительной машиной | 1983 |

|

SU1128245A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

..3

Авторы

Даты

1981-07-23—Публикация

1979-06-25—Подача