(54) СТАТИСТИЧЕСКИЙ НАКОПИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1973 |

|

SU646335A1 |

| Цифровой интегратор | 1981 |

|

SU1035605A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Устройство для контроля блоков оперативной памяти | 1976 |

|

SU615546A1 |

| Цифровой функциональный преобразователь | 1975 |

|

SU599265A1 |

| Устройство для синтаксического анализа программ | 1980 |

|

SU918950A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Устройство для обработки информации | 1973 |

|

SU624232A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1049968A1 |

| Оперативное запоминающее устройство с автономным контролем | 1982 |

|

SU1037349A1 |

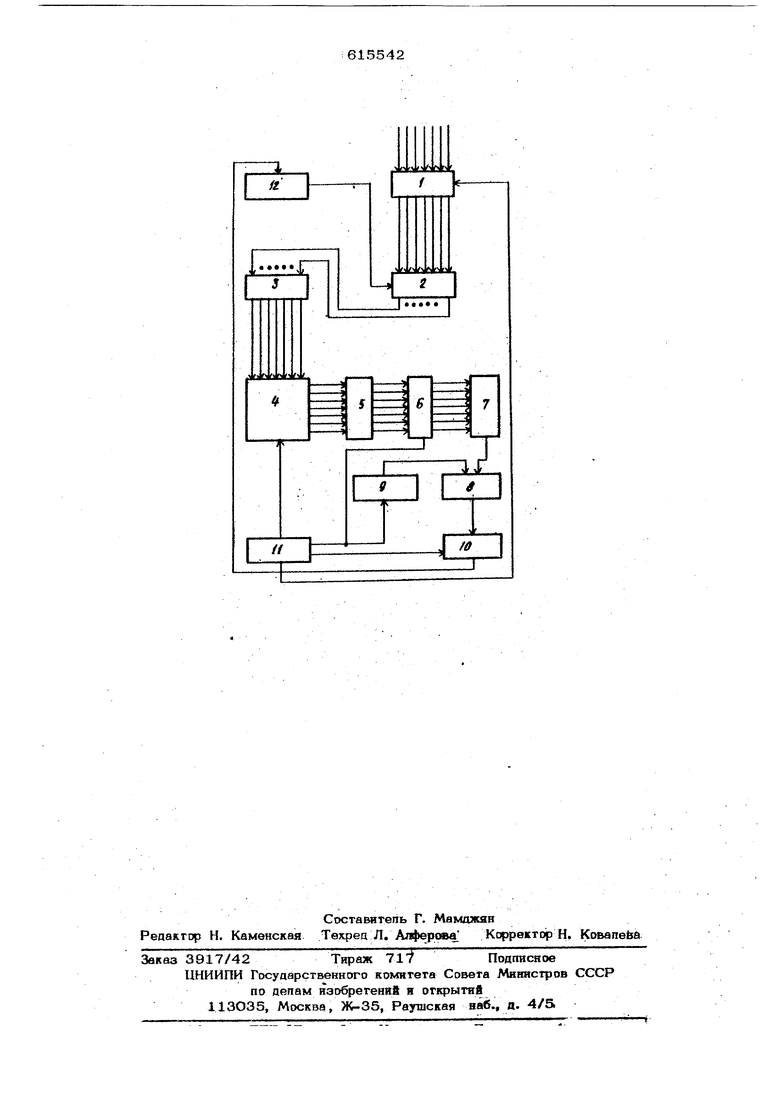

Изобретение, относится -к обпасти вьг чиспитепьной техники и может быть испопьзооано для накоппения статистических распредепений, например при -Спе ктрометрии проб внешней среды. Известен статистический накопитепь, содержащий псхзпедоватепьно вкпюченный входной регистр, формирователь адреса и регистр адреса, выходы которого подключены к адресным входам блока памяти, связанного с бпоком управления, а вых)ды блока памяти соединены со входами регистра числа р. . Цепь изобретения заключается в расши рении области применения накопителя. Поставленная цель достигается тем, что статистический накопитель содержит дешифратор, блок задания константы, дискримкнатор , счетчик, блок модификации адреса и эпементы И, ёходы которых под кпючеаы соответственно к выходам регис ра числа и блока управпения, а выходы ко входам дешифратора, выход которого соецинен с первым входом дискриминатора, второй вход которого подключен к вы ходу блока задания константы, а выход дискриминатора через счетчик и блок модификации адреса соединен с формировате лем адреса. Расширение обпасти применения устройства за счет автоматического изменения массиваiR(X) до вепичинь, пропцэционаггьной информативной составпяющей(Л(цф) попя |l)(X)5a уменьшения, вследствие этого, напожений достигается с помгащью вновь введенных блоков. Блок-схема статистического накопителя изображена на чертеже, где обозначено: входной регистр 1, формирователь адреса 2, регистр адреса 3, блок памяти 4 регистр числа 5f- эпементы И 6, дешифран тор 7, дискриминатор 8, блок задания кон-станты 9, счетчик 1О, блок управпения 11, блок модификации адреса 12. Общее время .измерения адаптивным статистическим накопитепем Т изм разбивается при помощи задатчика в{)еменных интервалов, расположенного внутри блока убавления 11, на три диапазона i Т иал i w « Mjw rtsw,. в Г5ромежугке вретчШни Ти yj enib--, чение числа отсчетов в канала; закопитэня происходит каждый раз при посгугтпепки на ,вхоа усгройсгва информационного собьгтия независимо от принадпежносги его к ипи информативной составпяющим о6 щего потока событий. Г1о окончании вре- Менного промежутка Т ,дм- памяти будет накоппен статистический спектр с отсчетами д ячейках в зависимости or вепйчин А,фи ,,.iKonH4ecTBo нагш жений при формированки адреса обращенкн к ячейкам накопителя будет гфопорционельно отношению Д; . , в промежуток времени опреде---пяегся абсолютная вепичина информатив-ной состаБПяющей tjHda 2вр®1Истрйрова1ь ной в ячейках накопитепя. Блок управпе- НИИ 11 вырабатывает разрешающий СИРнал, поступаюш.ий на вход бпока пажити 4. Содержимое ячеек накопителя, тгачиная с первой, поспедоватепьно выкосится на регистр числа 5.и поступает на первый вход эпеменг а И 6, При напичии разреша«« ющего jpoBHS на втором входе эпемента И, 6 от блока управпения-11 дешифратор Т преобразует содержимое ftanaiios паьи- тй дня сравнения его в дискриминаторе 8 с константой сравнения, ааданной з бпоке 9. Еспи число на выкоде дешифратора 7 превышает константу51ааааиную в бла-И ке 9, дискриминатор 8 вырабатывает им«- пупьс, увепичиваюнц й на единицу содержимое счетчнка Ю, После сравнения содержимого поспедней ячейки накопитейя с заданной константой двоичным с-ш-учаком Ю зафиксируется величина . равная общему количеству спучаев превышвниЕ заданной константы содержимого ячеек, н копителя. В конце временного проыежут--ка Т t43 сигнапу бпока управпения 11 производится перезапись в бпок мопифитса-ции,адреса 12 попученного значения Д . Бпок модификации адреса 12 изменяет разрядность формкроватегш адреса 2 в CG ответствии с хрангнцейся в нем зависимо- стью числа напгокений от запаса по памя ти .H попученного значений ДН t д к J- Работа адаптивного накопитейя в про- мажуткеТ,;;.;г:.А анаяогична работе Б течешй времени Тизм период времени . осзтдествгтяется статистическое накоплений, информационных событий с измененным пропорционально величине ЛИ попем адресов ). Использование вновь введенных блоков ,в схему накопителя выгодно отличает предлагаемое устройство or прототипа, гак как позволяет уменьшить количество напоженйй за счет выбора при помсяди блока модификации адреса такой величины массива, ааресов, которая пропорциональна информативкой составляющей общего потока собьк гай А мф . В результате можег быть расширена область применения накс пигеля ДЛИ систем с большой частотой поступпения событий, поскольку время доступа в произвольную ячейку накопитегш уменьшается пропорционально копичесгву ; Ев-пожений.. Формула иаобре чтения Статистический накопитель, содержащий последовательно включенные входной регистр, формирователь адреса и регистр attреса, выходы которого подключены к адресным входам блока памяти связанного, с блоком у1травления, а выходы блока памяти соединены со входами регистра числа, о т а Ъ щ и и с я тем, что, с цепью расширения области применения накопителя, ОИ содержит дешифратор, блок, задания, константы, дискриминатор, счетчик,, .блок модификации адреса и элементы.И, вхосйы которых подключены соответственно к выходам регисгра и блока управпения, а выходы - кр -зходам дешифратора, выход которого соединен с первым входом дискриминатора, второй вход которого подключен к выходу блока задания константы, а выход днокриминагора через счетчик и блок модифи кации адреса соединен с формирователе / адреса. Источники информации, принятые во BHHMairtie при экспертизе: 1. Авторское свидетельство СССР К 478359, кл, С|11 С 7/ОО, 1975.

cm,, ч

//

u (As

5 s л fi ь :i

j:

T

.j

Авторы

Даты

1978-07-15—Публикация

1976-04-06—Подача