(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКСе ОПЕРАТИВНОЙ

ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля матриц памяти | 1980 |

|

SU898507A1 |

| Цифровой статистический анализатор случайных интервалов времени | 1980 |

|

SU943745A1 |

| Устройство для контроля блоковОпЕРАТиВНОй пАМяТи | 1979 |

|

SU832603A1 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1594610A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для контроля логических блоков | 1981 |

|

SU1016786A1 |

| Запоминающее устройство | 1973 |

|

SU646335A1 |

| Резервированное многоканальное запоминающее устройство | 1980 |

|

SU942142A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

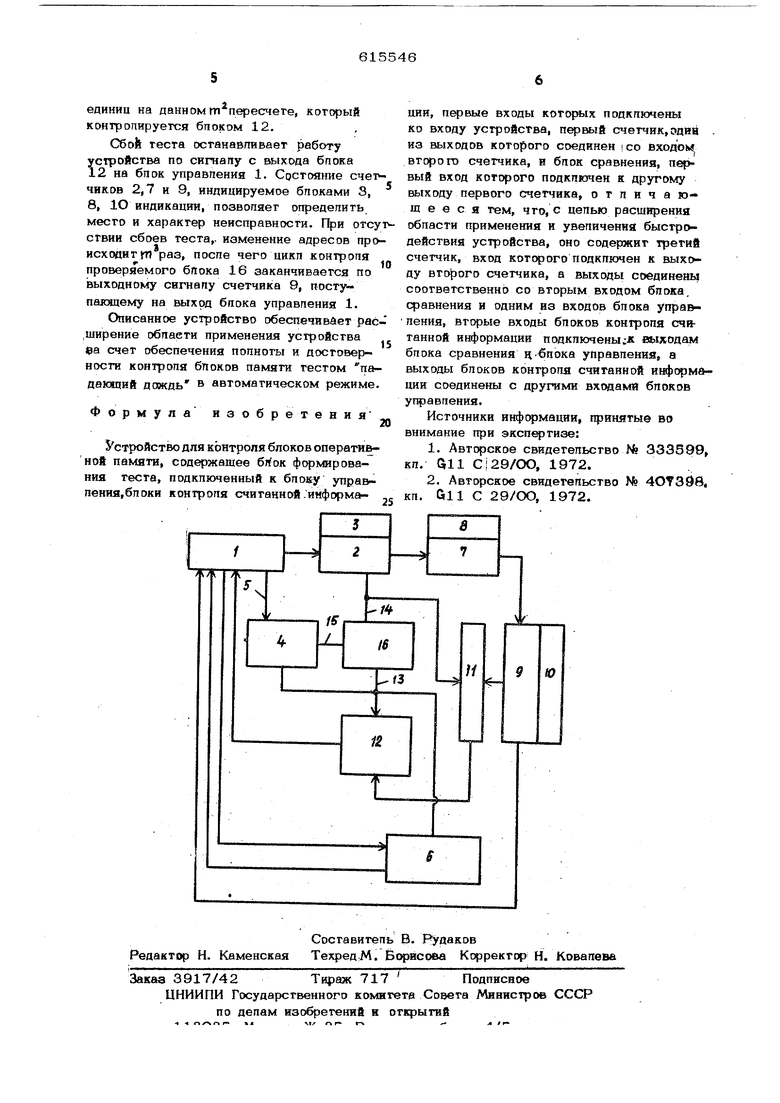

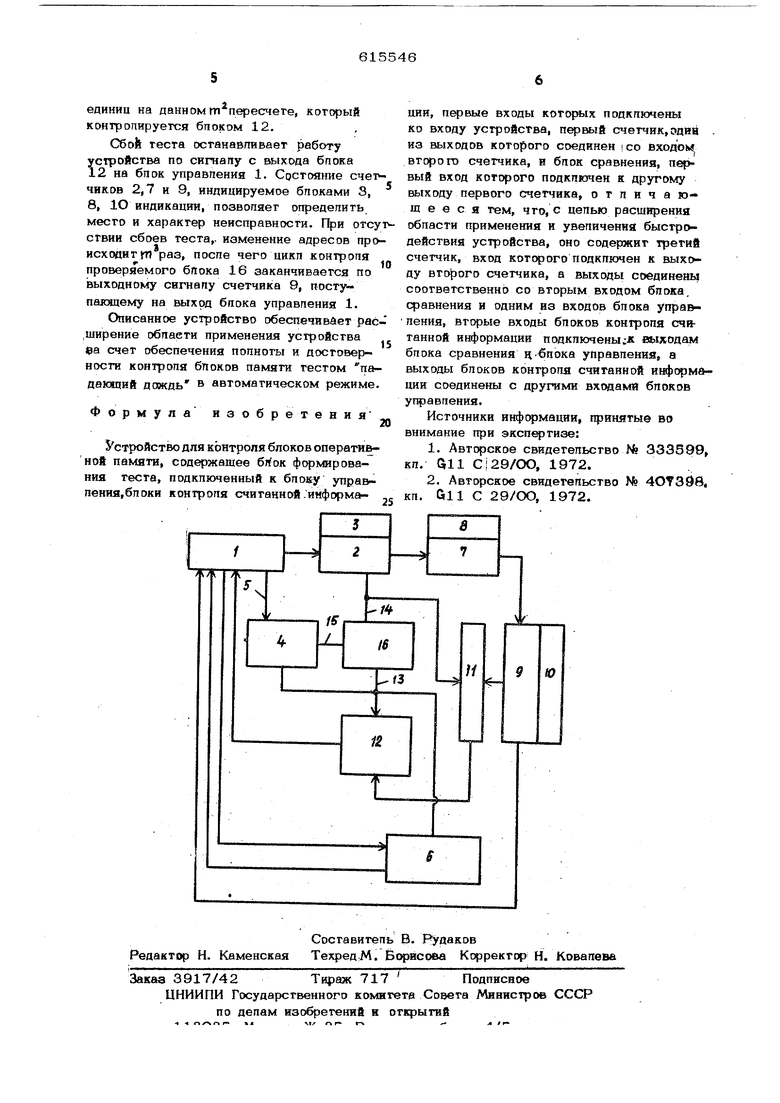

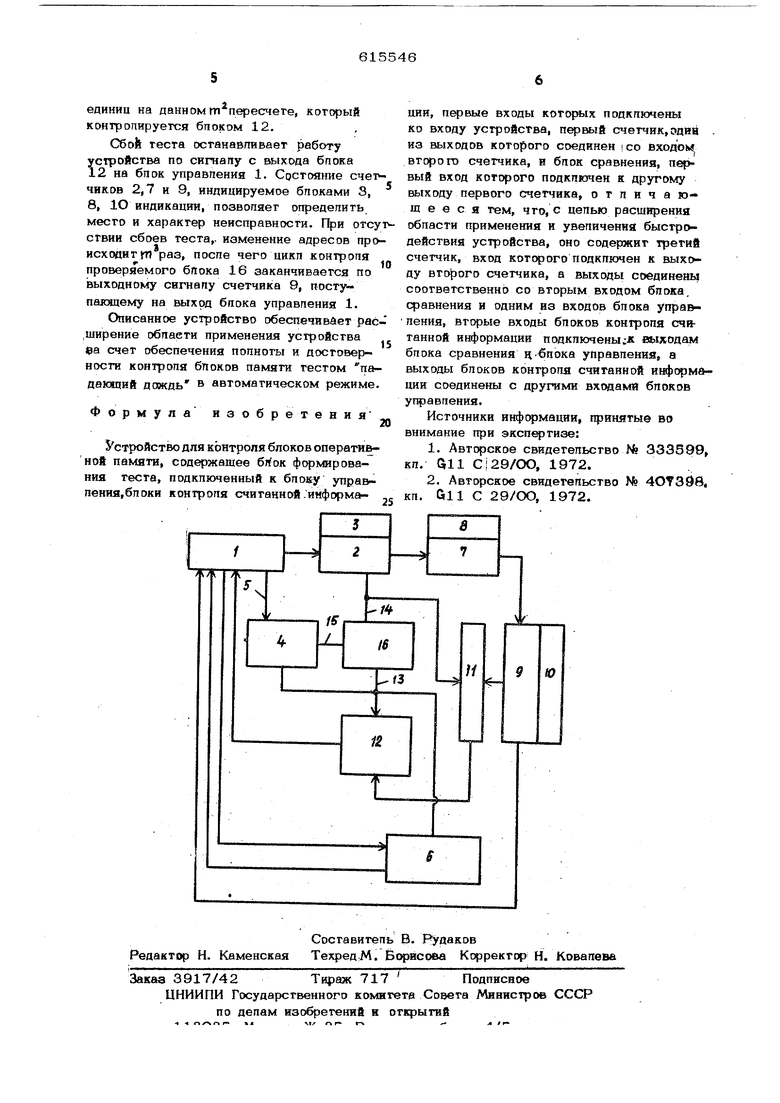

Изобретение касаетх;я аапоминакяцих усгройсгв. Известно устройство дпя контроля блоков оперативной памяти, содержащее опок свертки по модулю два, подключенный к регистрам, бпок сравнения, подключенный к выходам триггеров контрольных paapsfдов регистров и к выходам блока свертки по модулю два, блок преобразования кон1 рольных разрядов l . Недостатком этого устройства авпяется то, что в нем не предусмотрен контроль проверяемого блока, оперативной памяти тестом падающий дождь , что снижает полноту контроля. Наиболее близким техническим решением к данному изобретению явпяется уст ройство для контроля блоков оперативной памяти, содержа1цёе бпок. формирования теста, подключенный к блоку управления, блоки контроля считанной инфорМации, пер вые входы которых подключены ко входу устройства, первый счетчик, один из выходов которого соединен со входом втг рого счетчика, и бпок сравнения, периый вход которого подключен к гфугому первого счетчика 2j , Недсхзтатком этого устройства явпяв ся то, что прохоокдение в нем геста контролируется визуально оператором, что cmih ;жает CKq)tx:Tbf проверки испытуемого бпока памятя, а та(же сужественво огракичавает обпасгь применения згстройства. Цепью изобретения явпяегся расшнревнв обпасти применения и увепичение быстро действия устройства. Псюгавпевваа цепь досгягается гем, что предпагаемое устройство соавржвг фетнй счетчик, вход которого поакпкпен к выхщу вгорого счегчнка, а выходы соединены соотвегсгвенно со вторым входом блока сравнения я одним яэ входов блока управяения, вторые входы бпоков контроля считанной ипформапяв подключены к выходам блока сравнения и бпока утфавпеиия, а илходы бпоков контроля считанной квформаднв соединены с другвмя вхо дамн бпоков управления На чертеже показано предлагаемое устройство. Устройство содержит бпок управпения 1, первый счетчик 2, служащий дпя формирования кода адреса, к которому подключен бпок индикации 3, бпок формирования теста 4, вход 5 которого подключ к блоку управпения 1, бпок конгропя с штайной информации 6, второй счетчик 7 с бпоком индикации 8, третий счетчик 9 с блоком индикации Ю, блок сравнения И первый вход которого соединен с выходо счетчика 2, бпок контропя считанной инф мации 12. Первые входы блоков 6 и 12 подключены ко входу 13 устройства, выходы 14 и 15 которого соединены соответственно с выходами счетчика 2 и бло 4. Вторые входы блоков 6 и 12 подключены соответственно к выходам блоков 1 и 11, а выходы ко входам блока управпе ния 1. Вход счетчика 9 подключен к выходу второго счетчика 7, а выходы соединены соответственно со вторым входом блока 11 и одним из входов блока управления 1. Ко входу 13 и выходам 14 и 15 подключается контролируемый бпок оператив ной памяти 16. Устройство при контроле пров яемогс блока 16 тестом падакший дождь работает следующим образом, В, исходном состоянии счетчики 2 и 7 устанавливаются в нулевое состояние, вычитающий счетчик 9 в состояние т. ( где УП - максимальный адрес блока 16), в нулевую ячейку контролируемого блока 16 записывается код, содержащий . единицы во всезс разрядах, во всех оотельных ячейках распопонсены нулевые коды (содержащие нули во всех разрядах После пуска устройства происходит пересчет адресов контролируемого блока 16 счетчиком 2. При этом обеспечивае-П ся последовательное чтение ( с регенерацией) кодов из всех ячеек блока 16. Содержимое ячейки oL.-, образующееся при п - пересчете адресов выредсаегся формулой K).®(i-).,: ,знак означает пс зазрядную операцию слгакения по модулю 2(1 О, l,2...,tTi) Переход OT-j -го к ()-му адресу яроизводится путем спожения по модули ( In +1)| то есть o)m )n-i ® (m nФормирование теста, в соогветсгвни с приведенным законом, произвооигся Блок 6, служащий для контрогея идентичности единичной или нулевой информации во всех разрядах контролируемой ячейки после контроля каждого из считанных кодов, выдает сишал разрешения или запрещения работы на блок управления 1. После пуска устройства, в нулевую ячейку контролируемого блока 16 повторно будет записан код с единицами во всех разрядах. Далее, при пересчете адресов счетчиком 2, в первую и все последук щие ячейки будет записан код со всеми единицами. При следующем пересчете содержимое четных ячеек не изменяется, а в нечетных образуется пустой код. После того как, считая от исходного момента, адрес изменится :на единицу tn раз, код содержащий все единицы, остается только в ячейке с адресом tin, Когда адрес контрогаируемого блока 16 изменен еще № раз, то код со всеми единицами будет- распбйожен в ячейках с адресами tn- 1 и hi, после следующих УЛ изменений - в ячейках с адресами т- 2, т- 1, уп . После.того, как изменение адресов произойдет т раз, код, со .держащий единицы, окажется во всех ячейках контролируемого блока 16. При этом, в течение первых W изменений адресов контролируемого блока 16, которые отсчитываются счетчиками 2 и 7, код всех единиц постоянно хранится в ячейке блока 16с адресом Гп и контролируется при каждом считывании блоком 12, служащим |для контроля единичной информации в ячейке, по команде с вььхода блока 11 сравнения, которая формируется после совпадения кода адреса, поступившего со счетчика 2, и кода с выхода счетчика 9. После первых m пересчетов, по ылходному сигналу счетчика 7, состояние счетчика 9 изменяется на TTV 1. В теч&ние следующих мп зменений адресов конгропируемого бпока 16 счетчиком 2, которые отсчитываются счетчиком 7, код, содержащий все единицы, постоянно хра. нится в ячейке контролируемого блока 16 с адресом Ггь 1 и контролируется при каждом считывании блоком 12 аналогично контролю при первых m Изменениях адресов. После вторых m пересчетов адресов состояние счетчика 9 изменяется на hi- 2 t затем ш- 3 н так далее. При этом состояние счетчика 9 на каждом п пересчетв адресов контролируемого 1 fit ЧЧ f ИЛ I .г« л rt л ft IVA.

Авторы

Даты

1978-07-15—Публикация

1976-12-16—Подача