..х

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК В ВЫХОДНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2006971C1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Резервированное запоминающее устройство | 1984 |

|

SU1239751A2 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Резервированное запоминающее устройство | 1979 |

|

SU881875A2 |

| Устройство для контроля хода программ | 1988 |

|

SU1545223A1 |

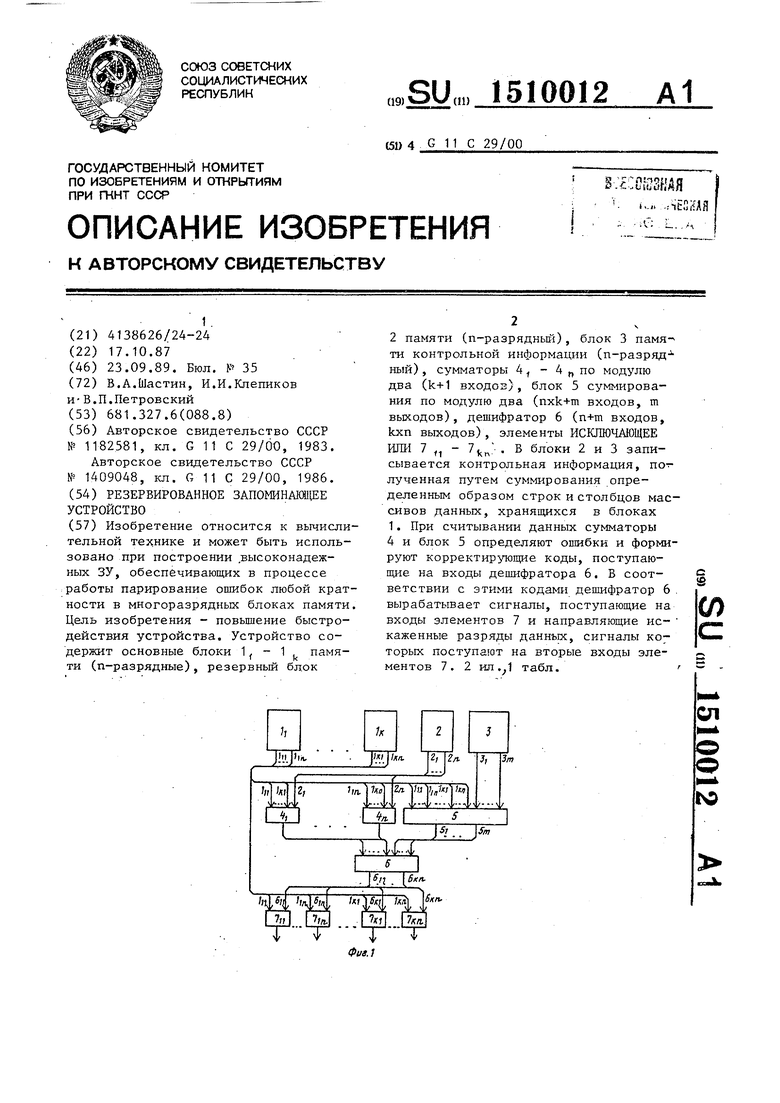

Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежных ЗУ, обеспечивающих в процессе работы парирование ошибок любой кратности в многоразрядных блоках памяти. Цель изобретения - повышение быстродействия устройства. Устройство содержит основные блоки 11-1K памяти (N-разрядные), резервный блок 2 памяти (N-разрядный), блок 3 памяти контрольной информации (N-разрядный), сумматоры 41-4N по модулю два (K+1 входов), блок 5 суммирования по модулю два (N.K+M входов, M выходов), дешифратор 6 (N+M входов, K.N выходов), элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 711-7 KN). В блоки 2 и 3 записывается контрольная информация, полученная путем суммирования определенным образом строк и столбцов массивов данных, хранящихся в блоках 1. При считывании данных сумматоры 4 и блок 5 определяют ошибки и формируют корректирующие коды, поступающие на входы дешифратора 6. В соответствии с этими кодами дешифратор 6 вырабатывает сигналы, поступающие на входы элементов 7 и направляющие искаженные разряды данных, сигналы которых поступают на вторые входы элементов 7. 2 ил.

Ш... ... Ш...

3 151001:

Изобретение относится к вычисли- i ельной технике и может быть испольовано при построении высоконадежых запоминающих устройств, обеспе- с чивающих в процессе работы парироваие ошибок любой кратности в многоазрядных блоках памяти.

Цель изобретения - поньшение быстродействия устройства,10

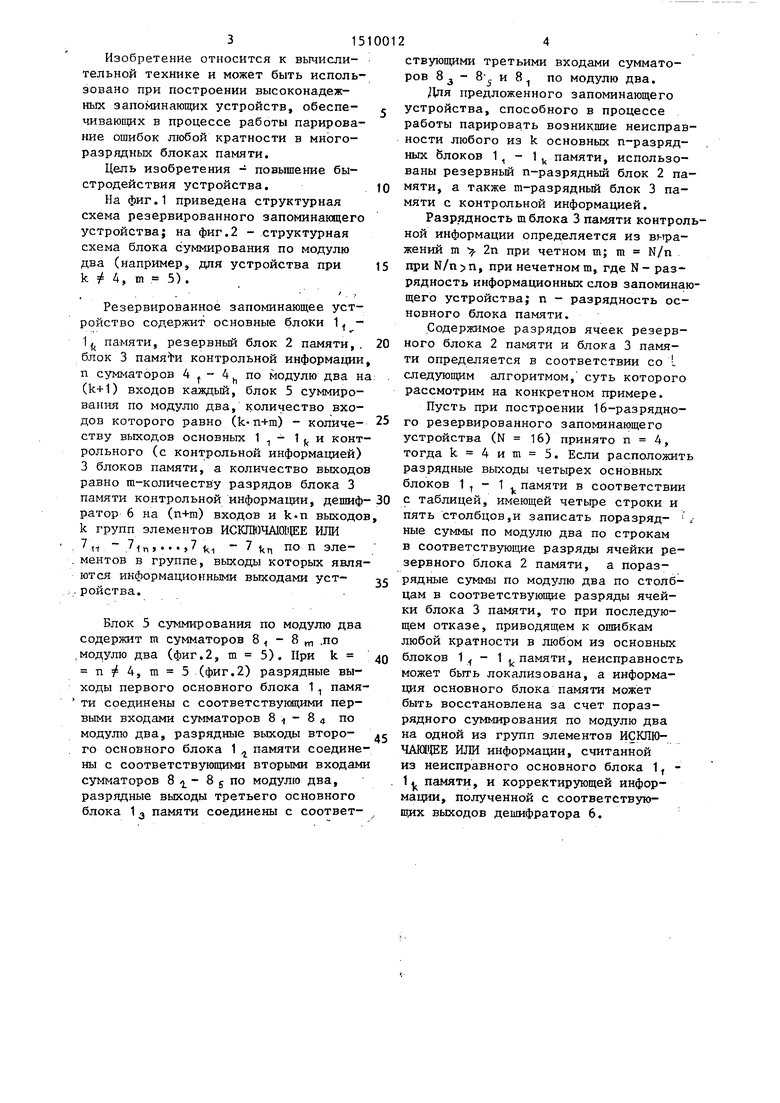

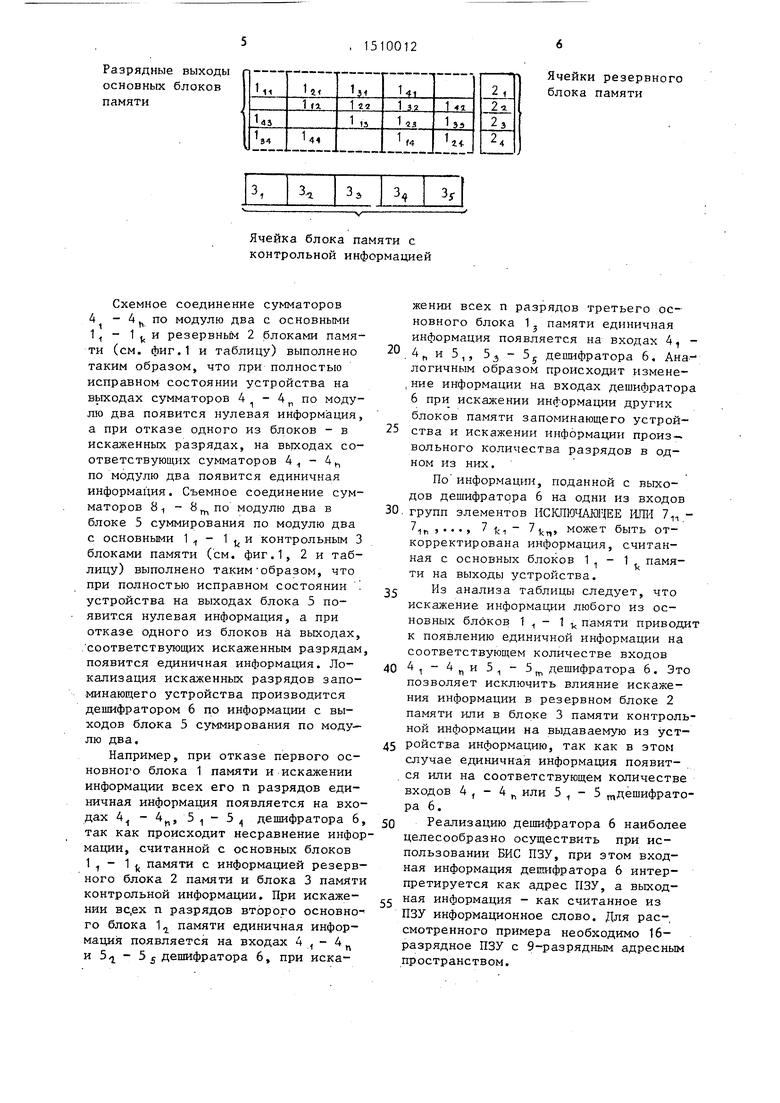

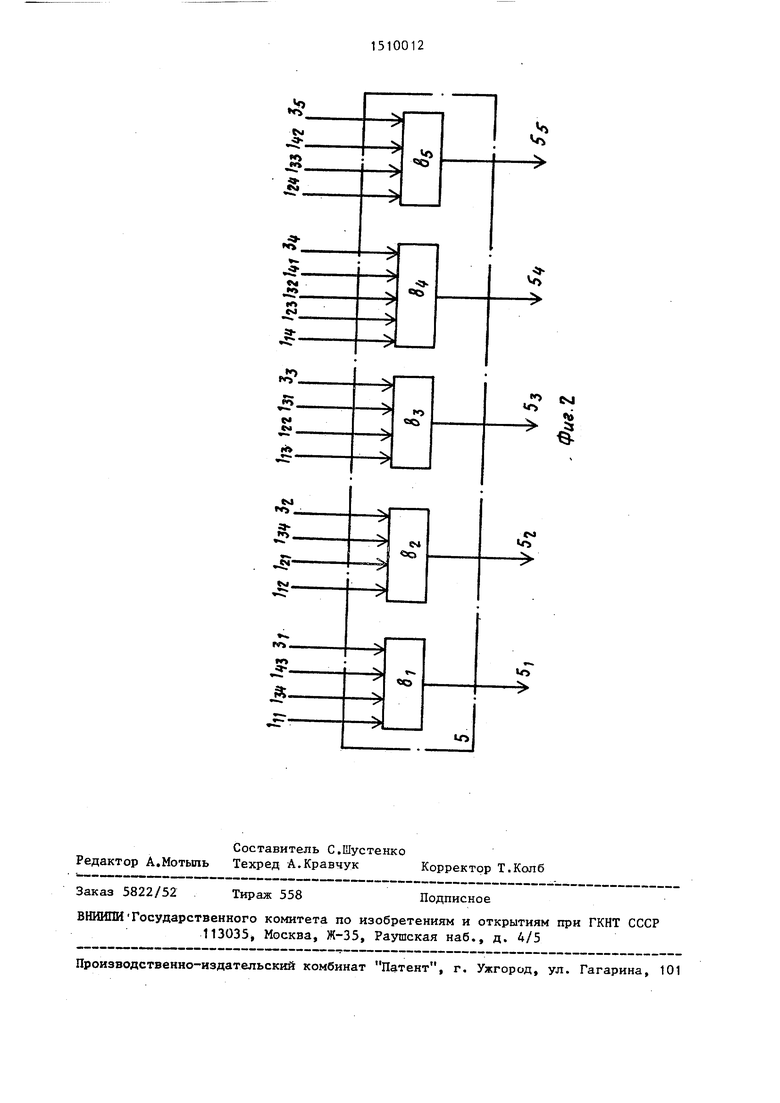

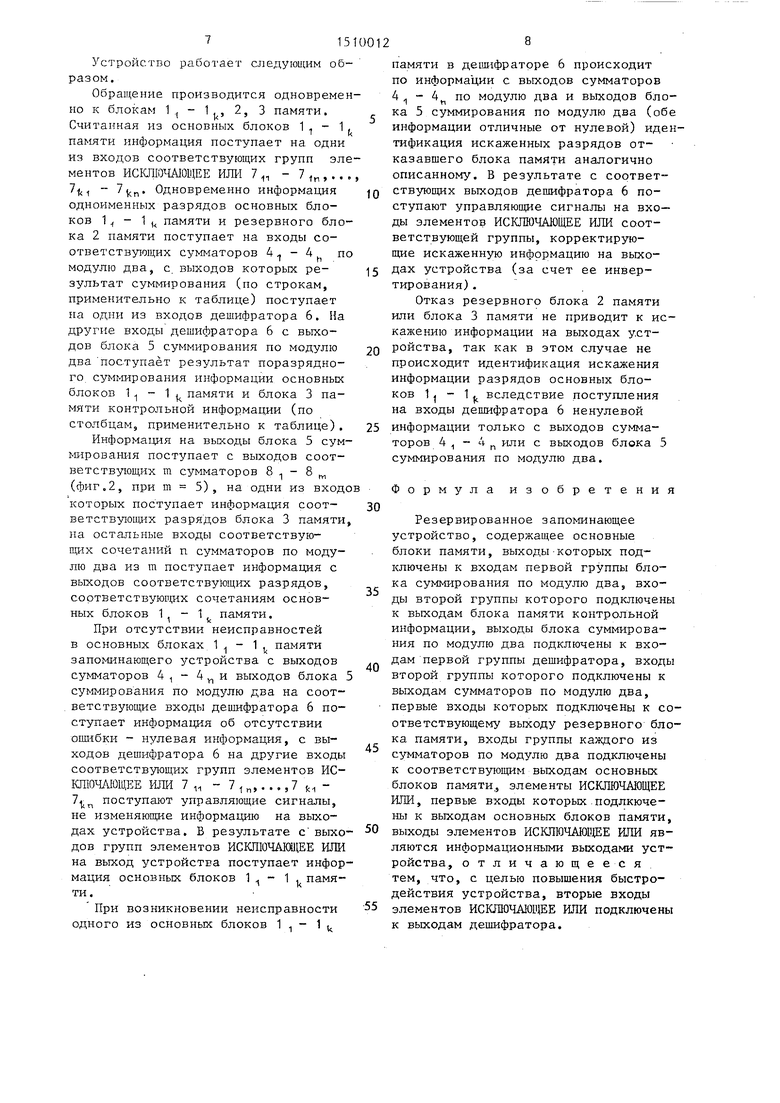

На фиг.1 приведена структурная схема резервированного запоминакщего стройства; на фиг.2 - структурная схема блока суммирования по модулю ва (например, для устройства при 15 4 4, m 5).

/ .

Резервированное запоминающее устойство содержит основные блоки памяти, резервный блок 2 памяти,, 20 блок 3 памя 1 и контрольной информации, п сумматоров 4 - 4 по модулю два на . (k+1) входов каждый, блок 5 суммирования по модулю два, количество входов которого равно (k-n+m) - количе- 25 ству выходов основных 1 - 1 {( и контрольного (с контрольной информацией) 3 блоков памяти, а количество выходов равно т-количеству разрядов блока 3 памяти контрольной информации, дешиф- 30 ратор 6 на (n+m) входов и k-n выходов, k групп элементов ИСКШ)ЧА101ЦЕЕ ИЛИ

11 71п i.;i 7 kn ПО П эле- ментов в группе, выходы которых являются информационными выходами уст- 05 ройства.

Блок 5 с.уммирования по модулю два содержит m сумматоров 8 - 8 .по

модулю два (фиг.2, m 5). При k 40 п f 4, m 5 (фиг.2) разрядные выходы первого основного блока 1 , памяти соединены с соответствующими первыми входами сумматоров по модулю два, разрядные выходы второ- g го осноззного блока 1 памяти соединены с соответствующими вторыми входами сумматоров 8 - 8 по модулю два, разредные выходы третьего основного блока 1 ч памяти соединены с соответ -. ,

ствующими третьими входами сумматоров 8 д - 8 и 8 по модулю два.

Для предложенного запоминающего устройства, способного в процессе работы парировать возникшие неисправности любого из k основных п-разряд- ных блоков 1, - 1 памяти, использованы резервный п-разрядный блок 2 памяти, а также т-разрядный блок 3 памяти с контрольной информацией.

Разрядность m блока 3 памяти контролной информации определяется из вьтра- жений m 2п при четном т; га N/n при N/n п, при нечетном т, где N - разрядность информационных слов запоминающего устройства; п - разрядность основного блока памяти.

Содержимое разрядов ячеек резервного блока 2 памяти и блока 3 памяти определяется в соответствии со L следующим алгоритмом, суть которого рассмотрим на конкретном примере.

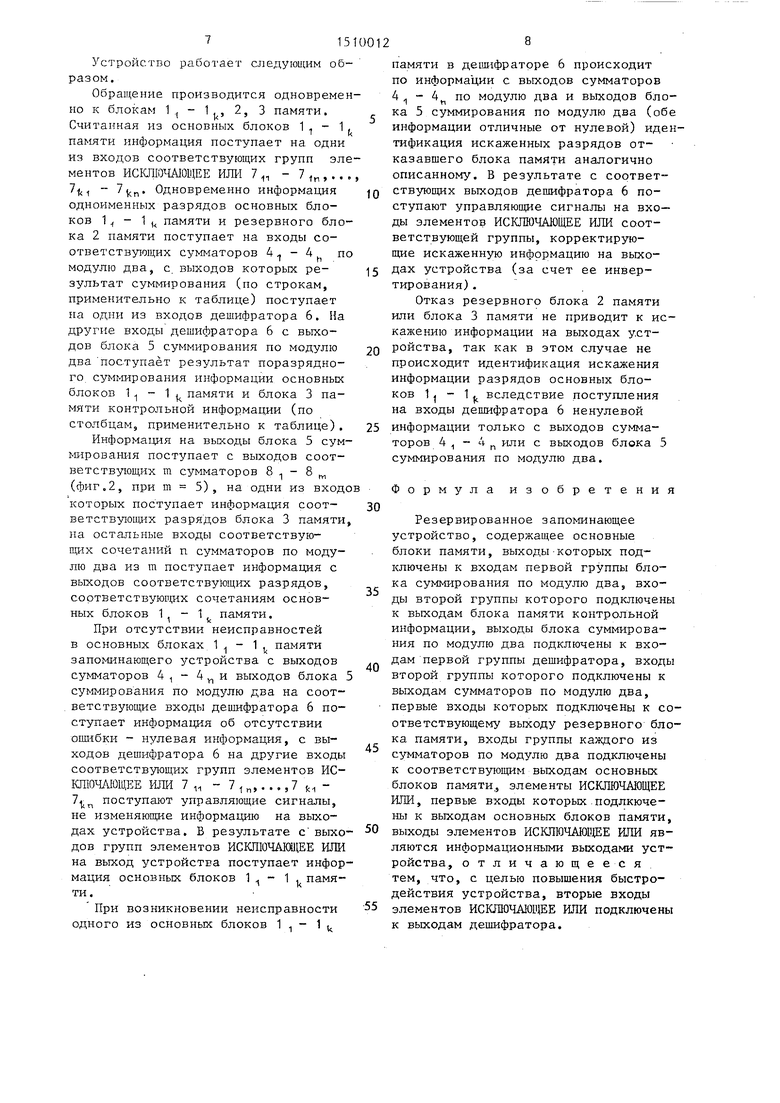

Пусть при построении 16-разрядного резервированного запоминающего устройства (N 16) принято п 4, тогда k 4 и m 5. Если расположит разрядные выходы четырех основных блоков 1 , - 1 памяти в соответствии с таблицей, имеющей четыре строки и пять столбцов,и записать поразряд- ные суммы по модулю два по строкам в соответствующие разряды ячейки резервного блока 2 памяти, а поразрядные суммы по модулю два по столбцам в соответствующие разряды ячейки блока 3 памяти, то при последующем отказе, приводящем к ошибкам любой кратности в любом из основных блоков памяти, неисправность может быть локализована, а информация основного блока памяти может быть восстановлена за счет поразрядного суммирования по модулю два на одной из групп элементов ИСКЛЮ- ЧАМ ЩЕ ИЛИ информадаи, считанной из неисправного основного блока 1 - }. памяти, и корректирующей информации, полученной с соответствующих выходов дешифратора 6.

Разрядные выходы основных блоков памяти

Ячейка блока памяти с контрольной информацией

Схемное соединение сумматоров 4 - 4 по модулю два с основными 1 - 1 jj и резервньм 2 блоками памяти (см. фиг.1 и таблицу) выполнено таким образом, что при полностью исправном состоянии устройства на вьпсодах сумматоров 4 - 4 по модулю два появится нулевая информация, а при отказе одного из блоков - в искаженных разрядах, на вькодах соответствующих сумматоров 4 - 4, по модулю два появится единичная информация. Съемное соединение сумматоров 8 - 8 по модулю два в блоке 5 суммирования по модулю два с основными 1 1 - 1 t и контрольным 3 блоками памяти (см. фиг.1, 2 и таблицу) выполнено таким-образом, что при полностью исправном состоянии . устройства на выходах блока 5 появится нулевая информация, а при отказе одного из блоков на выходах, /соответствующих искаженным разрядам появится единичная информация. Локализация искаженных разрядов запоминающего устройства производится дешифратором 6 по информации с выходов блока 5 суммирования по модулю два.

Например, при отказе первого основного блока 1 памяти и искажении информации всех его п разрядов единичная информация появляется на входах 4 - 4, дешифратора 6 так как происходит несравнение инфомации, считанной с основных блоков 1 - 1 (j памяти с информацией резервного блока 2 памяти и блока 3 памят контрольной информации. При искажении зс.ех п разрядов второго основно го блока 1 памяти единичная информация появляется на входах 4 - 4 и 5 - 5J дешифратора 6, при искаЯчейки резервного блока памяти

жении всех п разрядов третьего основного блока 1J памяти единичная информация появляется на входах - 4 и 5,, 5 - 5 дешифратора 6. Ана-- логичным образом происходит изменение информации на входах дешифратора 6 при искажении информации других блоков памяти запоминающего устройства и искажении информации произ-« вольного количества разрядов в одном из них.

По информации, поданной с выходов дешифратора 6 на одни из входов групп элементов НСКЛЮ ШОЩЕЕ 1ШИ 7

1п

7f.,- 7

,

может быть от

корректирована информация, считанная с основных блоков памяти на выходы устройства.

Из анализа таблицы следует, что искажение информации любого из основных блоков 1 ., - 1 памяти приводит к появлению единичной информации на соответствующем количестве входов

Ч

позволяет исключить влияние искажения информации в резервном блоке 2 памяти или в блоке 3 памяти контрольной информации на выдаваемую из устройства информацию, так как в этом случае единичная информация появится или на соответствующем количестве входов или (Дешифрато- ра 6.

Реализацию дешифратора 6 наиболее целесообразно осуществить при использовании БИС ПЗУ, при этом входная информация дешифратора 6 интерпретируется как адрес ПЗУ, а вькодная информация - как считанное из ПЗУ информационное слово. Для рассмотренного примера необходимо 16- разрядное ПЗУ с 9-разрядным адресным пространством.

Устройство работает следующим образом.

Обращение производится одновремен2, 3 памяти.

но к блокам 1 ,, - 1 , ,

Считанная из основных блоков , памяти 1 нформация поступает на одни из входов соответствующих групп элементов ИСКШОЧАЮЩЕЕ ИЛИ 7

11

- 7

In

( 1 kn Одновременно информация Q одноименных разрядов основных блоков памяти и резервного блока 2 памяти поступает на входы со- ответствзпощих сумматоров А - 4 по модулю два, с выходов которых результат суммирования (по строкам, применительно к таблице) поступает на одни из входов дешифратора 6. На другие входы дешифратора 6 с выходов блока 5 суммирования по модулю два поступает результат поразрядного суммирования информации основных блоков 1 1 - 1 1 памяти и блока 3

мяти контрольной информации (по столбцам, применительно к таблице).

Информация на выходы блока 5 суммирования поступает с выходов соответствующих m сумматоров 8 - 8 „ (фиг.2, при m 5), на одни из входов которых поступает информация соот- ветствуюишх разрядов блока 3 памяти, на остальные входы соответствующих сочетаний п сумматоров по модулю два из m поступает информация с выходов соответствующих разрядов, сортветствуюищх сочетаниям основных блоков 1, 1 памяти.

При отсутствии неисправностей в основных блоках памяти запоминающего устройства с выходов сумматоров 4 , - 4 и выходов блока 5 суммирования по модулю два на соответствующие входы дешифратора 6 поступает информац 1я об отсутствии ошибки - нулевая информация, с выходов дешифратора 6 на другие входы соответствующих групп элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 1, - 7 1 „,..., 7 fc - 7 поступают управляющие сигналы, не изменяющие информацию на выходах устройства. В результате с выходов групп элементов ИСКЛЮЧАКЩЕЕ ИЛИ на выход устройства поступает информация основных блоков памяти.

При возникновении неисправности одного из основных блоков 1 1 - 1 и

15100128

памяти в дешифраторе 6 происходит по информации с выходов сумматоров 4 - по модулю два и выходов блока 5 суммирования по модулю два (обе информации отличные от нулевой) идентификация искаженных разрядов отказавшего блока памяти аналогично описанному. В результате с соответствующих выходов дешифратора 6 поступают управляюшр е сигналы на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответствующей группы, корректирую- щке искаженную информацию на выхоj5 дах устройства (за счет ее инвертирования) .

Отказ резервного блока 2 памяти или блока 3 памяти не приводит к искажению информации на выходах у.ст20 ройства, так как в этом случае не происходит идентификация искажения информации разрядов основных бло- па- ков 1J - 1 j вследствие поступления на входы дешифратора 6 ненулевой

25 информации только с выходов сумматоров 4 - 4 или с выходов блока 5 суммирования по модулю два.

Формула изобретения

35

40

30

Резервированное запоминающее

устрохЧство, содержащее основные блоки памяти, выходы-которых подключены к входам первой группы блока суммирования по модулю два, входы второй группы которого подключены к выходам блока памяти контрольной информации, выходы блока суммирования по модулю два подключены к входам первой группы дешифратора, входы второй группы которого подключены к выходам сумматоров по модулю два, первые входы которых подключены к соответствующему выходу резервного блока памяти, входы группы каждого из сумматоров по модулю два подключены к соответствуюш им выходам основных блоков памяти., элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых-подлкюче- ны к выходам основных блоков памяти,

50 выходы элементов ИСКЛЮЧАЮ1ЧЕЕ ИЛИ являются информационными выходами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, вторые входы

55 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходам дешифратора.

45

Резервированное запоминающее

устрохЧство, содержащее основные блоки памяти, выходы-которых подключены к входам первой группы блока суммирования по модулю два, входы второй группы которого подключены к выходам блока памяти контрольной информации, выходы блока суммирования по модулю два подключены к входам первой группы дешифратора, входы второй группы которого подключены к выходам сумматоров по модулю два, первые входы которых подключены к соответствующему выходу резервного блока памяти, входы группы каждого из сумматоров по модулю два подключены к соответствуюш им выходам основных блоков памяти., элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых-подлкюче- ны к выходам основных блоков памяти,

выходы элементов ИСКЛЮЧАЮ1ЧЕЕ ИЛИ являются информационными выходами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, вторые входы

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходам дешифратора.

Составитель С.Шустенко Редактор А.Мотыль Техред А.Кравчук Корректор Т.Колб

Заказ 5822/52

Тираж 558

ВНИИПИТосударственного комитета по изобретениям и открытиям при ГКНТ СССР 1l3035j Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Многоканальное мажоритарно-резервированное запоминающее устройство | 1983 |

|

SU1182581A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1409048A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-09-23—Публикация

1987-10-17—Подача