Изобретение относится к запоминак щим устройствам.

По основному авг, св. Ма 526952 изйестно устройство дпя контроля блоков памяти, содержащее блок памяти, блок

управления, блок сравнения, формирователь кодов, счетчик числа обращений, счетчик математический ожиданий, генератор случайных чисел и сумматор, при-чем вход блока управления соединен с выходом блока сравнения, одна группа входов которого соединена с выходными шинами блока памяти, а вторая группа- с выходами формирователя кодов, выходы которого соединены с адресными шина ми блока памяти, вход счетчика числа обращений соединен с выходом блока управления, а выход - со входом счетчика, математических ожиданий, выходы которого и выходы генератора случайных чисел подключены к соответствующим входам сумматора, выходы сумматора соединены с адресными шинами блока памяти.

Недостатком этого устройства являет ся то, что коды адресов и последователь-

ность их подачи на ащэесные шины, будучи однажды получены, вторично воспроиэведены быть уже не могут, теряются для пользователя, так как формирование адреоной информации происходи- по случайному закону. Иными словами, коды адрес и последовательность их подачи на ащэеоные шины, создавшую сбойную ситуацию в проверяемом блоке, не могут быть предоставлены пользователю для их анализа и не могут быть многократно повторены с целью конкретизации сбойной ситуации в проверяемом блоке, например, посредством визуальных средств контроля. Это снижает область применения устройства.

Целью изобретения является расширение области применения устройства и повышение оперативности контрот.

Поставленная цель достигается тем, что предлагаемое устройство содержит логический блок и дополнительный блок памяти, управляющий вход которого соединен с одним из вйгходов блока управления, адресные входы - с информационными выходами счетчика числа обращений, информа ционныб входы . с выходами сумматора и первыми информационными входами логического блока, выходы - со вторыми информационными входами логического блока, управлякнций вход логического блока соединен с щ)угим выходом блока управления, а выходы - с ад ресными входами блока памяти и входами формирователя кодов.

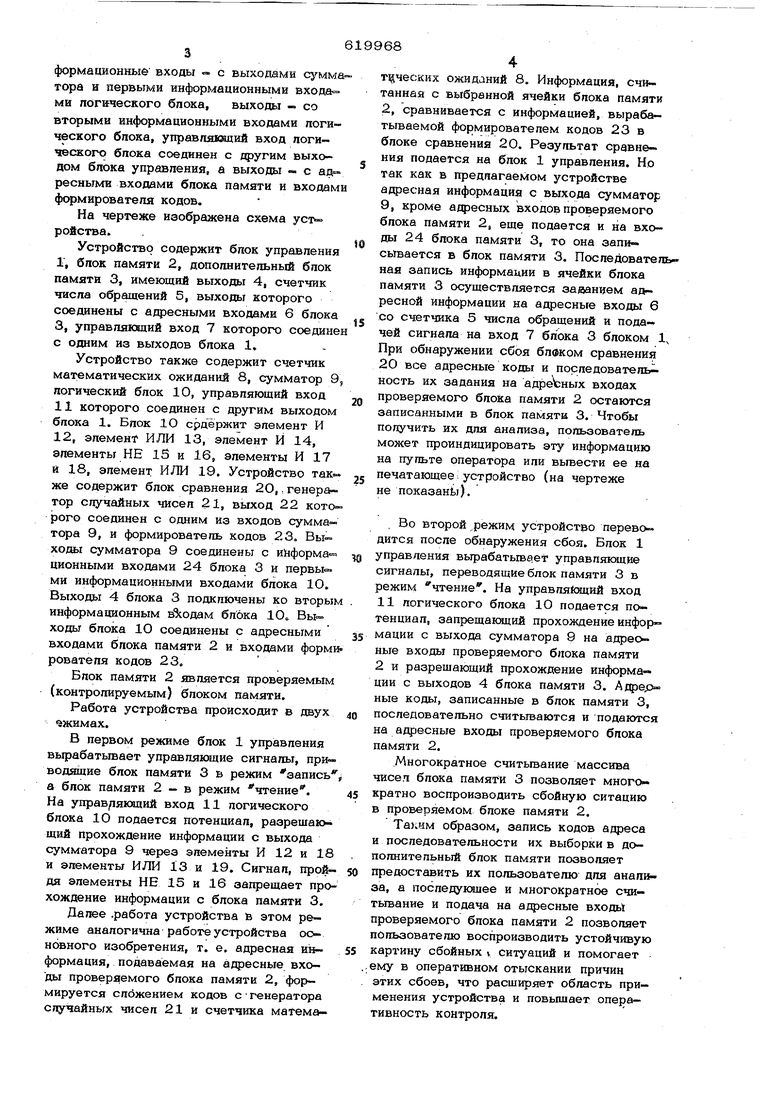

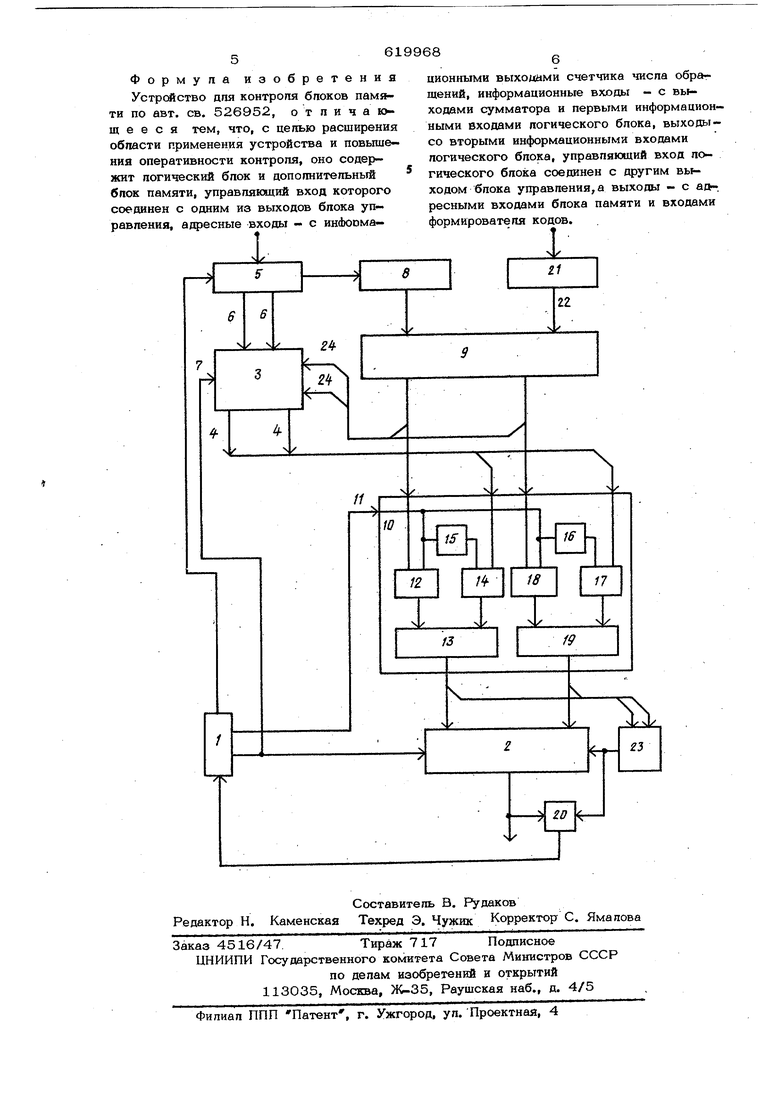

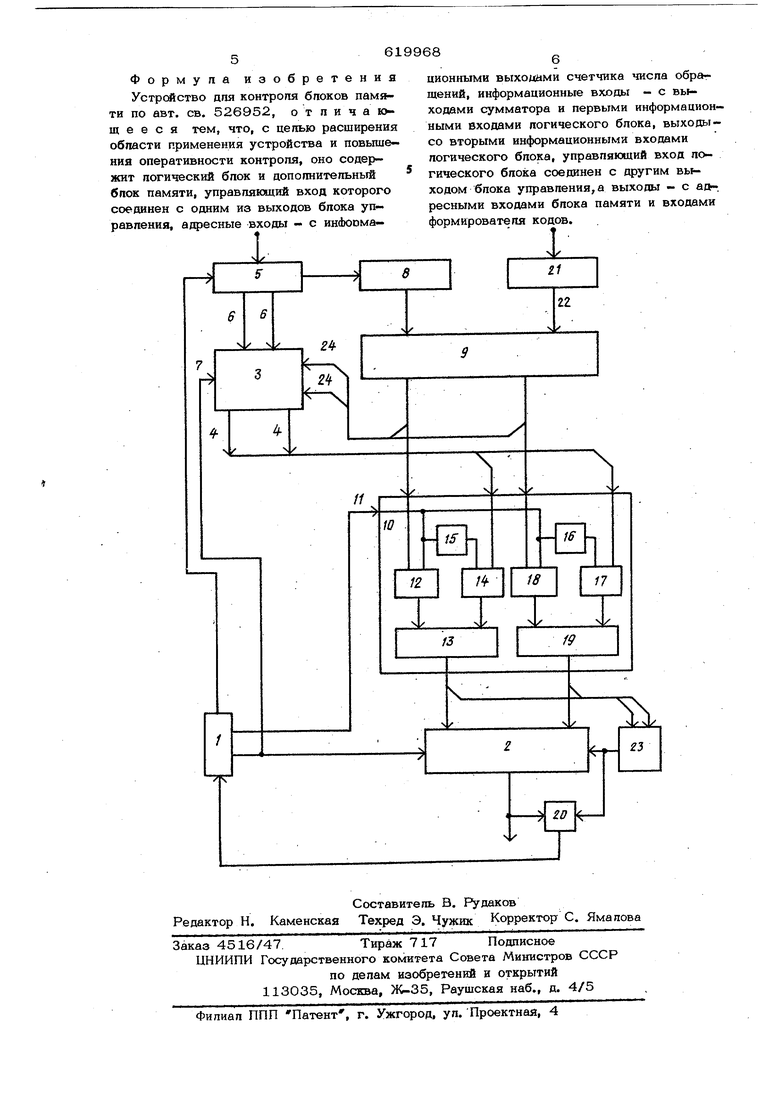

На чертеже изображена схема устройства.

Устройство содержит блок управления 1, блок памяти 2, дополнительный блок памяти 3, имеющий выходы 4, счетчик числа обращений 5, выходы которого соединены с агфесными входами 6 блока 3, управляющий вход 7 которого соединен с одним из выходов блока 1.

Устройство также содержит счетчик математических ожиданий 8, сумматор 9, логический блок 10, управляющий вход 11 которого соединен с другим выходом блока 1. БЛОК 1О срдёржит элемент И 12, элемент ИЛИ 13, элемент И 14, элементы НЕ 1б и 16, элементы И 17 и 18, элемент ИЛИ 19, Устройство так. же содержит блок сравнения 2О,, генератор случайных чисел 21, выход 22 кото рого соединен с одним из входов сумматора 9, и формирователь кодов 23. Выходы сумматора 9 соединены с иЯформа ционными входами 24 блока 3 и первы- ми информационными входами блока 10. Выходы 4 блока 3 подключены ко вторым информационным вЗсодам блока 1О Выходы блока 10 соединены с адресными входами блока памяти 2 и входами формирователя кодов 23.

Блок памяти 2 является проверяемым (контролируемым) блоком памяти.

Работа устройства происходит а двух сжимах.

В первом рехдаме блок 1 управления вьфабатьпзает управляющие сигнальг, приводящие блок памяти 3 в режим аапись а блок памяти 2 - в режим чтение. На управ яклдий вход 11 логического блока 10 подается потенциал, разрешакк щий прохождение информации с выхода сумматора 9 через элементы И 12 и 18 и элементы ИЛИ 13 и 19. Сигнал, прой- 50

дя элементы НБ 15 и 16 запрещает прохождение информации с блока памяти 3. Далее .работа устройства ь этом режиме аналогична работе устройства основного изобретения, т. е. адресная информация, подаваемая на ащэесные входы проверяемого блока памяти 2, формируется сложением кодов с генератора случайных чисел 21 и счетчика маТемаTij4ecKHX ожиданий 8. Информация, считанная с выбранной ячейки блока памяти 2, сравнивается с информацией, вырабатываемой формирователем кодов 23 в блоке сравнения 20. Результат сравнения подается на блок 1 управления. Но так как в предлагаемом устройстве ащэесная информация с выхода сумматор 9, кроме адресных входов проверяемого блока памяти 2, еще подается и на входы 24 блока памяти 3, то она записывается в блок памяти 3. Последователь ная запись информации в ячейки блока памяти 3 осуществляется заданием адресной информации на адресные входы б со счетчика 5 числа обращений и подачей сигнала на вход 7 блока 3 блоком 1, При обнаружении сбоя блФком сравнения 20 все адресные коды и последователь ность их задания на адресных входах проверяемого блока памяти 2 остаются записанными в блок памяти 3. Чтобы получить их для анализа, пользователь может проиндицировать эту информацию на пульте оператора или вывести ее на печатающее: устройство (на чертеже не показан4.1).

Во второй .режим устройство переводится после обнаружения сбоя. Блок 1

управления вырабатывает управляквдие сигналы, переводящие блок памяти 3 в режим чтение. На управляйнций вход 11 логического блока 1О подается потенциал, запрещающий прохождение инфор мации с выхода сумматора 9 на адресные входы проверяемого блока памяти 2 и разрещающий прохождение информации с выходов 4 блока памяти 3. Ащэер ные коды, записанные в блок памяти 3,

последовательно считьгеаются и подаются на адресные входы проверяемого блока памяти 2.

.Многократное считьгаание массива чисел блока памяти 3 позволяет много

кратно воспроизводить сбойную ситацию в проверяемом блоке памяти 2.

Та)шм образом, запись кодов адреса и последовательности их выборки в дополнительный блок памяти позволяет

за, а последующее и многократное считывание и подача на ащзесные входь проверяемого блока памяти 2 позволяет пользователю воспроизводить устойчивую 55 картину сбойных v ситуаций и помогает ..ему в оперативном отыскании причин . этих сбоев, что расширяет область применения устройства и повьпиает оперативность контроля. предоставить их пользователю для анали

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для контроля блоков памяти | 1974 |

|

SU526952A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1283859A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1003150A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

Авторы

Даты

1978-08-15—Публикация

1977-02-08—Подача