8 сравнения, связанный входами с шинами 9 считывания, формирователем 10 кодов и с шинами 11 записи.

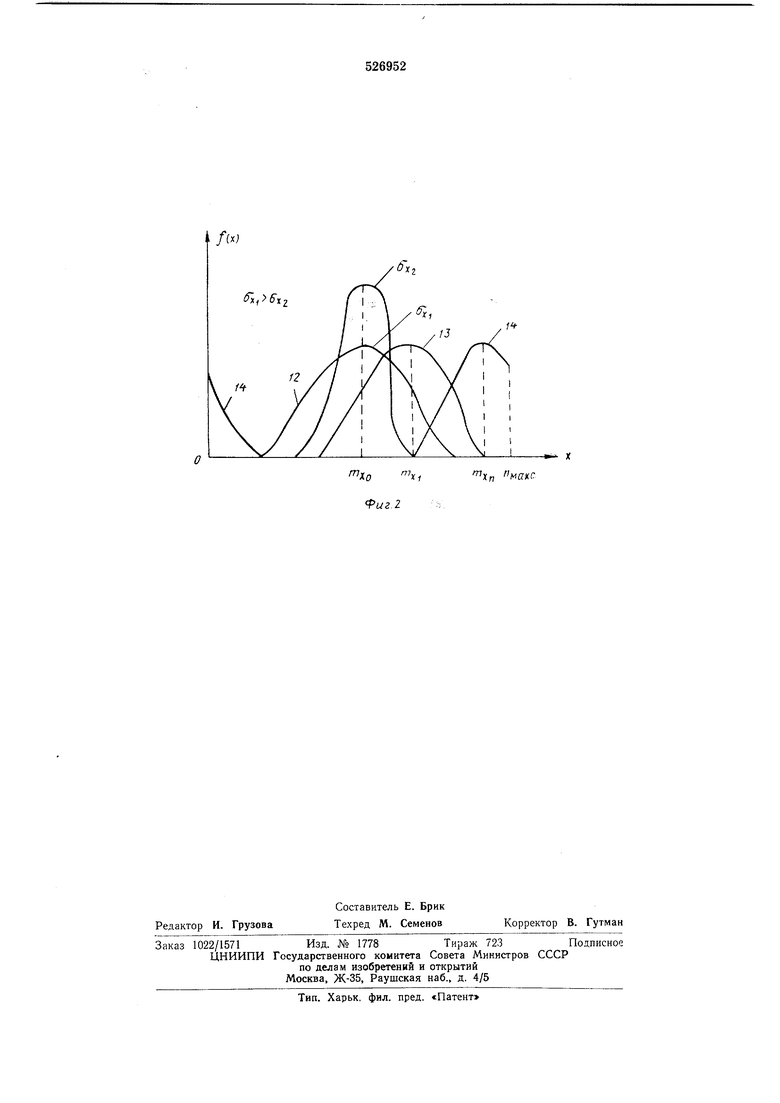

Ра-боту устройства рассмотрим на примере, когда генератор 7 случайных чисел вырабатывает числа с нормальным законом распределения.

Нормальный закон распределения имеет вид

1

/(А-)

а., 1/2.

r:ie J (х) - илоБНОсть вероятности случайной величины х;

tiix - математическое ожидание случайной величины А;

0;v - среднее квадратическое отклонение случайной величины х.

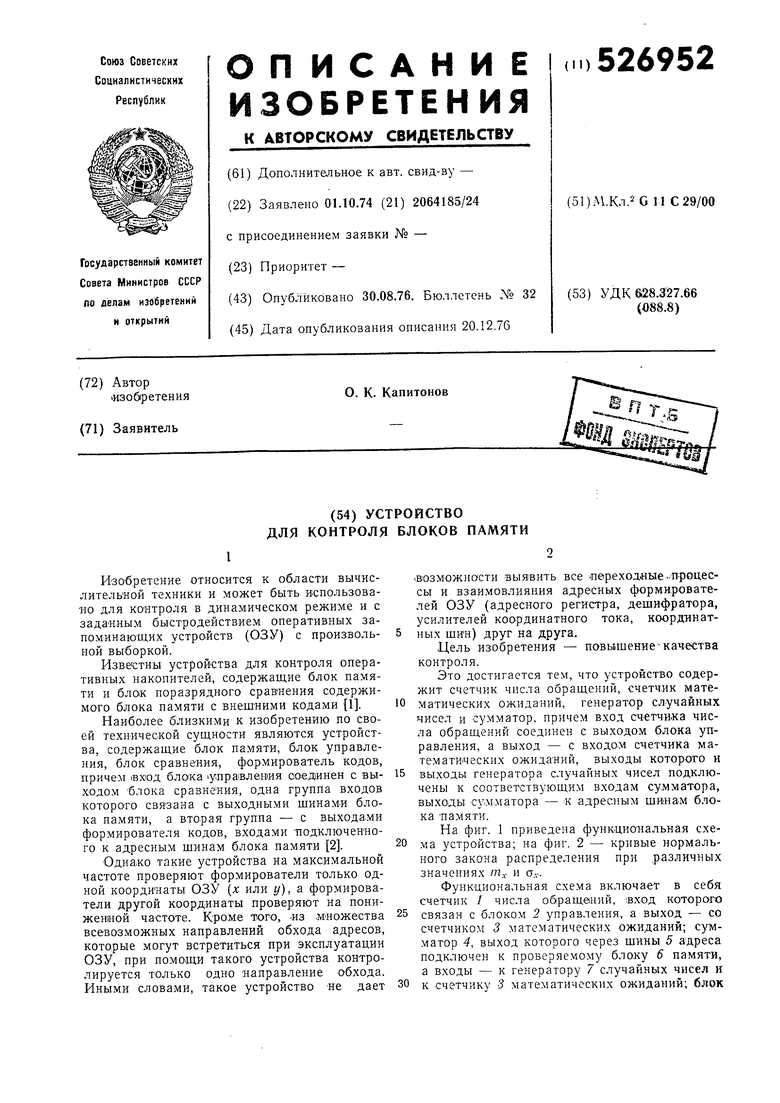

Перед тем как приступить к контролю ОЗУ, в него записывается тест, являюш,ийся производным адресной информации. Таким тестом может быть тест «адресный код или тест «шахматное поле. Для этого в счетчик 1 Числа обрашеиий вводится .максимальная Зставка (Все разряды счетчика устана:вливаются в состояние -«1), вход сумматора 4, соединенный с выходом тенератора 7 случайных чисел, блокируется (цепь блокировки на схеме не показана). Задается режим записи, и проводится пуск. Импульсы из блока 2 управления, пройдя счетчи-к 1 числа обраш,ений, подаются в счетчик 3 математических ожиданий. Адресная Ннформация, сформированная счетчиком 3 математических ожиданий, параллельным кодом, .пройдя без изменения сумматор 4, поступает на адресные шины 5 блока 6 памяти и формирователь 10 кодов для формирования записываемого теста. Сигналы обраш.ения, идушие с блока 2 управления на проверяемый блок памяти, проводят запись формируемого теста по всем адресам.

После записи теста переходят на режим проверки адресных формирователей ОЗУ. Проверяемый блок памяти переводят в реЖ1И;М чтения. Счетчик 3 (Математических ожиданий «обнуляется, в счетчик 1 числа обращений вводится уставка в зависимости от требуемого числа обрашений при выбранном параметре сгд., вход сумматора 4, идуш,ий на генератор 7 случайных чисел, освобождается от блокировки и проводят спуск.

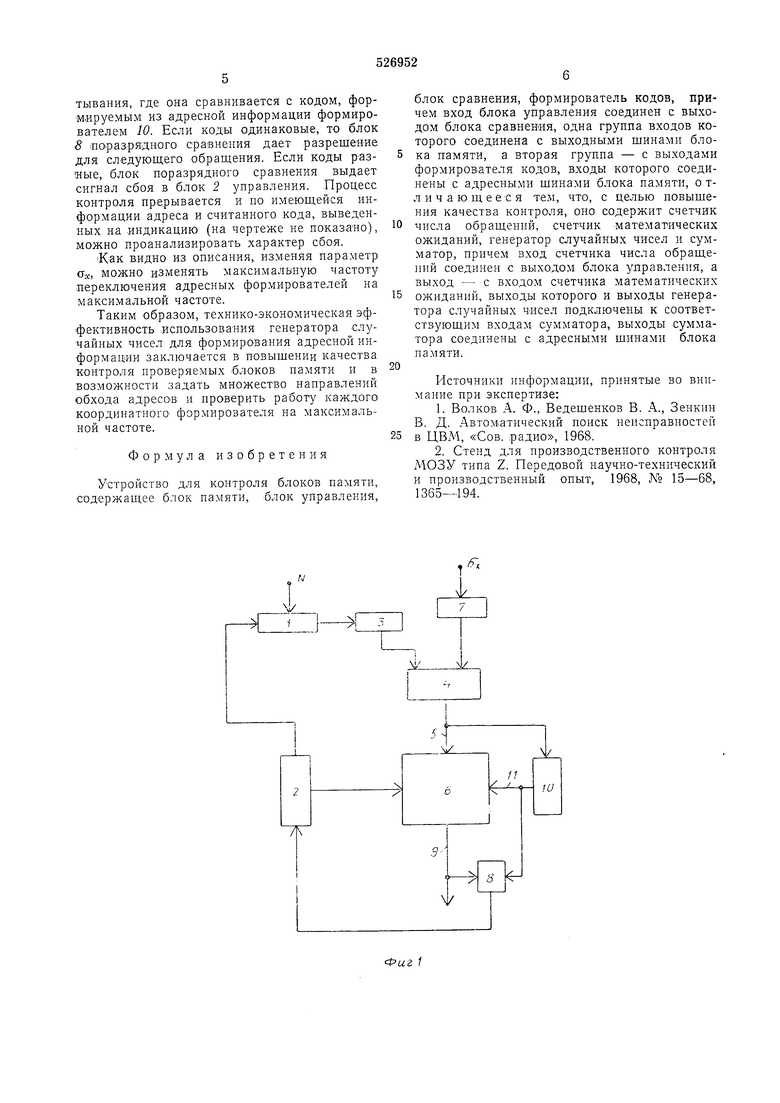

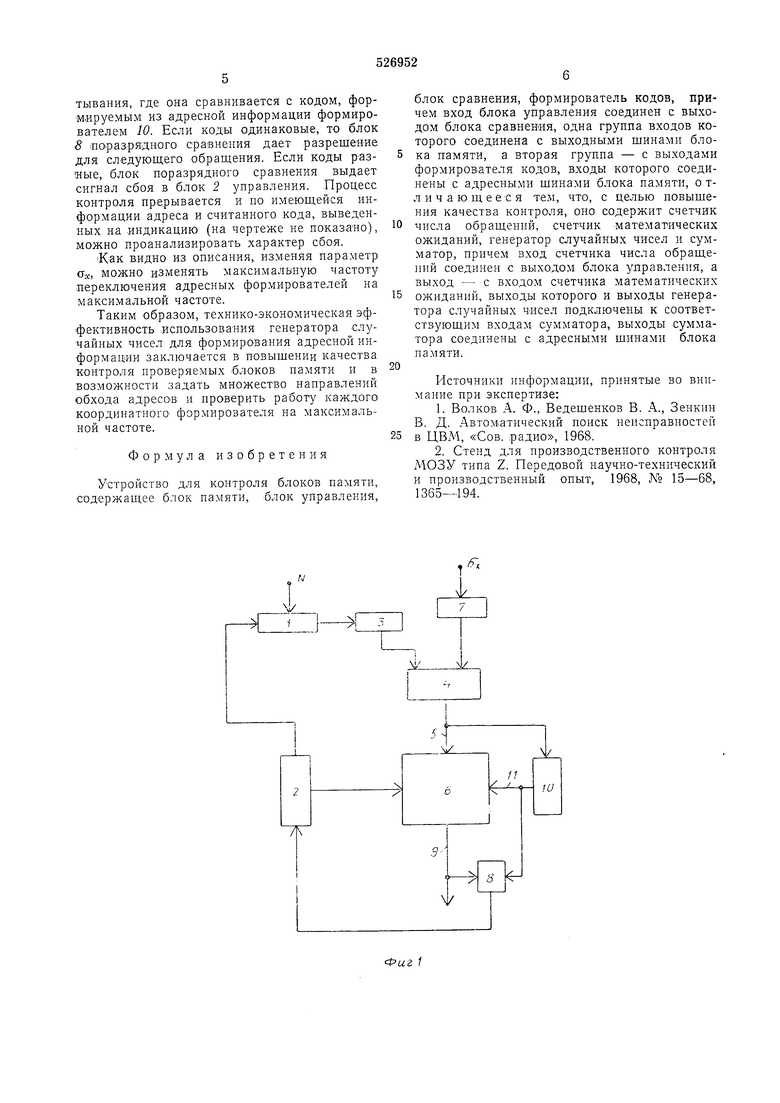

Блок 2 управления обеспечивает обраш,е.ние к ячейкам блока памяти, код адреса которых фор.мируется сумматором 4, и представляет собой код, равный сумме кодов, вырабатываемых генератором 7 случайных чисел и счетчиком 3 математических ожиданий. В начальный момент счетчик м атематических ожиданий «о.бнулен, поэтому адресная информация представляет собой коды чисел, вырабатываемые генератором 7 случайных чисел. Генератор случайных чисел вырабатывает коды

чисел с матем атическим ожиданием /и, и выбранным параметром ах, (см. фиг. 2, кривая 12).

Плотность вероятности обращений к ячейкам ОЗУ соответствует кривой 12 до тех пор, пока содержимое счетчика 3 математических ожиданий не изменится. Количество обращений к ячейкам ОЗУ, адреса которых ограничены кривой J2, определяется уставкой N в

счетчике / числа обращений. Максимальное число обращений происходит к ячейке, код адреса .которой совпадает с т,После того, как произойдет С - N обращений к ячейкам (С - емкость счетчика У),

счетчик / числа обращений переполняется и сигнал переполнения поступает на счетчик 3 математических ожиданий. Адресная информация при этом равна кодам, вырабатываемы.м генератором 7 случайных чисел, плюс

единица. В этом случае происходит обращение к ячейкам ОЗУ с математическим ожиданием /Пд. и с плотностью вероятности, соответствующей кривой 13 (см. фиг. 2). Максимальное число обращений проводится к ячейке, код адреса которой совпадает с т,. После того, как произойдет ещ.е С - N обращений, счетчик / числа обращений онять переполняется, сигнал переполнения увеличивает код счетчика 3 математических ожиданий еще

на единицу и обращение к ячейкам ОЗУ происходит с математическим ожиданием, увеличенным на единицу и т. д.

Когда коды адреса соответствуют старщим номерам ячеек (см. фиг. 2, кривая 14),

появляется момент, во время которого код суммы двух чисел - кода счетчика 3 математических ожиданий и кода генератора 7 случайных чисел-превосходит код адреса ячейки с максимальным номером. Сумматор 4 переполняется, па его старшем разряде Е031пикает сигнал переноса, а содержимое сумматора 4 представляет остаток от переполн.епия. В этом случае происходит обращение к ячейкам с младшими номерами.

Процесс формирования адресной информации заканчивается, когда полностью заполнится счетчик 5 математических ожиданий (емкость счетчика 3 математических ожиданий соответствует емкости проверяемого блока памяти).

Таким образом, каждая ячейка ОЗУ испытывается в режиме максимального числа обр-ащений. Когда т совпадает с кодами адреса младших ячеек ОЗУ, на максимальной

частоте проверяются формирователи одной адресной координаты (х или у); когда .п. перемещается в область кодов адреса старщих номеров ячеек, на максимальной частоте Проверяются формирователи другой адресной

координаты.

Правильность работы адресных формирователей определяется по совпадению записываемой в ОЗУ и считанной из ОЗУ информации. Считанная информация подается на блок 8 поразрядного сравнения через щины 9 считывания, где она сравнивается с кодом, формируемым из адресной информации формировател.ем 10. Если коды одинаковые, то блок 8 -поразрядного сравнения дает разрешение для следующего обращения. Если коды разиые, блок поразрядного сравнения выдает сигнал сбоя в блок 2 управления. Процесс контроля прерывается и по имеющейся информации адреса и считанного кода, выведенных на индикацию (на чертеже не показано), можно проанализировать характер сбоя.

Как видно из описания, изменяя параметр GX, можно изменять максимальную частоту переключения адресных формирователей на максимальной частоте.

Таким образом, технико-экономическая эффективность использования генератора случайных чисел для формирования адресной информации заключается в повыщенни качества контроля проверяемых блоков памяти и в возможности задать множество направлений обхода адресов и проверить работу каждого координатного формирователя на максимальной частоте.

Формула изобретения

Устройство для контроля блоков памяти, содержащее блок памяти, блок управления.

блок сравнения, формирователь кодов, причем вход блока управления соединен с выходом блока сравнения, одна группа входов которого соединена с выходными шинами блока памяти, а вторая группа - с выходами формирователя кодов, входы которого соединены с адресными шинами блока памяти, о тличающееся тем, что, с целью повышения качества контроля, оно содержит счетчик

0 числа обращений, счетчик математических ожиданий, генератор случайных чисел и сумматор, причем вход счетчика числа обращений соединен с выходом блока управления, а выход - с входом счетчика математических

5 ожиданий, выходы которого и выходы генератора случайных чисел подключены к соответствующим входам сумматора, выходы сумматора соединены с адресными шинами блока памяти.

Источники информации, принятые во внимание при экспертизе:

1.Волков А. Ф., Ведешенков В. А., Зенкин В. Д. Автом.атический поиск неисправностей

в ЦВМ, «Сов. радио, 1968.

2.Стенд для производственного контроля МОЗУ типа Z. Передовой научно-технический и производственный опыт, 1968, N° 15-68, 1365- 194.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1977 |

|

SU619968A2 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1003150A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU940240A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1283859A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для обнаружения ошибок в блоках интегральной оперативной памяти | 1988 |

|

SU1605281A1 |

| Устройство для контроля интегральных блоков оперативной памяти | 1980 |

|

SU907586A1 |

д.

махе

41

Авторы

Даты

1976-08-30—Публикация

1974-10-01—Подача