Изобретение отнесется к радиотехнике, приборостроению и автоматике и может быть использовано в диекретных системах обработки иифор.мации.

Изве.стен цифровой синтезатор частот, содержащий последовате.1ьио соединенные датчик опорных частот м фазовый детектор, а также Г1оследовате.льно соединенные фильтр нижних частот, управляющий э.чемент, перестраиваемый генератор, делите,1ь частоты с постоянным коэффициентом и делитель частоты с переменным коэффициентом деления, выход которого иодключен к дpyгo iy входу фазового детектора 1.

Однако в спектре выходного колебания синтезатора частот приеутетвуют соетавляюнлие, крагные опорной частоте.

Цель изобретения - улучшение подавления в спектре выходного колебания составляющих, кратных опорной частоте.

Цель достигается тем, что в цифровой еинтезатор частот, содержаиий последовательно соединенные опорных частот и фазовый детектор, а также иоследовательно .соединенные фи.:1ьтр нижних частот, унрав.чяющий элемент, нерестраиваемый генератор, дел 11тел ь частоты с ностоянным коэ(|)фициентом деления н делитель частоты с переменным коэффициентом де,теиия ,выход которого иодключен к друго.мх вход ())азового детектора, в.зедены нос,ледовате.1ьно соедииеи 1е блок задержки, элемент И и инфроЛ5ОЙ интегратор, выход ) соедииен со входом нижних частот, тактовые вхо ды блока задержки и цифрового интегратора подключены к другому выходу датчика опорных частот, первый выход фазового детектора соединен с другими входами блока задержки и элемента И, а второй выход с|эазового детектора соединен с управляющн.1 входо.м цифрового iiHferpaTopa.

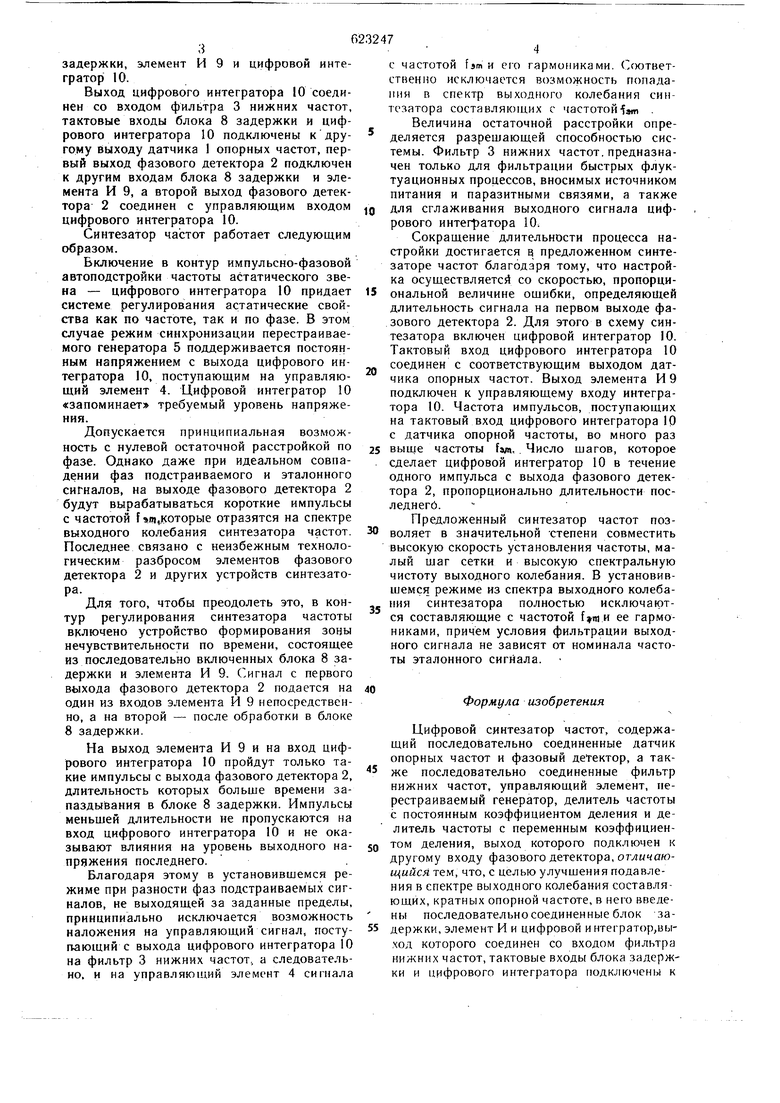

На чертеже приведена структурная электрическая схема предложенного синтезатора.

Цифровой синтезатор частот содержит последовательно соединенные датчик 1 опорных чаетот и фазовый детектор 2, а также последовательно соединенные фильтр 3 нижних частот, управляющий элемент 4, перестраиваемый генератор 5, делитель 6 частоты с постоянным коэффициентом деления и делитель 7 чаетоты с переменным коэффициентом деления, выход которого подключен к другому входу фазового детектора 2, блок 8 задержки, элемент И 9 и цифровой интегратор 10. Выход цифрового интегратора 10 соединен со входом фильтра 3 нижних частот, тактовые входы блока 8 задержки и цифрового интегратора 10 подключены к другому выходу датчика 1 опорных частот, первый выход фазового детектора 2 подключен к другим входам блока 8 задержки и элемента И 9, а второй выход фазового детектора 2 соединен с управляющим входом цифрового интегратора 10. Синтезатор частот работает следующим образом. Включение в контур импульсно-фазовой автоподстройки частоты астатического звена - цифрового интегратора 10 придает системе регулирования астатические свойства как по частоте, так и по фазе. В этом случае режим синхронизации перестраиваемого генератора 5 поддерживается постоянным напряжением с выхода цифрового интегратора 10, поступающим на управляющий элемент 4. Цифровой интегратор 10 «запоминает требуемый уровень напряжения. Допускается принципиальная возможность с нулевой остаточной расстройкой по фазе. Однако даже при идеальном совпадении фаз подстраиваемого и эталонного сигналов, на выходе фазового детектора 2 будут вырабатываться короткие импульсы с частотой ,KOTopbie отразятся на спектре выходного колебания синтезатора частот. Последнее связано с неизбежным технологическим разбросом элементов фазового детектора 2 и других устройств синтезатора. Для того, чтобы преодолеть это, в контур регулирования синтезатора частоты включено устройство формирования зоны нечувствительности по времени, состоящее из последовательно включенных блока 8 задержки и элемента И 9. Сигнал с первого выхода фазового детектора 2 подается на один из входов элемента И 9 непосредственно, а на второй - после обработки в блоке 8 задержки. На выход элемента И 9 и на вход цифрового интегратора 10 пройдут только такие импульсы с выхода фазового детектора 2, длительность которых больше времени запаздывания в блоке 8 задержки. Импульсы меньщей длительности не пропускаются на вход цифрового интегратора 10 и не оказывают влияния на уровень выходного напряжения последнего. Благодаря этому в установившемся режиме при разности фаз подстраиваемых сигналов, не выходящей за заданные пределы, принципиально исключается возможность наложения на управляющий сигнал, поступающий с выхода цифрового интегратора 10 на фильтр 3 нижних частот,, а следовательно, и на управляющий элемент 4 сигнала с частотой fim и его гармониками, (лютветственно исключается возможность попадания в спектр выходного колебания синтезатора составляюпхих с частотойiam . Величина остаточной расстройки определяется разрешающей способностью системы. Фильтр 3 нижних частот, предназначен только для фильтрации быстрых флуктуационных процессов, вносимых источником питания и паразитными связями, а также для сглаживания выходного сигнала цифрового интегратора 10. Сокращение длительности процесса настройки достигается в предложенном синтезаторе частот благодаря тому, что настройка осуществляетсй со скоростью, пропорциональной величине ощибки, определяющей длительность сигнала на первом выходе фазового детектора 2. Для этого в схему синтезатора включен цифровой интегратор 10. Тактовый вход цифрового интегратора 10 соединен с соответствующим выходом датчика опорных частот. Выход элемента И 9 подключен к управляющему входу интегратора 10. Частота импульсов, поступающих на тактовый вход цифрового интегратора 10 с датчика опорной частоты, во много раз выше частоты fsm, . Число шагов, которое сделает цифровой интегратор 10 в течение одного импульса с выхода фазового детектора 2, пропорционально длительности последнего. Предложенный синтезатор частот позволяет в значительной степени совместить высокую скорость установления частоты, малый шаг сетки и высокую спектральную чистоту выходного колебания. Б установившемся режиме из спектра выходного колебания синтезатора полностью исключаются составляющие с частотой и ее гармониками, причем условия фильтрации выходного сигнала не зависят от номинала частоты эталонного сигнала. Формула изобретения Цифровой синтезатор частот, содержащий последовательно соединенные датчик опорных частот и фазовый детектор, а также последовательно соединенные фильтр нижних частот, управляющий элемент, перестраиваемый генератор, делитель частоты с постоянным коэффициентом деления и делитель частоты с переменным коэффициентом деления, выход которого подключен к другому входу фазового детектора, отугмча/ощийся тем, что, с целью улучшения подавления в спектре выходного колебания составляющих, кратных опорной частоте, в него введены последовательно соединенные блок задержки, элемент И и цифровой и нтегратор,вЕ |ход которого соединен со входом фильтра нижних частот, тактовые входы блока задержки и цифрового интегратора подключены к

другому ныхолу датчика опорных частот, первый выход фазового детектора соединен с другими входами блока задержки и элемента И. а второй выход фазового детектора соединен с управляющим входом цифрового интегратора.

Источники информации, принятые во внимание при экспертизе:

I. Левин В. А., Нисневич Д. Г. Некоторые вопросы построения цифровых синтезаторов частот. «Электросвязь, № 4, 1976,с. 73-79.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Синтезатор частот | 1989 |

|

SU1730720A1 |

| Синтезатор частоты | 1981 |

|

SU1007202A1 |

| Устройство для поиска шумоподобного сигнала | 1984 |

|

SU1277415A1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Синтезатор частот | 1980 |

|

SU896762A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

Авторы

Даты

1978-09-05—Публикация

1976-08-11—Подача