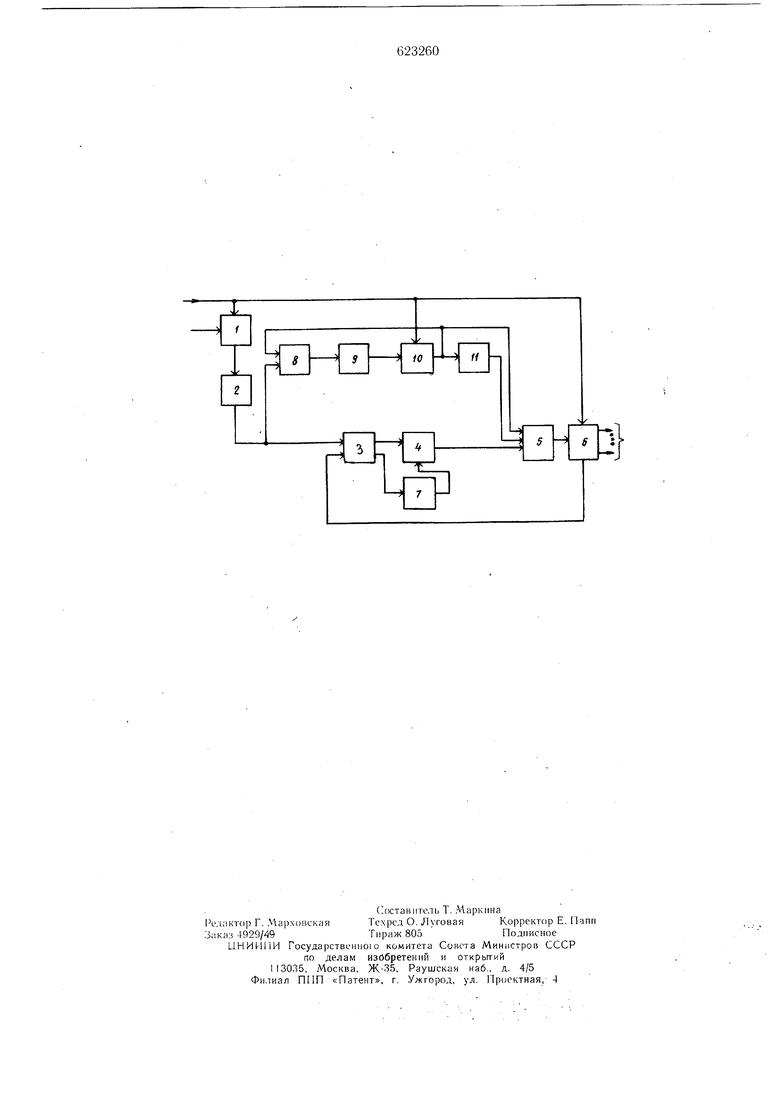

Изобретение . относится к электросвязи и может испоотьзоваться в цифровых систомах передачи. Известно устройство цикловой синхронизации, содержащее последовательно соединенные регистр сдвига, дешифратор, первый анализатор, первый накопитель, блок совпадения и генератор, выход которого подключен к другому входу первого анализатора, другой выход которого через второй накопитель подключен к другому входу первого накопителя, а также последовате п,но соединенные второй анализатор, блок управления и делитель, выход которого подключен ко второму входу блока совпадения и первому входу второго анализатора, а другой вход делителя oбъeди ieн со входом регистра сдвига и другим входом генератора и является входом устройства, причем выход дешифратора подключен к второму входу второго анализатора |1J. Однако такое устройство не обеспечивает достаточной помехоустойчивости. Цель изобретения - повышение помехоустойчивости и сокращение времени вхождения в синхронизм. Для этого в устройство цикловой синхронизации, содержащее последовательно соединенные регистр сдвига, дещифратор, первый анализатор, первый накопитель, блок совпадения и генератор, выход которого подключен к другому входу первого анализатора, другой выход которого через второй накопитель подключен к другому входу первого накопителя, а также последовательно соединенные второй анализатор, блок управления и делитель, выход которого подключен ко второму входу блока coв пaдeния и первому входу второго анализатора, а другой вход делителя объединен со входом регистра сдвига и другим входом генератора и является входом устройства, причем выход дещифратора подключен к второму входу второго анализатора, введен дополнительный накопитель, вход которого соединен с выходом делителя, а выход - с третьим входом блока совпадения. На чертеже изображена структурная электрическая схема предложенного устройства. Устройство цикловой синхронизации содержит последовательно соединенные регистр 1 сдвига, дешифратор 2, первый анализатор 3, первый накопитель 4, блок 5 совпадения и генератор б, выход которого подключен к другому входу первого апа.шзатора 3, другой вьгход которого через кгорой накопитель 7 подк.ночей к другому входу первого накопителя 4. и также поеле;ювательно ес)еди11е 1пые BTOpofi анализатор 8, блок 9 управ,1е11ия и делитель 10, выход которого иодк.тючен ко втором входу олока 5 еовпадекия и первому входу второго анализатора 8. а дру1Ч)й вход делителя 10 соединен со входом регистра 1 сдвига и другим входом генератора 6 и являетея входом устройства, причем выход деип1фратора 2 подключен к второму входу второго ана.1изатора 8, а также дополнительный накоиитель 11, вход которого соединен с выходом делителя 10, а выход - с третьим входом блока 5 совпадения. Устройство работает следующ-пм образом. В состоянии синхронизма сигналы на вы(хте денп1фратора 2 и генератора 9 совпадают по времегн). При этом на выходе первого анализатора 3 нериод1 чески появляются сигналы, заполняющие второй накопитель 7, а пе)вый наконите ть 4 опуетошеп. На выходе б;1ока 5 совпадения си1нал отсутствует, и генератор 6 работает синхронпо с при1П маемым rpyiniOBijiM сигна.юм. Де.П1тель 10 работает CHHxpoHiio с IenepaToром 6, снгна.ты на выходе второго ана.тпзатора 8 и на выходе блока 9 управления отсутствуют. При наруп енпи синхрониз.ма сигна.ты на входах анализаторов 3 н 8 не синфазны м на выходах этих ана.тизаторов появляются сигналы несовпадения. Сигналы несовпадения с выхода первого анализатора 3 поступают на вход первого накопителя 4 и нанол ;яют его. После наполнения первого накогипеля 4 на его выходе появляется сигнал, подготавливаюн1ий блок 5 совпаде1Н1я 1 установке генератора 6. Первый сигнал несовпадения на выходе вкмюго анализатора 8 подготав,тивает б.юк 9 унрав.ления к установке делителя 10. При иоявленни на выходе деп1ифратора 2 сигнала иа выходах первого анализатора 8 и блока 9 унрав,тения появляются сигпал 1, устанавливающие делитель 10. Далее устройство переходит в режим коитро,тя, в котором оно находится до тех пор, пока па анализируемой позицнп пе сфор.мпруется комбинация сп; ;волов, отличная от синхрогрунны. После этого след юпи1и сигна.т на выходе деп1ифратора 2 установит дсл1ггель 10 п устройство перейдет в режим контроля синхронизма па другой нозинии прппимаемого группового сигнала. Т;1ким образом осун1ествляется процесс поис1 а синхросигна.та незавнсимо от состояния первого након ггеля 4. Перестройка генератора 6 пронзводи ся только носле обнаружения устойчивого отсу1сг ия состояния синхронизма на предыдун1ей .тактовой позиции (носле заполнения первого накопителя 4 по выходу из ципх)опизма) и устойчивого обнаружения с.11хрогруцпы на другой позиции, (после заполнения доно.тпительного накопителя 11 по входу в синхронизм), в предлагаемом устройстве синхронизации исключается ложная перестройка генератора 6, и, как следствие, время несинхроннойработыаппаратурысокращается. Коэффициент деления донол1Н1тельного накопителя 11 выбирается исходя из статических характеристик грунпового сигнала н структуры синхрогруппы. При использовании предложенного устройства значительно повышается но.мехоустойчнвость и сокращается время вхождения в синхронизм. Формула изобретения Устройство цик„ювой синхронизации, содержанхее последовательно соединенные регистр сд,вига, дешифратор, первый анализатор, первый накопитель, блок совпадения и генератор, выход которого подключен к друroAiy входу первого анализатора, другой выход которого че()ез второй накопитель подключен к другому входу первого накопителя, а также последовательно соединенные второй анализа1ор, блок уцравления и делите;1ь, выход которого подключен ко второ.му входу блока совпаде}П1я и первому входу второго анализатора, а другой вход делите,тя объединен со входом регистра сдвига п другим входом генератора и являетея входом устройства, причем выход дешифратора подключен к второ.му входу второго анализатора, отличающееся тем, что, с целью повышения помехоустойчивости и сокращения времени вхождения в синхронизм, введен дополнительный накопитель, вход которого соединен с выходом делителя, а выход - с третьим входом блока совпадения. Источники информации, принятые во внимание при экспертизе: 1. Левин Л. С. и Г лоткин . .4.,Основы построения цифровых систе. передачи. М, «Связь, 1975 , с. 116-120.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Устройство цикловой синхронизации | 1977 |

|

SU668100A2 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU907838A2 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для цикловой синхронизации корректирующих кодов | 1978 |

|

SU788413A2 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1999 |

|

RU2173027C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

| Устройство синхронизации по циклам | 1980 |

|

SU944135A1 |

Авторы

Даты

1978-09-05—Публикация

1977-02-08—Подача