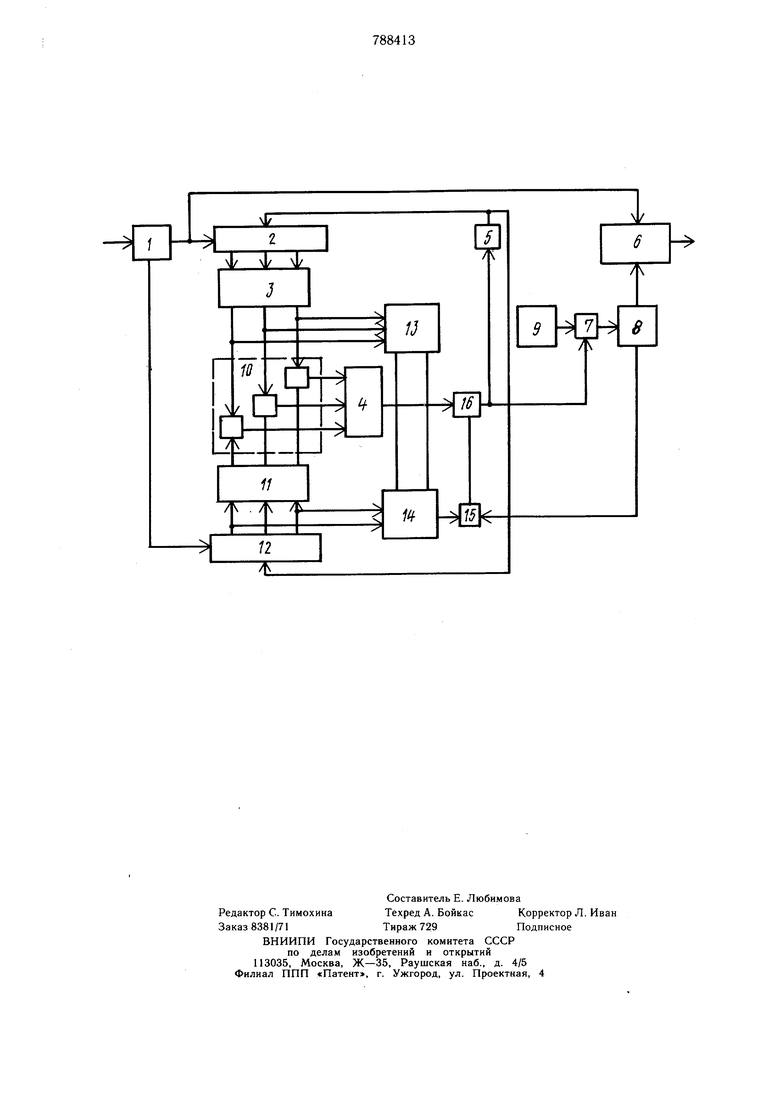

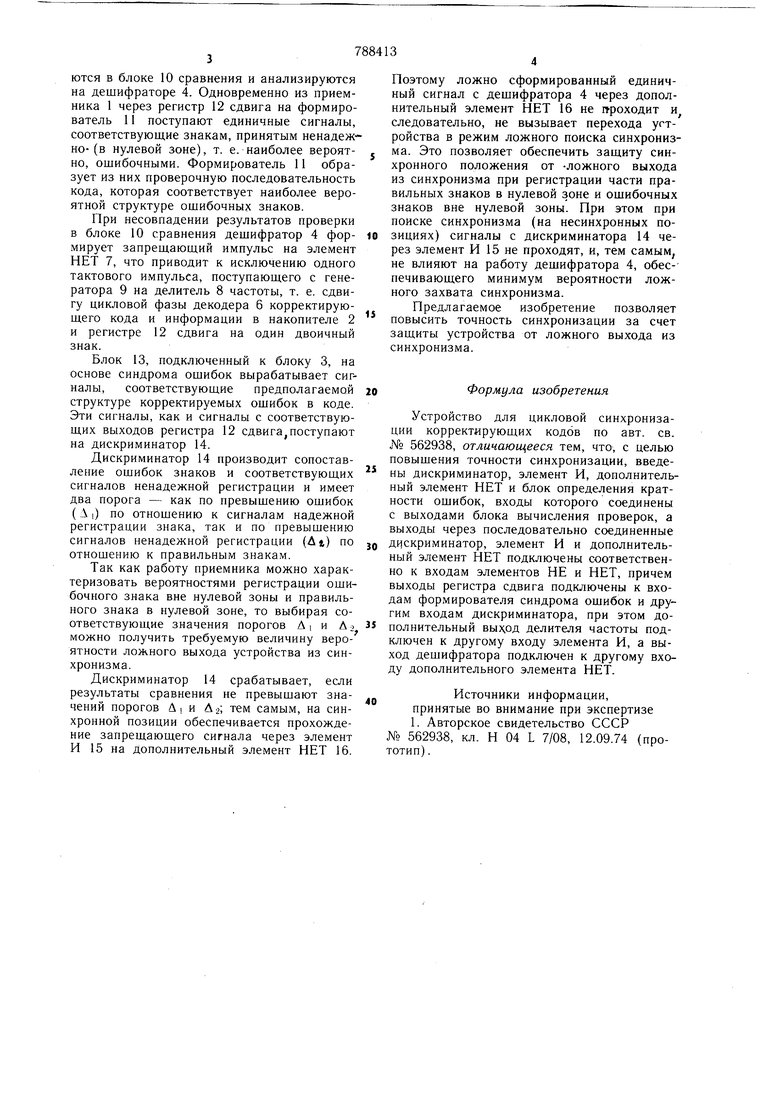

Изобретение относится к электросвязи и может иснользоваться в устройствах цикловой синхронизации систем передачи двоичной информации, закодированной блочными корректирующими кодами. По основному авт. св. № 562938 известно ycтpoйctвo для цикловой синхронизации корректирующих кодов, содержащее приемник, накопитель, блок вычисления проверок, дешифратор, элемент НЕ, декодер, элемент НЕТ, делитель частоты, генератор тактовых импульсов, блок сравнения, формирователь синдрома ошибок и регистр сдвига 1. Однако точность синхронизации известного устройства невысока. Цель изобретения - повышение точности синхронизации. Для достижения этой цели в известное устройство для цикловой синхронизации корректирующих кодов введены дискриминатор, элемент И, дополнительный элемент НЕТ и блок определения кратности ощибок, входы которого соединены с выходами блока вычисления проверок, а выходы через последовательно соединенные дискриминатор, элемент И и дополнительный элемент НЕТ подключены соответственно к входам элементов НЕ и НЕТ, причем выходы регистра сдвига подключены к входам формирователя синдрома ошибок и другим входам дискриминатора, при этом дополнительный выход делителя частоты подключен к другому входу элемента И, а выход дешифратора подключен к другому входу дополнительного элемента НЕТ. На чертеже представлена структурная электрическая схема предложенного устройства. Устройство для цикловой синхронизации корректирующих кодов содержит приемник 1, накопитель 2, блок 3 вычисления проверок, дешифратор 4, элемент НЕ 5, декодер 6, элемент НЕТ 7, делитель 8 частоты, генератор 9 тактовых импульсов, блок 10 сравнения, формирователь 11 синдрома ошибок, регистр 12 сдвига, блок 13 определения кратности ошибок, дискриминатор 14, элемент И 15 и дополнительный элемент НЕТ 16. Устройство работает следующим образом. Кодовая последовательность знаков из приемника 1 задерживается в накопителе 2 и проверяется на закон построения кода в блоке 3. Результаты проверок сопоставляются в блоке 10 сравнения и анализируются на дешифраторе 4. Одновременно из приемника 1 через регистр 12 сдвига на формирователь 11 поступают единичные сигналы, соответствующие знакам, принятым ненадежно-(в нулевой зоне), т. е. наиболее вероятно, ошибочными. Формирователь 11 образует из них проверочную последовательность кода, которая соответствует наиболее вероятной структуре ошибочных знаков. При несовпадении результатов проверки в блоке 10 сравнения дешифратор 4 формирует запрещающий импульс на элемент НЕТ 7, что приводит к исключению одного тактового импульса, поступающего с генератора 9 на делитель 8 частоты, т. е. сдвигу цикловой фазы декодера 6 корректирующего кода и информации в накопителе 2 и регистре 12 сдвига на один двоичный знак. Блок 13, подключенный к блоку 3, на основе синдрома ошибок вырабатывает сигналы, соответствующие предполагаемой структуре корректируемых ошибок в коде. Эти сигналы, как и сигналы с соответствующих выходов регистра 12 сдвига,поступают на дискриминатор 14. Дискриминатор 14 производит сопоставление ошибок знаков и соответствующих сигналов ненадежной регистрации и имеет два порога - как по превышению ошибок (А |) по отношению к сигналам надежной регистрации знака, так и по превышению сигналов ненадежной регистрации (At) по отношению к правильным знакам. Так как работу приемника можно характеризовать вероятностями регистрации ошибочного знака вне нулевой зоны и правильного знака в нулевой зоне, то выбирая соответствующие значения порогов А; и До можно получить требуемую величину вероятности ложного выхода устройства из синхронизма. Дискриминатор 14 срабатывает, если результаты сравнения не превышают значений порогов Д| и Д2; тем самым, на синхронной позиции обеспечивается прохождение запрещающего сигнала через элемент И 15 на Дополнительный элемент НЕТ 16. Поэтому ложно сформированный единичный сигнал с дешифратора 4 через дополнительный элемент НЕТ 16 не проходит и следовательно, не вызывает перехода устройства в режим ложного поиска синхронизма. Это позволяет обеспечить защиту синхронного положения от -ложного выхода из синхронизма при регистрации части правильных знаков в нулевой зоне и ошибочных знаков вне нулевой зоны. При этом при поиске синхронизма (на несинхронных оозициях) сигналы с дискриминатора 14 через элемент И 15 не проходят, и, тем самым, не влияют на работу дешифратора 4, обеспечивающего минимум вероятности ложного захвата синхронизма. Предлагаемое изобретение позволяет повысить точность синхронизации за счет защиты устройства от ложного выхода из синхронизма. Формула изобретения Устройство для цикловой синхронизации корректирующих кодов по авт. св. № 562938, отличающееся тем, что, с целью повышения точности синхронизации, введены дискриминатор, элемент И, дополнительный элемент НЕТ и блок определения кратности ошибок, входы которого соединены с выходами блока вычисления проверок, а выходы через последовательно соединенные дискриминатор, элемент И и дополнительный элемент НЕТ подключены соответственно к входам элементов НЕ и НЕТ, причем ВЫХОДЫ регистра сдвига подключены к входам формирователя синдрома ошибок и другим входам дискриминатора, при этом дополнительный выход делителя частоты подключен к другому входу элемента И, а выход дешифратора подключен к другому входу дополнительного элемента НЕТ. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР М 562938, кл. Н 04 L 7/08, 12.09.74 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство блочной синхронизации для групповых кодов | 1980 |

|

SU932643A1 |

| Устройство цикловой синхронизации для блочных кодов | 1975 |

|

SU565403A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

Авторы

Даты

1980-12-15—Публикация

1978-12-07—Подача