Изобретенне относится к вычислительной технике и может быть использовано для многоканального счета с временным делением каналов н хранением накопленных результатов, а при необходимости и в качестве обычного запоминающего устройства.

По основному авт. св. № 568971 нзвестно магнитное запоминающее устройство, содер.жащее матрицу памяти, выполненную на трехотверстных сердечниках флюксорного типа из материала с прямоугольной петлей гистерезиса, прошитых шинами записи, считывания, режима и шинами управления выхода формирователи соответствующих токов, устройство считывания и местное устройство управления 1.

Однако известное устройство имеет ограниченные функциональные возможности.

Цель изобретения - расширенне области применения устройства за счет реализации суммирования вычитания единичных прирашений к содержимому любой ячейки памяти непосредственно в запоминающем устройстве.

Для этого в предлагаемое устройство введены разрядный коммутатор, блок вентилей и триггер запоминания переноса, выходы разрядного коммутатора соединены с входами разрядных формирователей токов режима, входы вентилей соединены с регнстром числа, а выходы - с разрядными формирователями токов записи, входы установки «I и «О триггера запомииаиия переноса соединены соответственно с выходами элементов ИЛИ и И, а выходы - с блоком управления запоминающего устройства.

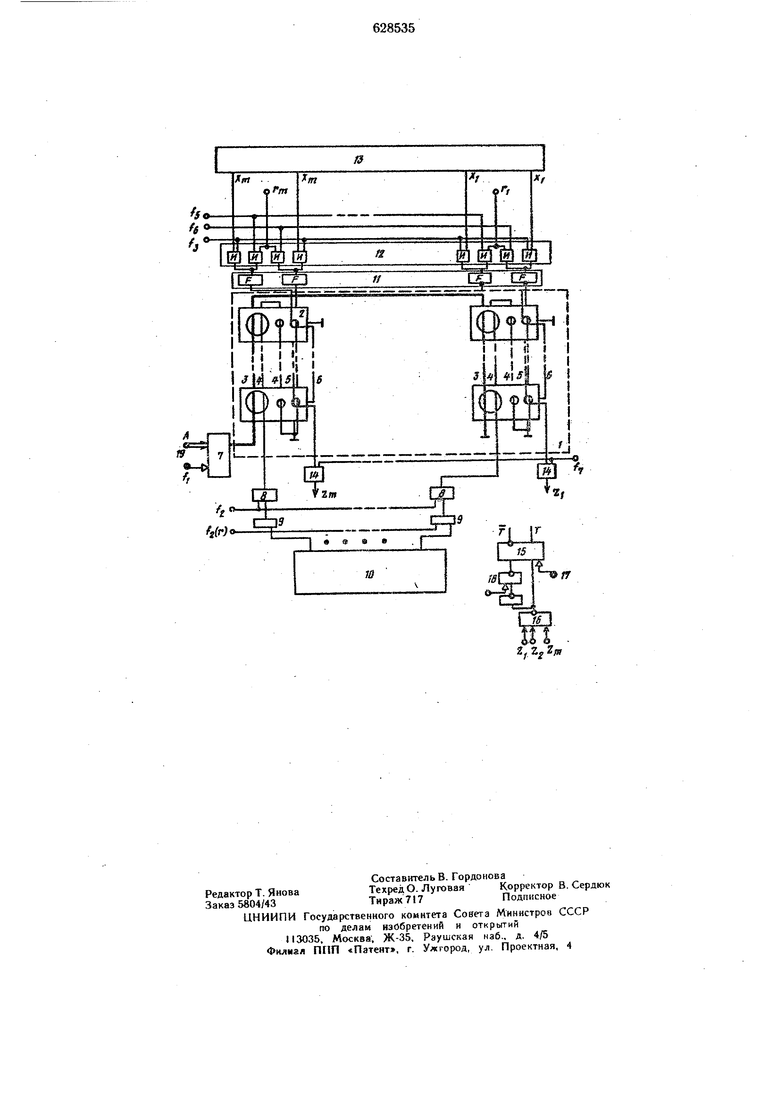

На чертеже изображена схема предлагаемого магнитного запоминающего устройства.

Магнитное запоминающее устройство содержит накопитель 1, состоящий из трехотверстиых сердечников 2 флюксорного типа из материала с прямоугольной петлей гистерезиса, причем одно крайнее отверстие больше двух других. Накопитель прошит обмотками 3 выборки, проходящими чере больщие отверстия сердечников, разрядными обмотками 4 режима, проходящими через большие отверстия сердечников в одном направлении, а через центральные отверстия в противоположном направлении, разрядными обмоТками 5 записи и выходными обмотками 6, проходящими через малые крайние отверстия сердечников;

Кроме того, устройство содержит формирователи 7 токов адресной выборки, на входы которых поступает код адреса и управляющие сигналы, а выходы соединены с обмотками 3 выбррки, разрядные формирователи 8 токов режима с входными схемами совпадения 9, иа их вход поступают сигналы с выходов разрядного коммутатора 10, а выходы формирователей 8 - с разрядными обмотками 4 режима, разрядные формирователи 1 токов записи, выходы последних соединены с разрядными обмотками 5 записи, а на вход поступают сигналы с выхода блока 12 вентилей, на вход которого поступает код записываемого числа с регистра 13 числа. Выходные обмоткй 6 соединены с входами усилителей 14 воспроизведения, выходы триггера 15 запоминания переноса связаны с блоком управления запоминающего устройства (на чертеже не показано), входы установки «1 - с выходом элемента ИЛИ 6 и с цепью 17 подачи единичных приращений, а вход установки «О - с элементом 18, на его входы поступают управляющие сигналы.

Устройство работает в режиме счета следующим образом.

Перед очередным добавлением единицы на кодовых шинах 19 адреса присутствует в потенциальной форме код адреса ячейки памяти, к содержимому которой необходимо прибавить единицу. Единичное приращение поступает н вход триггера 15 и устанавли-. йает триггер в состояние «1. Далее происходит считывание младшего разряда выбранной ячейки памяти на регистр 13 числа. Считывание только младщего разряда обеспечивается срабатыванием только одного формирователя тока режима, на вход этого формирователя поступает единичный сигиал разрядного коммутатора,

- Если считанный бит равен нулю, то процесс добавления единицы заканчивается при первом же обращении. Инвертированным сигналом с выхода элемента ИЛИ 16, выделяющей ненулеьые состояния регистра числа сбрасывается в «О триггер 15 а в младщий разряд ячейки памяти производится запись «1х. На этом процесс добавления «1 заканчивается.

Если считанный бит равен единице, то триггер 15 остается в состоянии «1. Тем самым запоминается перенос в следующий старший разряд. В данный разряд записывается «О - результат сложения по модулю 2 значения считанного бита и единичного

приращения. Далее разрядный коммутатор переводится в следующее состояние и производится обращение к очередному старщему разряду. Процесс повторяется до тех пор, , пока триггер-запоминания переноса не переключится в состояние «О по нулевому состоянию всех триггеров регистра числа по.сле очередного считывания или пока разрядный коммутатор не выдаст сигнал «Переполнение - Устройство может быть использовано для вычитания единичных приращений без измеJ нения операционной части. Необходимо только изменить последовательиость работы устройства управления, а именно, триггер сбрасывается в «О при значении считанного, бита, равного единице, в элемент памяти записывается «О и процесс вычитаиия заканчивается. Если значение считанного бита равно нулю, то триггер остается в состоянии «1, в ячейку памяти записывается единица, и разрядный коммутатор переводится в следующее состояние.

Формула изобретения

Магнитиое запомииающее устройство по авт.св. ,отличающееся тем, что, с целью расширения области применения устройства, оно содержит разрядный коммутатор, 6.ПОК вентилей и триггер запоминания переноса, выходы разрядного коммутатора соединены со входами разрядных формирователей токов режима, входы вентилей соединены с регистром числа, а выходы - с разрядными формирователями токов записи, входы установки «1 и «О триггера запоминания переноса соединены соответственно с выходами элемента ИЛИ и И, а выходы - с блоком управления запоминающего устройства.

Источиики информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 568971 кл. G II С П/08, 17.09.75.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386442A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР С ПАРАЛЛЕЛЬНЫМ СДВИГОМ | 1969 |

|

SU250544A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОСЙ1Ч '^ | 1972 |

|

SU436389A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU368605A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Логическое запоминающее устройство | 1972 |

|

SU442512A1 |

| Аналоговое запоминающее устройство | 1975 |

|

SU598127A1 |

| Счетчик импульсов | 1983 |

|

SU1112576A1 |

Авторы

Даты

1978-10-15—Публикация

1976-05-17—Подача