Изобретение относится к области вь числительной техники к может быть использовано при разработке буферных ЗУ высокого быстродействия. Известны буферные ЗУ, содержащие блоки управления, формирования адресов записи, регистры и логические элементы 1 и 121.. Одно из известных буферных ЗУ соцержит блок местного управления, блоки формирования адресов записи и счить вания, регистры и логические элементы 11. Недостатком устройства является его относительная сложность. Наиболее близким техническим реш&нием к изобретению является буферное ЗУ, содержащее, как и предложенное,бло местного управления, блок формирования адресов записи, блок формирования адресов считывания, регистры и группы элементов И по числу регистров. Вьтсоды к;аждогь регистра подключены к одни входам элементов И соответствующей группы, другие входы элементов И кажд группы объединены и соединены С выходами блока формирования адрес.ов считывания. Выходы элементов И всех групп поразрядно объединены и соединены с одноименными выходами устройства, а входы блока формирования адресов записи и блока формирования.адресов считывания подключены к выходам блока местного управления 2 . Недостатком известного устройства является его сложность и малое бьютродействие. Целью изобретения является упрощение и повышение быстродействия буферного ЗУ. Поставленная цель достигается рутем того, что в предложенном буферном ЗУ информационные входы регистров поразрядно объединены и соединены с одноименными входами устройства , а управляющие входы регистров подключены к выходам блока формирования адресов писи. В предложенном ЗУ считьгоание информации из регистров происходит по сигналам считывания, формируемым

блоком формирования адресов считывания, а запись информации в регистры - по окончании сигналов записи, формируемых блоком формирования ацресов записи,

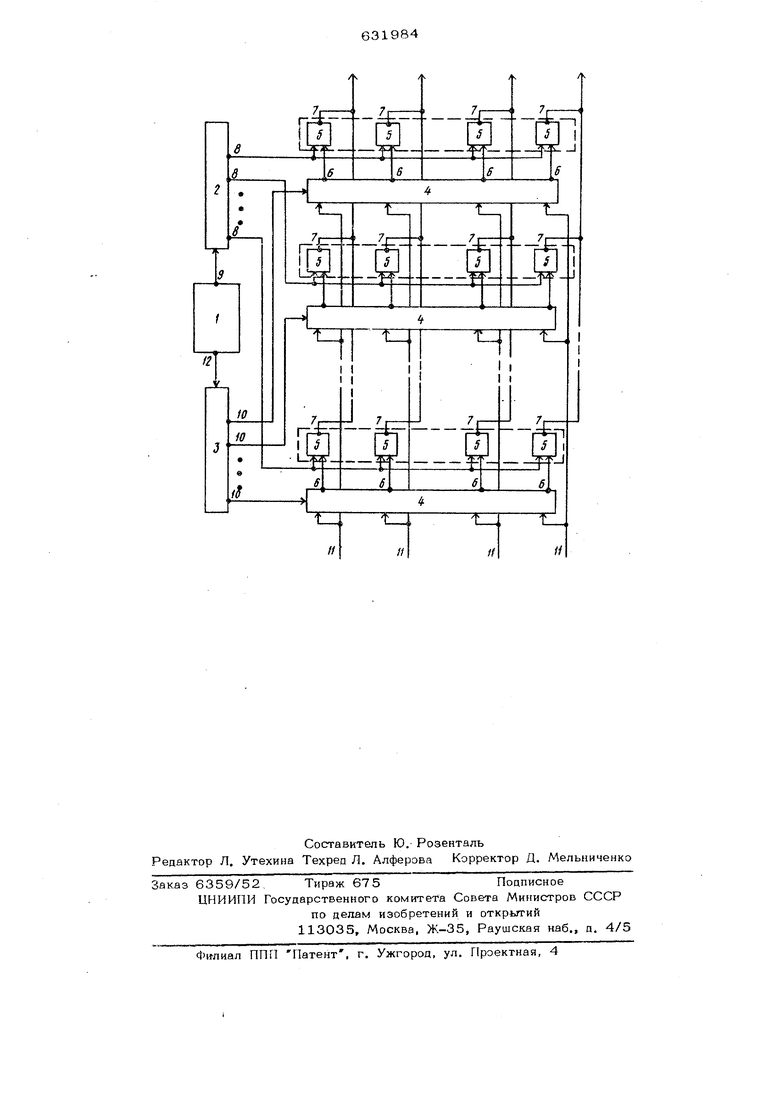

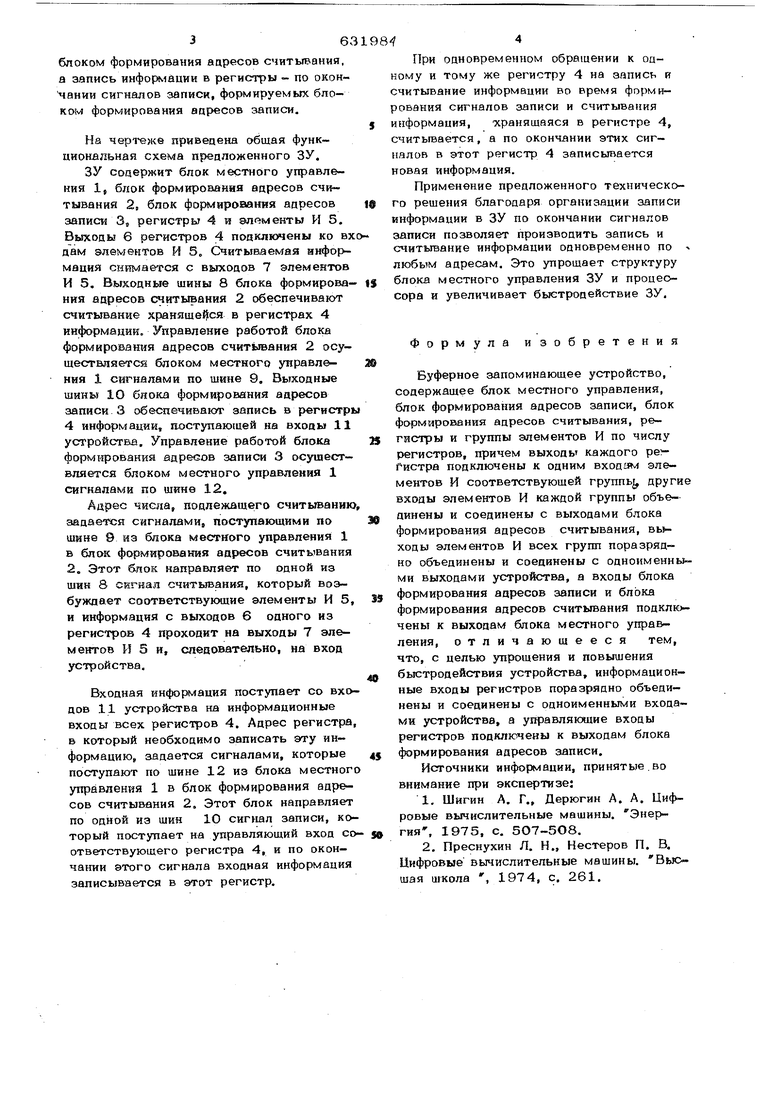

На чертеже привецена общая функциональная схема предложенного ЗУ.

ЗУ содержит блок местного управления 1, блок формирования ацресов считывания 2, блок формирования адресов записи 3s регистры 4 и элементы И 5. Выходы 6 регистров 4 подключены ко вхдам элементов И 5„ Считываемая информация снимается с выходов 7 элементов И 5. Вы ходные шины 8 блока формирования адресов считывания 2 обеспечивают считывание хранящейся в регистрах 4 информации. Управление работой блока формирования адресов считывания 2 осуществляется блоком местного ут равле- ния 1 сигналами по шине 9, Выходные шины 10 бнока формирования адресов записи 3 обеспечивают запись в регистры 4 информации, 1юст5гпающей на входы 11 устройства. Управление работой блока

формтфования адресов записи 3 осуществляется блоком местного управления 1 сигналами по шине 12.

Адрес числа, подлежвщего считыванию задаеэчзя сигналами, поступающими по

шине 9 ИЗ блока местного управления 1 в блок формирования ааресов считывания 2. Этот блок Направляет по одной из шин S сигнал считывания, который возбуждает соответствующие элементы И 5, и информация с выходов 6 одного из регистров 4 проходит на выходы 7 элементов И 5 и, следовательно, на вход устройства,

Входная информация поступает со входов 11 устройства на информационные входы всех регистров 4. Адрес регистра, в который необходимо записать эту информацию, задается сигналами, которые поступают по шине 12 из блока местного управления 1 в блок формирования адресов считывания 2. Этот блок направляет по одной из шин 1О сигнал записи, который поступает на управляющий вход со ответствующего регистра 4, и по окончании этого сигнала входная информация записывается в этот регистр.

При одновременном обращении к оцному и тому же регистру 4 на запись и считывание информации во время формирования сигналов записи и считывания информация, хранящаяся в регистре 4, считывается, а по окончании этих сигналов в этот регистр 4 записывается новая информация.

Применение предложенного технического решения благодаря организации записи информации в ЗУ по окончании сигналов

записи позволяет производить запись и считывание информации одновременно по любым адресам. Это упрощает структуру блока местного управления ЗУ и процессора и увеличивает быстродействие ЗУ,

Формула изобретения

Буферное запоминающее устройство, содержащее блок местного управления, блок формирования адресов записи, блок формирования адресов считывания, регистры и группы элементов И по числу регистров, причем выходы каждого ретРистра подключены к одним входам элементов И соответствующей rpynnbj, други входы элементов И каждой группы объединены и соединены с выходами блока формирования адресов считывания, выходы элементов И всех групп поразрядно объединены и соединены с одноименными выходами устройства, а входы блока формирования адресов записи и блока формирования адресов считывания подключены к выходам блока местного управления, отличающееся тем, что, с целью упрощения и повышения быстродействия устройства, информационные входы регистров поразрядно объединены и Соединены с одноименными входами устройства, а управляющие входы регистров подключены к выходам блока формирования ааресов записи.

Источники информации, принятые во внимание при экспертизе:

1.Шигин А. Г., Дерюгин А. А. Цифровые вычислительные машины, Энергия, 1975, с, 5О7-5О8,

2,Преснухин Л. Н., Нестеров П. В. Цифровые вычислительные машины. Высшая школа , 1974, с. 261.

ILJ

Ipr -Zpr fc

I I I I

I

j Ш LL

H

ti

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1979 |

|

SU849302A1 |

| Запоминающее устройство | 1979 |

|

SU842956A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1136173A1 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| Запоминающее устройство | 1974 |

|

SU487417A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1088066A1 |

Авторы

Даты

1978-11-05—Публикация

1977-04-06—Подача