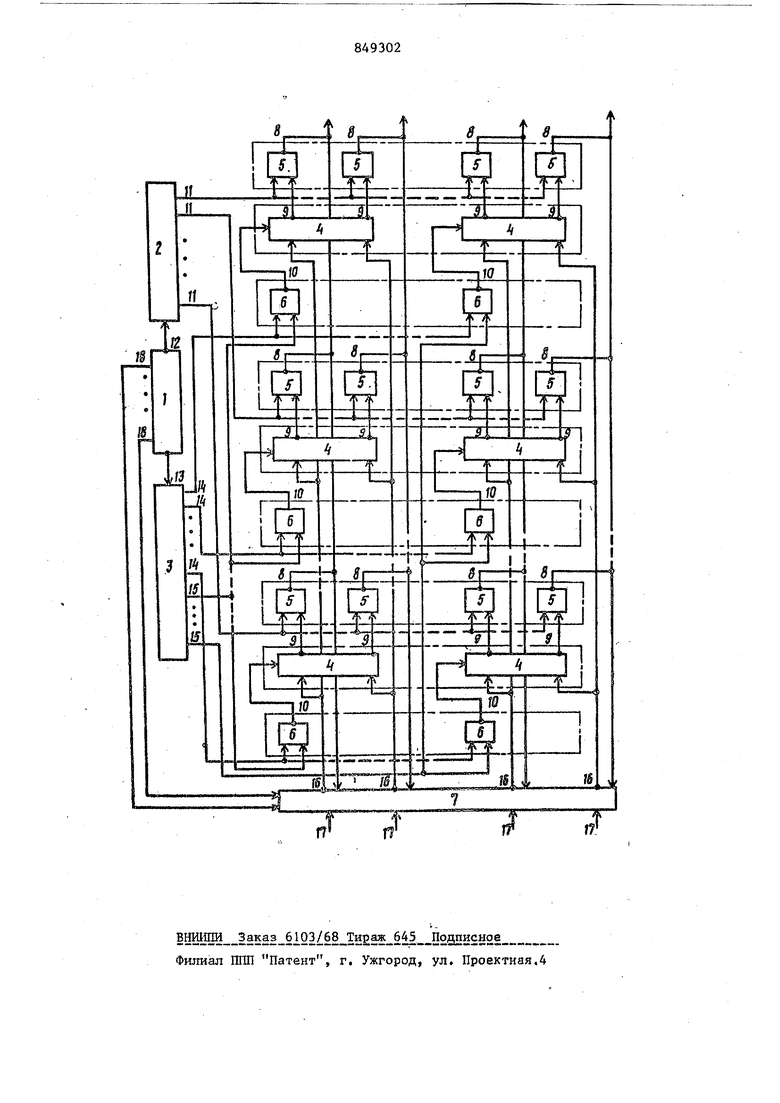

Изобретение относится к запомина щим устройствам. Известно буферное запоминающее устройство, которое содержит блок местного управления, блоки формирования адресов записи и считьшания, регистры и логические элементы f 1 . Недостатком устройства является его относительная сложность. Наиболее близким по технической сущности к предлагаемому является буферное запоминающее устройство, содержащее блок местного управления, блок формирования адресов записи, блок формирования адресов считьщ.ания, регистры и группы элементов И по числу регистров. Выходы каждого регистра зтого устройства подключены к одним входам элементов И соответствующей группы, другие входы эле ментов И каждой групЬы объединены и соединены с выходами блока формирова ния адресов считьшания. Выходы элеме тов И всех групп поразрядно объединены и соединены с одноименными выходами устройства. Входы блока формирования адресов записи и блока формирования адресов считывания подключены к выходам блока местного управления. Управляющие входы регистров соединены с выходами блока формирова.ния адресов записи, а информационные входы всех регистров поразрядно объединены С23. Недостатком известного устройства является невозможность осуществления сдвига хранящейся в любом регистре информации влево - вправо и перезаписи информации из регистра в регистр (часть регистра), что сужает ласть применения устройства. Цель изобретения - расширение области применения устройства за счет обеспечения возможности сдвига информации в регистрах. Поставленная цель достигается тем, что в буферное запоминанндее устройство, содержащее адресный блок считывания, адресный блок записи, блок местного управления, группы регистров и группы основных элементов И, причем выходы регистров групп подключены к одним из входов соответствуюпщх основных элементов И групп, другие входы основных элементов И каждой группы объединены и соединены с выходами адресного блока считьшания, выходы основных элементов И каждои группы поразрядно объединены и .соединены с одноименными выходами уст ройства, а входы адресного блока считьшания и адресного блока записи подключены к одним из выходов блока местного управления, введены коммутатор и группы дополнителЁных элементов Ц причем.выходы коммутатора соединены с информационными входами регистров групп, одни из входов соединены соответственно с выходами основных злементов И групп и другими выходами бло ка местного управления, а другие вход комь5утатора являются входами устройства, выходы дополнительных элементов И групп соединены с управляющими вход ми одноименных регистров групп, первые входы дополнительных элементов И каждой группы объединены и соединены с одними из выходов адресного блока записи, вторые входы одноименных допо нительных элементов И групп объединены и соединены с другими выходами адресного блока записи. На чертеже изображена функциональная схема предлагаемого устройства. Устройство .содержит блок 1 местного управления, адресный блок 2 считывания, адресный блок 3 записи, группы регистров 4, группы основных элементо И 5, группы дополнительных элементов И 6 и коммутатор 7 Выходы 8 элементов И 5 соединены с одними иэ входов коммутатора 7 и с одно1 менными выходами устройства, выходы 9 регистров 4 подключены к одним из входов элементов И 5. Выходы 10 элементов И 6 соединены с управляющими входами одноименных регистров 4. Выходы 11 блока 2 обеспечивают считывание информации, хранящейся в регист рах 4. Управление работой блока 2 осу ществляется блоком 1 местного управт Ленин сигналами по выходу .12. Управле ние работой блока 3 осуществляется блоком 1 местного управления сигналам по выходу 13. Выходы 14 и 15 блока 3 обеспечивают запись в регистры инфор824 мации, поступающей с выходов 16 коммутатора 7. Выходы I6 коммутатора 7 соединены с информационными входами регистров 4. Устройство имеет входы 17. Одни из входов коммутатора 7 соединены с выходами 18 блока 1, а другие входы коммутатора 7 являются входами I7 устройства . Первые входы элементов И каждой группы объединены и соединены с выходами 14 блока 3, вторые входы одноименных элементов И объединены и соединены с выходами 15 блока 3. Предлагаемое устройство работает следующим образом, В режиме считывания адрес числа, подлежащего считьшанию, определяется сигналамит поступающими с выхода 12 из блока 1 местного управления в блок 2. Этот блок направляет по одному из выходов 11 сигнал считьшания, который возбуждает элементы И 5 соответствующей группы, и информация с выходов 9 регистров 4 одной из групп поступает на выходы В элементов И 5 и на выходы устройства. При выполнении режимов записи, перезаписи и сдвига блок 1 местногг управления направляет в коммутатор 7сигнал по одному из выходов 18. 8зависимости от этого сигнала на выходы 16 коммутатора 7 поступает информация или со входов 17 устройства или с выходов В элементов И 5, причем при выполнении режима сдвига на выходе 16 коммутатора 7 поступает информация, сдвинутая в соответствующую сторону на соответствующее количество разрядов относительно информации, поступающей на входы коммутатора 7. При записи с выходов 16 коммутатора 7 снимается входная информация. Адрес, по которому необходимо ее записать, определяется сигналами, пос:тупающими из блока 1 местного управления в блок 3 по выходу 13. Этот блок направляет по одному из выходов 14я по одному или нескольким выходам 15сигналы записи, которые возбуждают элементы И 6 соответствующей группы, при этом по окончании сигналов с выходов 10 элементов И 6 происходит запись информации в соответствзтощий адресуемый регистр 4. При одновременном обращении к регистрам какой-либо группы на запись и считьшание во время- формирования

сигналов записи и считьюания, инфор-: мация, хранящаяся в данных регистрах 4, считывается, а по окончании этих сигналов в регистры 4 или часть регистров 4 группы записьшается новая информация.

При перезаписи информации из регистров i-ой группы в регистры к-й группы блок 2 вырабатьюает соответствующий сигнал, а блок 3 выраба-ю тывает сигнал записи в регистры 4 к-ой группы и сигналы записи в j-й регистр 4. По этим сигналам считьшае мая из регистров 4 i-ой группы инфор мация через элементы И 5 и коммутатор 7 подается на информационные вхо ды регистров 4 и по окончании сигна лов записи записывается в. регистры 4 к-ой группы. При сдвиге хранящейся в i-м ре- гистре 4 информации, например вправо на к разрядов, блок 3 и блок 2 нап- равляют сигналы записи и считьшания в i-й регистр 4. Коммутатор 7 подает на информационные входы регистров 4 считьюаемую из t-ro регистра 4 информацию, сдвинутую на к разрядов вправо. Применениепредлагаемого устройства позволяет производить в запоминающем устройстве сдвиг хранящейся информации влево-вправо и перезапись информации из регистра в регист Это позволяет выполнять часть логических операций непосредств енно в запоминающем устройстве, что разгружает от выполнения этих операций про цессор и, следовательно увеличивает его быстродействие. Кроме того, возможность вьшолнени операций сдвига непосредственно в за поминающем устройстве позволяет производить обмен информацией с этим устройством как в параллельном, так и в последовательном коде. Это исключает необходимость применения схе сопряжения и, таким образом, упрощае структуру процессора.

Формула изобретения Буферное запоминающее устройство,. содержащее адресный блок считьшания, адресный блок записи, блок местного управления, группы регистров и группы основных элементов И, причем выходы регистров групп-подключены к одним из входов соответствующих основных элементов И групп, другие входы основных элементов И каждой группы объединены и соединены с выходами адресного блока считьшания, выходы основных элементов И каждой группы поразрядно объединены и соединены с одноименными вьрсодами устройства, а входы адресного блока считьшания и адресного блока записи подключены к одним из выходов блока местного управления, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности сдвига информации в регистрах,, оно содержит коммутатор и группы дополнительных элементов И, причем выходы коммутатора соединены с информационными входами регистров групп, одни из входов соединены соответственно с выходами оснЬвных элементов И групп и другими выходами блока местного уп- равления, а другие входы коммутатора являются входами устройства, выходы дополнительньбс элементов И групп соединены с управляющими входами одноименных регистров групп, первые входы дополнительных элементов И каждой группы объединены и соединены с одними из выходов адресного блока записи, вторые входы одноименных-дополнительных элементов И групп объединены и соединены с другими выходами адресного блока записи. Источники информации, принятые во внимание при экспертизе 1.Шигин А.Г. и Дерюгин А.А. Цифровые вычислительные машины. М., Энергия, 1975, с. 507-508.. 2.Авторское свидетельство СССР 631984, кл. G il С 11/00, 1977. (прототип).

™--J

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1977 |

|

SU631984A1 |

| Запоминающее устройство | 1979 |

|

SU842956A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1986 |

|

SU1367021A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU983752A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1124384A1 |

Авторы

Даты

1981-07-23—Публикация

1979-11-01—Подача