(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1124384A1 |

| Запоминающее устройство со считыванием без разрушения информации | 1979 |

|

SU773724A1 |

| Запоминающее устройство | 1983 |

|

SU1246137A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Буферное запоминающее устройство | 1979 |

|

SU849302A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

1

Изобретение относится к запоминающим устройствам и может быть использовано в качестве сверхоперативной памяти или буферного запоминающего устройства.

Известно устройство, содержащее блок местного управления, дешифратор, регистры и элементы И по две группы на каждый регистр 1.

Недостатком этого устройства является малое быстродействие.

Наиболее близким техническим рещением к предлагаемому является буферное запоминающее устройство, содержащее блок местного управления, блоки формирования адресов записи и считывания, регистры и группы элементов И по числу регистров, выходы каждого регистра подключены к одним входам элементов И соответствующей группы, другие входы элементов И каждой группы объединены и соединены с выходами блока формирования адресов считывания, выходы элементов И всех групп поразрядно объединены и соединены с одноименными выходами устройства, входы блоков формирования адресов записи и считывания подключены к выходам блока местного упра-вления, информационные входы регистров поразрядно объединены и соединены с одноименными входами устройства. Управляющие входы регистров подключенных к выходам блока формирования адресов записи 2.

Недостатками этого устройства являются невысокие быстродействия и надежность, обусловленные тем, что при одновременном обращении к.одному и тому же регистру на запись и считывание,.информация сначала считывается, а затем записывается, что возможно только в том случае, если информация существует на входных щинах достаточно долго, а если информация поступает на запись асинхронно со считыванием и со скоростью, равной или близкой к скорости записи, возможны потери информации.

Цель изобретения - повышение быстродействия и надежности устройства.

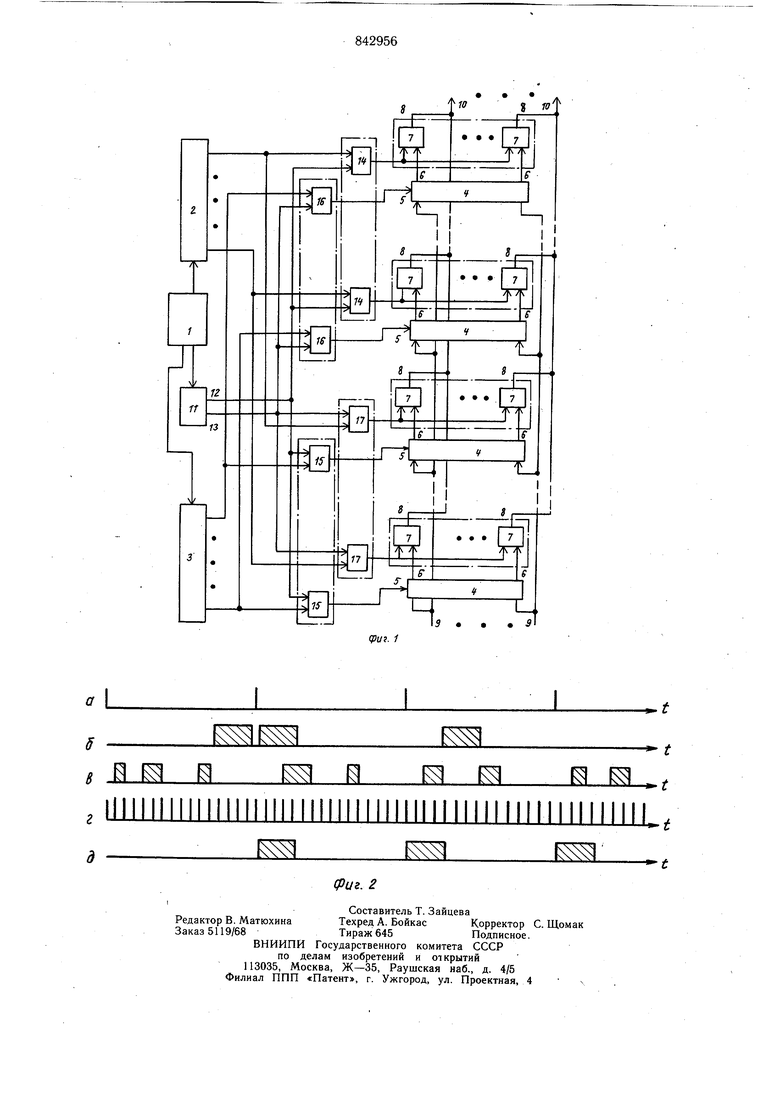

Поставленная цель достигается тем, что в запоминающее устройство, содержащее регистры, группы элементов И по числу регистров, блок местного управления, формирователь адресных сигналов записи и формирователь адресных сигналов считывания, причем выходы регистров подключены к первым входам элементов И соответствующей группы, выходы элементов И групп соедийены с одноименнь1м;1 выходами устройства, информационные входы регистров соединены с одноименными входами устройства, входы формирователей адресных сигналов считывания и записи подключены соответственно к первому и второму выходам блока местного управления, введены коммутатор и четыре группы дополнительных элементов И, причем вход коммутатора подключен к третьему выходу блока местного управления, а первый и второй выходы соединены с первыми входами дополнительных элементов И первой и второй групп и третьей и четвертой групп соответственно, вторые входы дополн11тельных элементов И первой и четвертой групп подключены к соответствующим выходам формирователя адресных сигналов считывания, вторые входы дополнительных элементов И второй и третьей групп соединены с соответствующими выходами формирователя адресных сигналов записи, выходы дополнительных элементов третьей и первой групп подключены соответственно к управляющим входам одних из регистров и ко вторым входам элементов И соответствующих групп, выходы дополнительных элементов И второй и четвертой групп соединены соответственно с управляющими входами других регистров и со вторыми входами элементов И соответствующих групп. На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 -временные диаграммы работы устройства. Устройство содержит (фиг. 1) блок 1, местного управления, формирователь 2 адресных сигналов считывания, формирователь 3 адресных сигналов записи, регистры 4 с управляющими входами 5 и выходами б, группы элементов И 7 с выходами 8, входы 9 и выходы 10 устройства, коммутатор 11 с первым 12 и вторым 13 выходами, первую 14, вторую 15, третью 16 и четвертую 17 группы дополнительных элементов И. Выходы 6 регистров 4 подключены к первым входам элементов И 7 соответствующей группы. Выходы элементов И 7 групп с-оединены с одноименными выходами 10 устройства. Информационные входы регистров 4 соединены с одноименными входами 9 устройства. Входы формирователя 2 адресных сигналов считывания и формирователя 3 адресных сигналов записи подключены соответственно к первому и второму выходам блока 1 местного управления. Вход коммутатора 11 подключен к третьему выходу блока 1 местного управления, а первый 12 и второй 13 выходы соединены с первыми входами дополнительных элементов И первой 14 и второй 15 групп, третьей 16 и четвертой 17 групп соответственно. Вторые входы дополнительных элементов И первой 14 и четвертой 17 групп подключены к соответствующим выходам формирователя 2 адресных сигналов считывания. Вторые входы дополнительных элементов И второй 15 и третьей 16 групп, соединены с соответствующими выходами формирователя 3 адресных сигналов записи. Выходы дополнительных элементов третьей 16 и первой 14 групп подключены соответственно к управляющим входам 5 одних из регистров 4 и ко вторым входам элементов И 7 соответствующих групп. Выходы дополнительных элементов И второй 15 и четвертой 17 групп соединены соответственно с управляющими входами 5 других регистров 4 и со вторыми входами элементов И 7 соответствующих групп. На фиг. 2 изображены сигналы определенной частоты, переключающие коммутатор 11 (фиг. 2а) и поступающие для записи в устройство информационные сигналы с более высокой частотой (фиг. 26) или пачками слов (фиг. 28). На фиг. 2г и 2(3 показаны информационные сигналы, считываемые из запоминающего устройства. Устройство работает следующим образом. По сигналам блока 1 местного управления (фиг. 1) поступающим на вход комму-татора 11, одни из регистров 4 выбираются для записи в них информации, а другие - для считывания информации из них, что определяется сигналами с выходов коммутатора 11. Если с первого выхода 12 коммутатора ,11 выдается сигнал разрещения, то со второго выхода 13 - сигнал запрета, и наоборот. Сигнал разрешения, выдаваемый с первого выхода 12 коммутатора 11, открывает дополнительные элементы И первой 14 и второй 15 групп , а сигнал запрета со второго выхода 13 закрывает дополнительные элементы И третьей 16 и четвертой 17 групп . В этом случае одна половина регистров 4 (верхние на фиг. 1) выбрана для считывания, а другая половина регистров 4 выбрана для записи. Формирователь 3 адресных сигналов записи по сигналам блока 1 местного управления вырабатывает адрес регистра 4, в который должна быть записана информация, поступающая по входам 9 устройства на входы всех регистров 4. Сигналы записи через дополнительные элементы И второй 15 группы поступают на управляющие входы 5 регистров 4, обеспечивая запись информации. Одновременно по сигналам, поступающим с блока 1 местного управления, формирователь 2 адресных сигналов считывания вырабатывает адреса регистров 4, с которых должна быть считана информация. Сигналы считывания через дополнительные элементы И первой 14 группы поступают на вторые входы элементов И 7 соответствующих групп. с выхода 6 выбранного регистра 4 проходит на выходь 8 элементов И 7 группы, а затем на выходы 10 устройства. Если сигнал разрещения со второго выхода 13 коммутатора 11 поступает на элементы И третьей 16 и четвертой 17 групп и открывает их, а сигнал запрета, поступающий с первого выхода 12 коммутатора И, закрывает дополнительные элементы И первой 14 и второй 15 групп, то-верхняя половина регистров 4 выбрана для записи, а нижняя для считывания. В этом случае сигналы записи поступают на входы дополнительных элементов И третьей 16 группы, а с их выходов на управляющие входы 5 соответствующих регистров 4,, обеспечивая запись информации. Одновременно сигналы считывания поступают на входы дополнительных элементов И четвертой группы 17, а с их выходов на объединенные вторые входы элементов И 7 групп, и разрещают считывание информации. Переключение коммутатора 11 может производиться внещними сигналами (фиг. 2а) после записи или после считывания информации из одной половины регистров 4. Если информация в устройстве отсутствует, то коммутатор 11 не переключается и считывание не происходит. Предлагаемое буферное запоминающее устройство является унифицированным. Если информация поступает на запись с более высокой частотой и пачками слов в произвольные моменты времени (фиг. 26 или 2в), оно может при считывании передавать информацию с трансформированной частотой и более равномерно (фиг. 2г и 2д). В предлагаемом устройстве скорость записи информации определяется только быстродействием регистров, формирователя адресных сигналов записи, а считывания - быстродействием формирователя адресных сигналов считывания и элементов И групп, так как обращение на запись и считывание всегда производятся к разным регистрам 4 запоминающего устройства, за счет чего достигается высокое быстродействие и повыщается надежность устройства. Формула изобретения Запоминающее устройство, содержащее регистры, группы элементов И по числу регистров, блок местного управления, формирователь адресных сигналов записи и формирователь адресных сигналов считывания, причем выходы регистров подключены к первым входам элементов И соответствующей группы, выходы элементов И групп соединены с одноименными выходами устройства, информационные входы регистров соединены с одноименными входами устройства, входы формирователей адресных сигналов считывания и записи подключены соответственно к первому и второму выходам блока местного управления, отличающееся тем, что, с целью повыщения быстродействия и надежности устройства, оно содержит коммутатор и четыре группы дополнительных элементов И, причем вход коммутатора подключен к третьему выходу блока местного управл ения, а первый и второй выходы соединены с первыми входами дополнительных элементов И первой и второй групп и третьей и четвертой групп соответственно, вторые входы дополнительных элементов И первой и четвертой групп подключены к соответствующим выходам формирователя адресных сигналов считывания, вторые входы дополнительных элементов И второй и третьей групп соединены с соответствующими выходами формирователя адресных сигналов записи, выходы дополнительных элементов третьей и первой групп подключены .соответственно к управляющим входам одних из регистров и ко вторым входам элементов И соответствующих групп, выходы дополнительных элементов И второй и четвертой групп соединены соответственно с управляющими входами других регистров и со вторыми входами элементов И соответствующих групп. Источники информации, принятые во внимание при экспертизе 1.Шигин А. Г. и Дерюгин А. А. Цифровые вычислительные мащины. М., «Энергия, 1975, с. 508. 2.Авторское свидетельство СССР № 631984, кл. G II С 11/00, 1977 (прототип).

Авторы

Даты

1981-06-30—Публикация

1979-07-11—Подача