1

Изобретение относится к вычисли- тельной технике.

Известны способ аналого-цифрового преобразования и устройство для его осуществления. Способ основан на последовательном усилении разностного сигнала пороговых напряжений, а устройство содержит усзилители, пороговые устройства и источник эталонных напряжений l .

Однако быстродействие и точность такого способа недостаточны.

Известен способ аналого-цифрового, преобразования, основанный на поразрядном уравновешивании компенсирующим сигналом отрицательной обратной связи входного сигнала и сравнении разностного сигнала, равного алгебраической сумме компенсирующего и входного напряжений, с эталонным напряжением, и устройство для его реализации содержащее цифро-аналоговый преобразователь (ЦАП), выход которого соединен с первым входом дифференциального усилителя, второй вход которого соединен с первым входом компаратора, старшего разряда, выход которого соег динен с входом старшего разряда ЦАП;, Второй вход компаратора соединен с входом старшего разряда блока эталонных уровней, а входная шина устройст ва - со входом знакового компаратора 2. Однако такие способ и устрой ство недостаточно быстродейственны, а устройство сложно.

Цель изобретения - повышение быстточности способа и упрородействия,

щение устройства.

Это достигается тем, что по предложенному способу формируют зону чувствительности каждого разряда из зталонных напряжений данного и предыдущего разрядов, сравнивают одновремен но разностный сигнал с зонами чувствительности всех разрядов и используют сигнал о нахождении данного разностного сигнала в зоне для получения компенсирующего нагфяжения отрицателЬ..ой обратной связи.

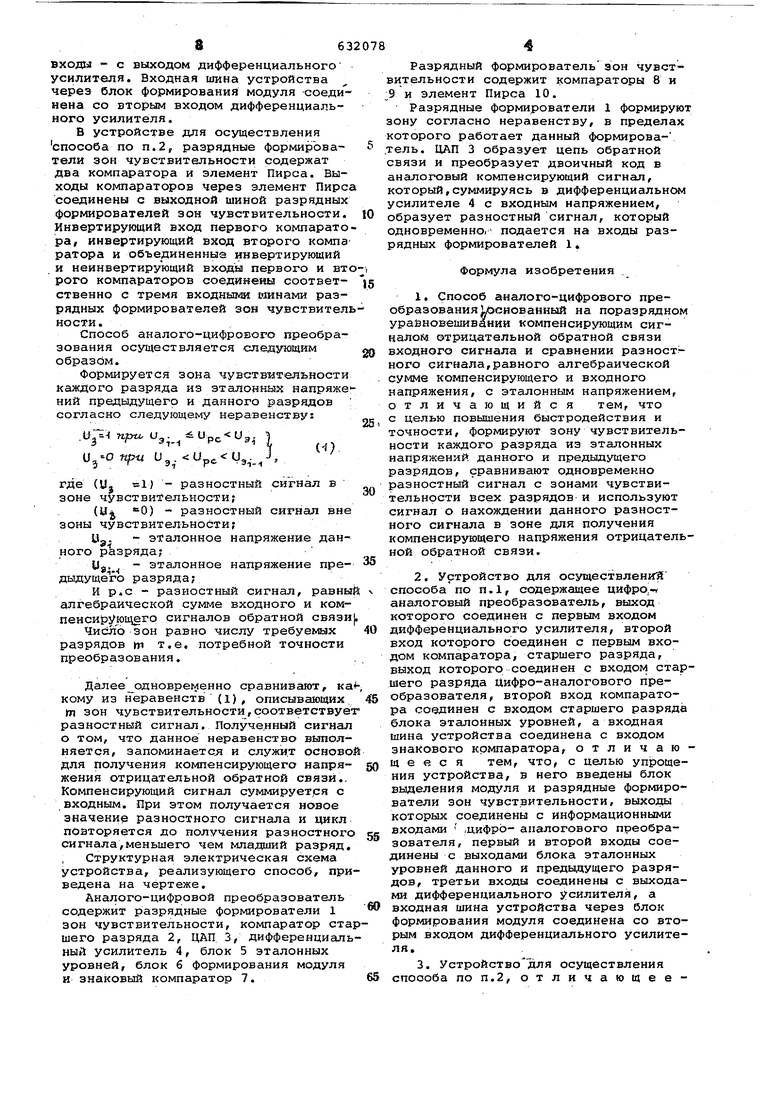

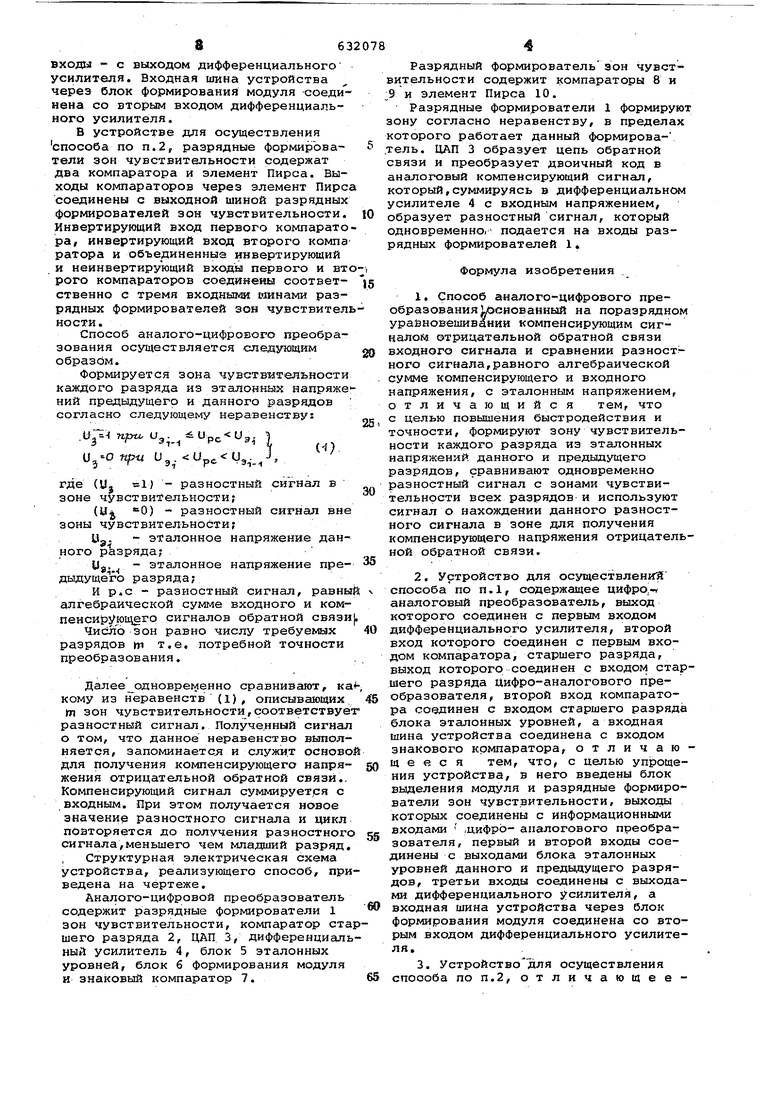

В устройство для осуществления способа по П.1, содержащее ЦАП, блок эталонных уровней,компаратор, знаковый компаратор и дифференциальный усилитель,введены блок выделения модуля и разрядные формирователи зон чувствительности, выходы которых, соединены с информационными входами ЦАП, первый и второй входы соединены с Ёыходами блока эталонных уровней данного и предыдущего разрядов,третьи ВХОДЫ - с выходом дифференциального усилителя. Входная шина устройства через блок формирования модуля соединена со вторьш входом дифференциального усилителя. В устройстве для осуществления способа по п.2, разрядные формироватали зон чувствительности содержат лва компаратора и элемент Пирса. Выходы компараторов через элемент Пирс соединены с выходной шиной разрядных формирователей зон чувствительности. Инвертирующий вход первого компарато ра, инвертирующий вход второго компа ратора и объединенные инвертирующий и неинвертирующий входы первого и BT рого компараторов соединены соответственно с тремя входными воинами разрядных формирователей зон чувствител ности. Способ аналого-цифрового преобразования осуществляется следующим образом. Формируется зова чувствительности каждого разряда из зталонньзх наиряже ний предьщущего и данного разрядов согласно следующему неравенству: . Ttpt U3.,. и,. ., где (U, 1) - разностный сигнал в зоне чувствительности; (U О) - разностный сигнал вне зоны чувствительности; Ug. - эталонное напряжение данного pkзpядa; Uj. . - эталонное напряжение предьвдущего разряда; И р.с - разностный сигнал, равны алгебраической сумме входного и компенсирующего сигналов обратной свяэи Число зон равно числу требуемых разрядов tti т.е. потребной точности преобразования. Далее одновременно сравнивают, ка кому из неравенств (1) , описывающих (п зон чувствительности,соответствуе разностный сигнал. Полученный сигнал о том, что данное неравенство выполняется, запоминается и служит осново для получения компенсирующего напряжения отрицательной обратной связи.. Компенсирующий сигнал суммируется с входным. При этом получается новое значение разностного сигнала и цикл повторяется до получения разностного сигнала,меньшего чем младший разряд. Структурная электрическая схема устройства, реализующего способ, при ведена на чертеже. Аналого-цифровой преобразователь содержит разрядные формирователи 1 зон чувствительности, компаратор ста шего разряда 2, ЦАП 3, дифференциаль ный усилитель 4, блок 5 эталонных уровней, блок б формирования модуля и знаковый компаратор 7. Разрядный формировательзон чувствительности содержит компараторы 8 и 9 и элемент Пирса 10. Разрядные формирователи 1 Формируют зону согласно неравенству, в пределах которого работает данный формирователь. ЦАП 3 образует цепь обратной связи и преобразует двоичный код в аналоговый компенсирующий сигнал, который,суммируясь в дифференциальном усилителе 4 с входным напряжением, образует разностный сигнал, который одновременнО| подается на входы разрядных формирователей 1. Формула изобретения 1.Способ аналого-цифрового преобразования ЬЬеиованный на поразрядном уравновешивании компенсирующим сигналом отрицательной обратной связи входного сигнала и сравнении разностного сигнала,равного алгебраической сумме компенсирующего и входного напряжения, с эталонным напряжением, отличающийся тем, что с целью повышения быстродействия и точности, формируют зону чувствительности каждого разряда из эталонных напряжений данного и предьщущего разрядов, сравнивают одновременно разностный сигнал с зонами чувствительности всех разрядов и используют сигнал о нахождении данного разностного сигнала в зоне для получения компенсируквдего напряжения отрицательной обратной связи. 2.Устройство для осуществлений способа по П.1, содержащее цифро,-/ аналоговый преобразователь, выход которого соединен с первым входом дифференциального усилителя, второй вход которого соединен с первым входом компаратора, старшего разряда, выход которого соединен с входом старшего разряда цифро-аналогового преобразователя, второй вход компаратора соединен с входом старшего разряда блока эталонных уровней, а входная шина устройства соединена с входом знакового компаратора, отличающееся тем, что, с целью упрощения устройства, в него введены блок выделения модуля и разрядные форютрователи зон чувствительности, выходы которых соединены с информационными входами ,цифро- аналогового преобразователя, первый и второй входы соединены с выходами блока эталонных уровней данного и предыдущего разрядов, третьи входы соединены с выходами дифференциального усилителя, а входная шина устройства через блок формирования модуля соединена со вторым входом дифференциального усилителя, 3.Устройстводля осуществления способа по п.2, отличающеес я тем, что разрядные формирователи зон чувствительности содержат рва компаратора и элемент Пирса, причем выходы компараторов через элемент Пирса соединены с выходной шиной разрядных формирователей зон чувствитель|ности, инвертирующий вход первого компаратора,инвертирующий вход второго компара:тора и объединенные инвер:тирующий и неинвертирующий входы перieoro и второго компараторов соединены чзортветственно с тремя входными шинами разрядных формирователей зон чувствадельности.

Источники информации, принятые во внимание при экспертизе:

Д. Смолов В.Б. Полупроводниковые; кодирующие и декодирующие преобразователи напряжений М., Энергия 1967, с. 128-142.

2. Авторское свидетельство СССР № 291335, Н 03 К 13/02, 1967.

| название | год | авторы | номер документа |

|---|---|---|---|

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Преобразователь код-напряжение | 1984 |

|

SU1197084A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 2003 |

|

RU2245000C2 |

| Устройство для считывания графической информации | 1987 |

|

SU1506460A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

Авторы

Даты

1978-11-05—Публикация

1977-04-26—Подача