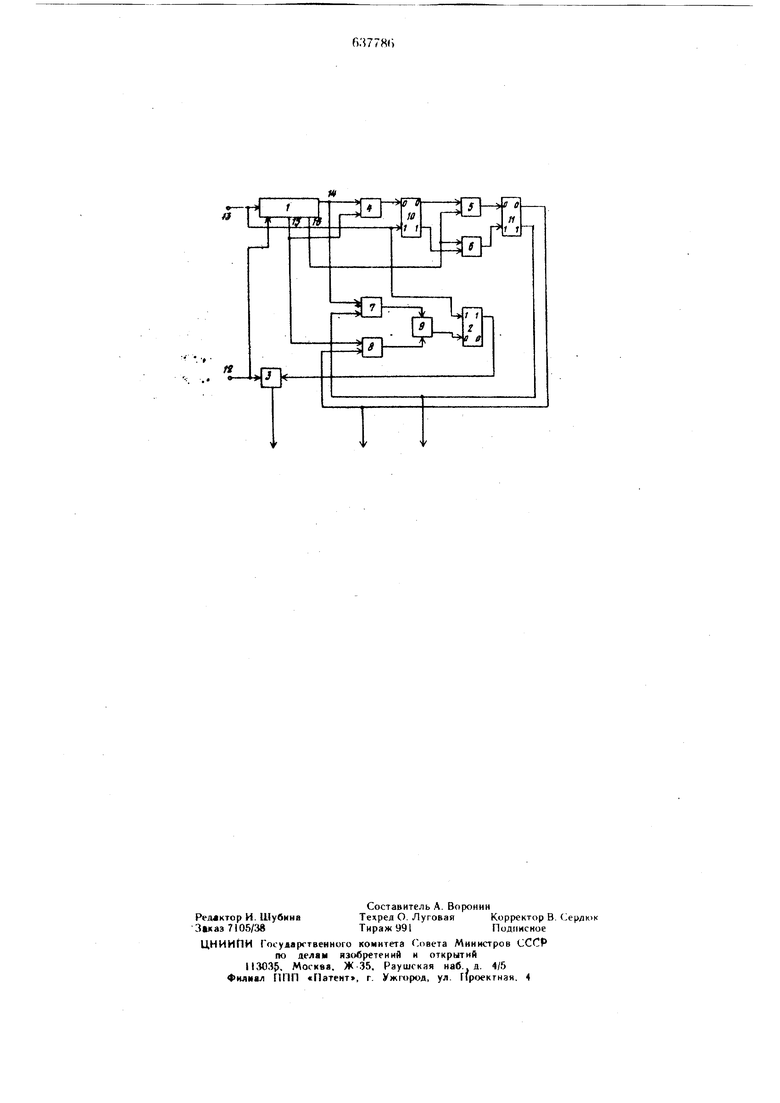

соответственно, один из входов которого соединен с .выходом второго элемента И, другой вход - с первой шиной управления, выходы пятого и шестого элементов И соединены соответственно со входами второго дополнительного триггера, первый выход которого гюдключен к другому входу третьего элемента И, выход второго дополнительного триггера соединен с другим входом четвертого элемента И, выходы третьего и четвертого элементов И подключены через элемент ИЛИ к нулевому входу основного триггера. На чертеже приведена функциональная схема предлагаемого устройства, содержащего регистр i, основной триггер 2, элементы И 3-8, элемент ИЛИ 9, дополнительные триггеры 10, И, шины управления 12, 13. Устройство работает следующим образом. Управляющие сигналы определяют момент времени начала процесса записи и сдвига информации в устройствах обработки информации (накопители, ЗУ и др.) и поступают по первой шине управления 13 на вход регистра I и единичные входы триггеров 2, 10. На вторую шину управления поступают импульсы сдвига информации в накапливающих линейках устройств обработки информации. В исходном состоянии триггер 2 запрещает прохождение через элемент 3 импульсов сдвига информации на устройство обработки информации. С приходом управляющего импульса триггер 2 устанавливается в единичное состояние, разрешая прохождение через элемент 3 импульсов сдвига на накапливающие линейки устройства обработки информации. Одновременно, при поступление управляющего импульса устанавливается в единич ное состояние триггер 10 и первый разряд регистра I, и по импульсам-сдвига, поступающим на второй вход регистра 1 происходит последовательная установка в единичное состояние последующ,их разрядов. Предыдущие разряды регистра при этом возвращаются в нулевое состояние. На выходах 14, 15 регистра 1 вырабатываются импульсы, задержанные относительно управляющих. Время задержки этих импульсов определяется количеством разрядов между входом и соответствующим выходом регистра 1 и частотой следования импульсов сдвига, поступакмяих на регистр 1.. Количество разрядов регистра I между промежуточным 5 и основным 14 выходами регистра 1 выбирается так, чтобы время задержки сигнала на этом участке регистра равнялось периоду повторенияуправляющих импульсов, следующих с более высокой частотой. Дополнительный выход 16 регистра выбирается между промежуточным 15 и основным 14 выходами и является вспомогательным выходом 16, необходимым д/1я работы схемы автомятичсского ог|редолсиия част(эты следования управлнюпи(х импульсов. По истечении времени, равного периоду повторения управляющих импульсов, следующих с частотой fi, на выходах 14 и 15 регистра } вырабатываются импульсы, которые поступают на входы элемента 4, в результате чего на его выходе появляется сигнал, который переводит триггер 10 в нулевое состояние. Потенциал, который вырабатывается на нулевом выходе триггера 10, разрешает прохождение через элемент 5 на нулевой вход триггера I импульсов, поступающих на элементы 5 и 6 с дополнительного выхода 16 регистра I. Через элемент 6 этот импульс не проходит, так как в это время он забло.кирован запрещающим потенциалом, который подается на схему с единичного выхода триггера 10. Триггер 11 переводится в нулевое состояние и на его нулевом выходе вырабатывается разрешающий потенциал, который поступает на элемент 8 и на устройство обработки информации (или ЗУ), при этом в нем подключаются накапливающие линейки с временем задержки (длиной), соответствующим периоду повторения управляющих импульсов следующих с частотой fi. Устройство обработки информации при этом осуществляет накопление сигналов, поступающих на его вход с частотой, синхронной частоте управляющих импульсов fi. На выходе вырабатывается сигнал обнаружения. Через элемент 8 и элемент ИЛИ 9 на нулевой вход триггера 2 подается управляющий импульс, вырабатываемый на выходе 15 регистра 1. Этим импульсом триггер 2 возвращается в исходное ну.левое состояние и запрещает прохождение через элемент 3 импульсов сдвига на устройство обработки информации. Следующий управляющий импульс, который поступает с шины 13 на вход регистра 1 и единичные входы триггеров 2 и 10, переводит триггер 2 в единичное состояние, при этом триггер 2 разрешает поступление импульсов сдвига информации через элемент 3 на устройство обработки информации. Таким образом осуществляется следующий цикл накопления информации. Разрешающий потенциал, который вырабалывается в этом случае на единичном выходе триггера 10, при частоте следовния импульсов fi не изменяет нулевого состояния триггера 11, так как после каждого управляющего импульса, начиная со второго, на выходе элемента 4 вырабатываются импульсы, которые переводят триггер 10 опять в нулевое состояние, после чего нулевое состояние триггера 11 подтверждается импульсами, поступающими на его нулевой вход с дополнительного выхода 16 регистра 1. При низкой частоте следования управляющих импульсов fj на выходе элемента 4 импу.чьсы не вырабатываются. При этом триг гер 0, который устанавливается в единичное состояние управляющим импульсом, поступающим на его единичный вход с шины 13 своего состояния не изменяет. В этом случае импульсы, которые вырабатываются на дополнительном выходе 16 регистра, поступают через элемент 6 на единичный вход триггера 11 и переводят его в единичное состояние- Разрешающий потенциал, который вырабатывается в этом случае на единичном выходе триггера II, подается на элемент 7 и на устройство обработки информации; при этом в устройстве обработки информации подключаются накапливающие линейки с временем задержки (длиной), соответствующим периоду построения управляющих импульсов, следующих с частотой f. Устройство обработки информации при этом осуществляет накопление сигналов, поступающих на его вход с частотой, синхронной частоте управляющих импульсов fj. Через элемент 7 и элемент ИЛИ 9 на нулевой вход триггера 2 поступает импульс, который вырабатывается на выходе 14 регистра 1. Этот импульс переводит триггер 2 в исходное нулевое состояние, в результате чего запрещается прохождение импульсов сдвига на устройство обработки информации до поступления следующего управляющего импульса. Количество разрядов в регистре 1 между его входом и выходами - промежуточным 15 и основным 14 соответствует количеству элементов задержки каждой накааливающей линейки устройства обработки информации. Количество разрядов частей регистра и частей накапливающих линеек устройства обработки информации выбирается из условия соответствия времени задержки каждой из частей периоду повторения управляющих сигналов. Поэтому количество импульсов сдвига, проходящих через элемент 3 на устройство обработки информации по каждому управляющему сигналу всегда строго постоянно, равно количеству элементов задержки каждой накапливающей линейки устройства обработки информации и не зависит от периода повторения соответствующих управляющих импульсов при условии, что период их повторения больше времени прохождения импульсов через соответствующую часть регистра управления. Вместо регистра управления могут использоваться другие устройства задержки, например счетчик с дешифраторами и др. П|)ямеионие д;)ниогг) блока управления ()ляет автоматизировать процесс обработки информации при работе устройства обработки информации с несколькими управляющими сигналами, кроме того, повысить надежность работы устройства обработки информации, так как устраняются связи, которые необходимо вводить между блоком упраапения, устройством обработки информации и внешними устройствами управления при ручном способе управления. Формула изобретения Блок управления для запоминающего устройства, содержащий регистр, первый вход которого подключен к единичному входу основного триггера и к первой шине управления, второй вход регистра соединен с одним из входов первого элемента И и второй щиной управления, другой вход первого элемента И соединен с единичным выходом основного триггера, выход первого элемента И подключен к выходу блока управления, отличающийся тем, что, с целью расширения области применения блока управления, в него введены элемент ИЛИ, дополнительные триггеры и элементы И, один из входов второго и третьего элементов И соединены с первым выходом регистра, второй выход которого подключен к другому входу второго и одному из входов четвертого элементов И, третий выход регистра соединен с одними из входов пятого и шестого элементов И, другие входы которых соединены с нулевым и единичным выходами первого дополнительного триггера соответственно, один из входов которого соединен с выходом второго элемента И, другой вход - с первой щи ной управления, выходы пятого и шестого элементов И соединены соответственно со входами второго дополнительного триггера, первый выход которого подключен к другому входу третьего элемента И, второй выход второго, дополнительного триггера соединен с другим входом четвертого элемента И, выходы третьего и четвертого элементов И подключены через элемент ИЛИ к нулевому входу основного триггера. Источники информации, принятые во внимание при экспертизе: 1,Кузьмин С. 3. Цифровая обработка радиатокационной информации, иэд-во «Сов. радио, 1967. 2.Авторское свидетельство СССР № 428454, кл. G 11 С 19/00, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| Устройство для программного управления | 1985 |

|

SU1290263A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1339554A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для считывания графической информации | 1988 |

|

SU1606980A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU658564A2 |

| Устройство для моделирования адаптивных вычислительных систем | 1981 |

|

SU1020830A1 |

Авторы

Даты

1978-12-15—Публикация

1975-01-06—Подача