2

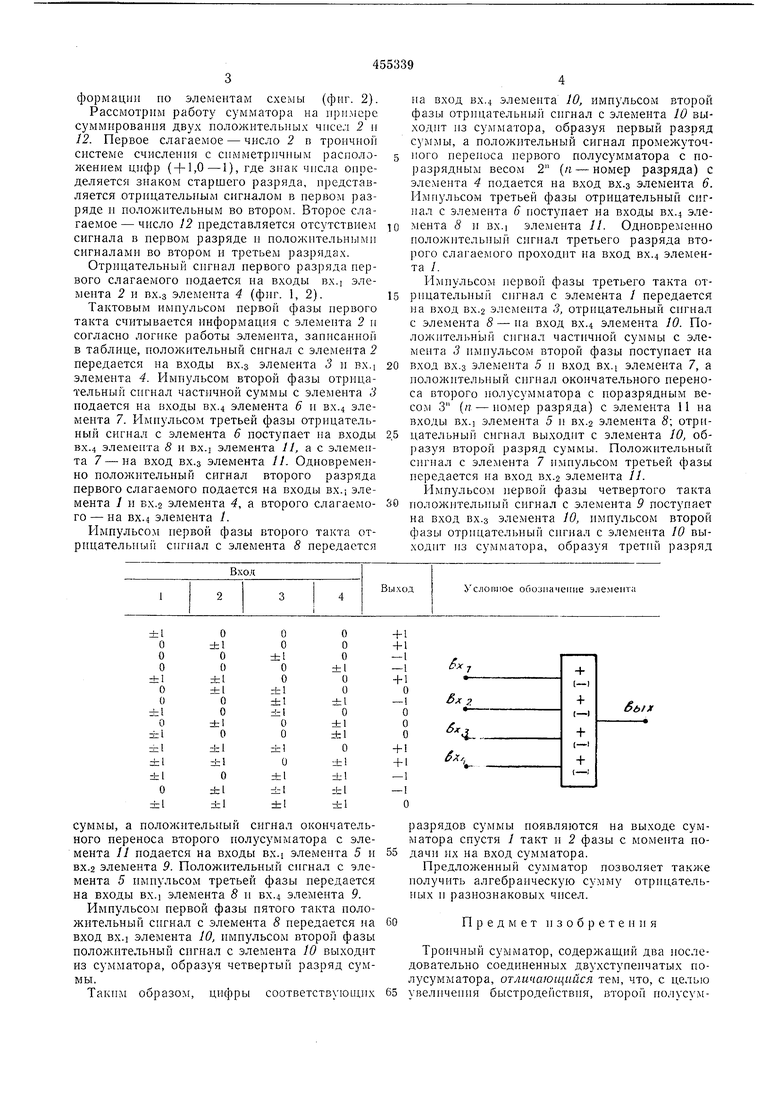

формации по элементам схемы (фиг. 2).

Рассмотрим работу сумматора на примере суммирования двух положительных чисел 2 п 12. Первое слагаемое - число 2 в троичной системе счисления с симметричным расиоложением цифр ( + 1,0-1), где зиак числа определяется знаком старшего разряда, представляется отрпцате.аьным сигналом в первом разряде и положительным во втором. Второе слагаемое- число 12 представляется отсутствием сигнала в первом разряде п положптельн111ми сигналами во втором п третьем разрядах.

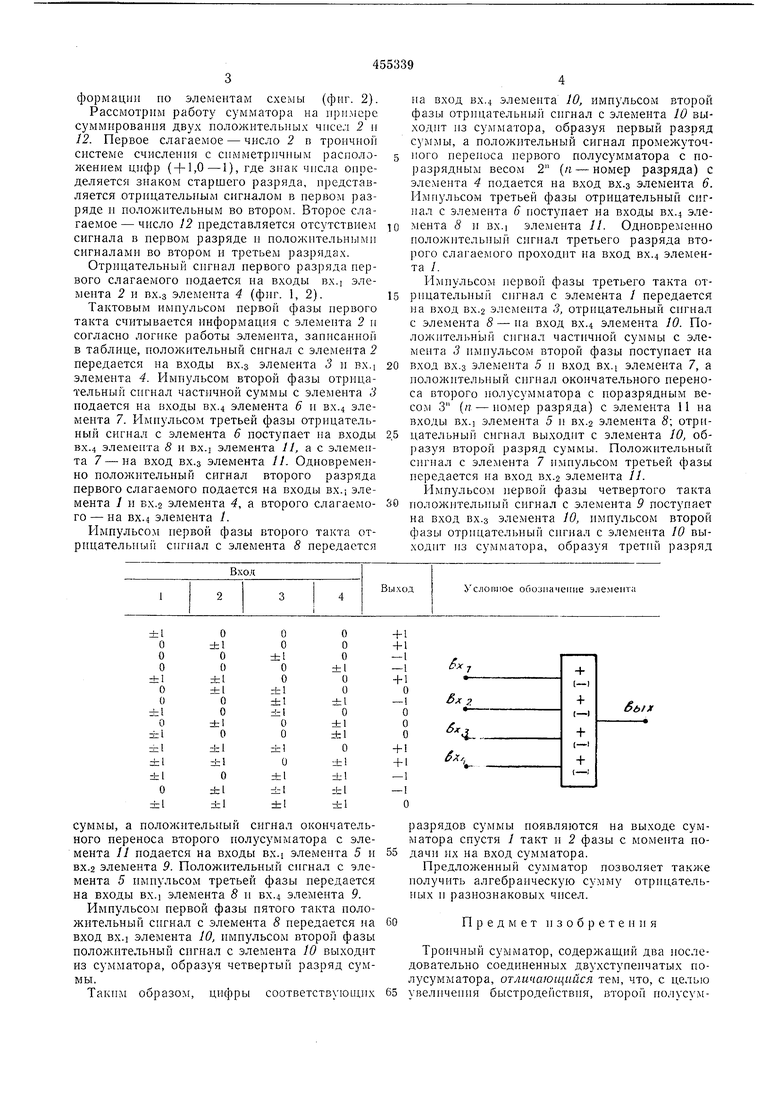

Отрицательный спгпал первого разряда первого слагаемого подается на входы BX.I элемента 2 и вх.з элемента 4 (фиг. 1,2).

Тактовым импульсом первой фазы первого такта считывается информация с элемепта 2 и согласно логике работы элемента, записанной в таблице, положительный сигнал с элемента 2 передается на входы вх.з элемента 3 и BX.I элемента 4. Импульсом второй фазы отрицательный сигнал частичной суммы с элемепта 3 подается на входы вх.4 элемента 6 п вх.4 элемента 7. Импульсом третьей фазы отрицательный сигнал с элемента 6 поступает на входы вх.4 элемента 8 и вх. элемента J1, а с элемента 7- на вход вх.з элемента 1L Одновременно положительный спгнал второго разряда первого слагаемого подается на входы вх.-, элемента 1 и ВХ.2 элемента 4, а второго слагаемого - на вх.4 элемента 1.

Импульсом первой фазы второго такта отрицательньп сигнал с элемента 8 передается

иа вход вх.4 элемеита 10, импульсом второй фазы отрицательный сигнал с элемента 10 выходит из сумматора, образуя первый разряд суммы, а положительный спгнал промежуточного переноса первого полусумматора с поразрядным весом 2 (п - номер разряда) с элемента 4 подается на вход вх.з элемента 6. Имиульсом третьей фазы отрицательный сигнал с элемента 6 поступает на входы вх.4 элемента 8 и ВХ.1 элемента 11. Одновременно положптельный сигнал третьего разряда второго слагаемого проходпт на вход вх.4 элемента /.

Импульсом первой фазы третьего такта отрицательиый спгнал с элемента / передается на вход ВХ.2 элемепта 3, отрицательный спгнал с элемента 8 - на вход вх.4 элемента 10. Положнтельный сигнал частичной суммы с элемента 3 импульсом второй фазы поступает на вход вх.з элемента 5 п вход BX.I элемента 7, а положительпый сигпал окончательного переноса второго полусумматора с поразрядным весом 3 (п - номер разряда) с элемента 11 на входы вх. элемента 5 и вх.2 элемента 8; отрицательный сигнал выходнт с элемента 10, образуя второй разряд суммы. Положительный сигнал с элемента 7 нмпульсом третьей фазы передается на вход вх.г элемеита 11.

Импульсом первой фазы четвертого такта положительный сигнал с элемента 9 поступает на вход вх.з элемента 10, импульсом второй фазы отрицател1 ный снгнал с элемента 10 выходнт из сумматора, образуя третий разряд

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный сумматор | 1976 |

|

SU638960A1 |

| Двоичный сумматор | 1980 |

|

SU918945A1 |

| Двоичный сумматор | 1981 |

|

SU1001088A1 |

| Десятичный сумматор | 1973 |

|

SU491947A1 |

| Цифровой преобразователь координат | 1980 |

|

SU943715A1 |

| Устройство для умножения | 1987 |

|

SU1411733A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Двоичный сумматор | 1980 |

|

SU857976A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

суммы, а положительный сигнал окончательного переноса второго полусумматора с элемента 11 подается на входы BX.I элемента 5 и ВХ.2 элемента 9. Положительный сигнал с элемента 5 пмпульсом третьей фазы передается на входы ВХ.1 элемента 8 п вх.4 элемента 9.

Импульсом первой фазы пятого такта положительный сигнал с элемента 8 передается на вход вх. элемента 10, пмпульсом второй фазы положптельный спгпал с элемента 10 выходит пз сумматора, образуя четвертый разряд суммы.

Таким образом, цифры соответствующих

разрядов суммы появляются на вы.ходе сумматора спустя 1 такт н 2 фазы с момента подачи их на вход су.мматора.

Предложенный сумматор позволяет также получить алгебранческую сумму отр1П1,ательных н разиознаковых чисел.

Предмет п з о б р е т е п н я

Троичный сумматор, содержащий два последовательно соединенных двухступенчатых полусумматора, отличающийся тем, что, с целью увелпчепия быстродействия, второй полусумматор содержит дополнительный логический троичный элемент, первый и второй входы которого соединены соответственно с первым и четвертым выходами первой ступени второго полусумматора, второй п третий входы объединены и через линию задержки соединены с выходом суммы первого полусумматора, а выход соединен с дополнительным входом второго полусумматора.

Риг 1

%ja, 9аза

i

O30j

n

15

7

2

/4

75

5

6 1

n

16

j Ннпульсы fnpe)((pa3JiOiO ,fa пито/уиЯ

Jaf/uc6 A Cvumbf a/ii e„ 7

Jonuct,„- - Счнглбгбание„-

(Риг.2

C4i/m6iSoHue:,0

Авторы

Даты

1974-12-30—Публикация

1972-06-06—Подача