1

Изобретение относится к технике передачи двоичной информации и может использоваться при конструировании устройств сопряжения независимых источников двоичной информации с групповым трактом канала связи.

Известно устройство для квазисинхронного ввода двоичных сигналов, содержащее на входе блок формирования тактовых частот и регенерации, один выход которого соединен с информационным входом блока памяти, а два других выхода через распределители записи и считывания подключены к входам управления блока памяти и к входам блока сравнения скоростей соответственно.

Однако из-за того, что в импульсный сигнал источника информации на передаче вводятся дополнительные служебные сигналы, что требует увеличения скорости передачи в канале связи по сравнению со скоростью источника информации, не вся пропускная способность канала связи используется для передачи информации.

С целью повышения пропускной способности канала связи в предлагаемое устройство введены элементы «ИЛИ и анализатор отсутствия сигнала, вход которого соединен с входом блока формирования тактовых частот и регенерации, а выход через элементы «ИЛИ подключен к входам установки начальной фазы распределителей записи и считывания,

причем к вторым входам элементов «ИЛИ подключены соответствующие выходы блока сравнения скоростей.

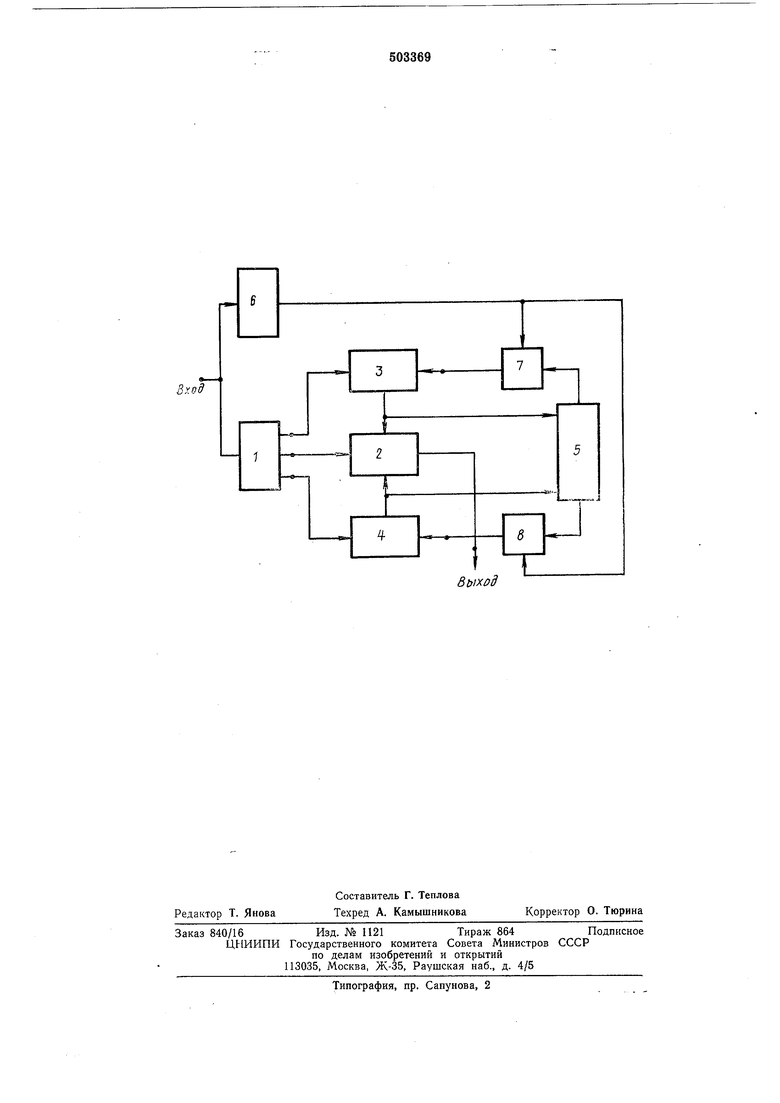

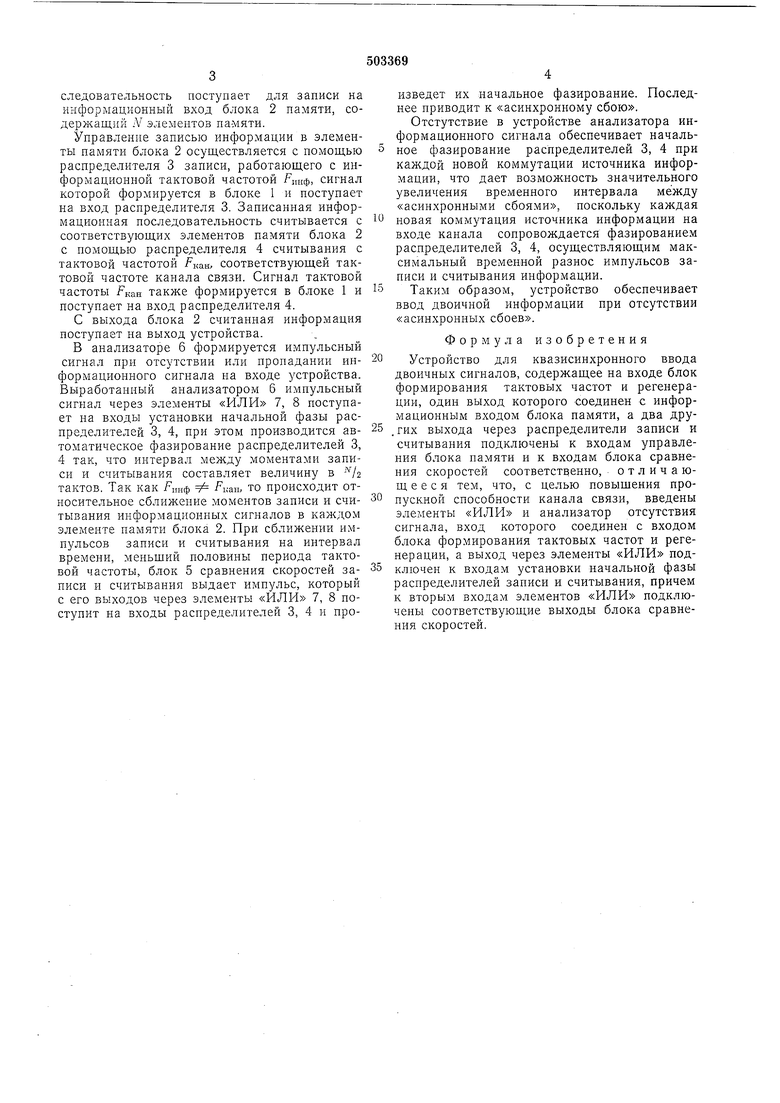

На чертеже приведена структурная электрическая схема устройства.

Устройство для квазисинхронного ввода двоичных сигналов содержит блок 1 формирования тактовых частот и регенерации, один выход которого соединен с информационным входом блока 2 памяти, а два других выхода через распределитель 3 записи и распределитель 4 считывания подключены одновременно к входам управления блока 2 памяти и к входам блока 5 сравнения скоростей соответственно, анализатор 6 отсутствия сигнала, вход которого соединен с входом блока 1, являющимся входом устройства, а выход через элементы «ИЛИ 7, 8 подключен к входам установки начальной фазы распределителей 3, 4, причем к вторым входам элементов «ИЛИ 7, 8 подключены соответствующие выходы блока 5 сравнения скростей, выход блока 2 памяти является выходом устройства.

Устройство работает следующим образом.

Информационный двоичный сигнал с входа устройства поступает на блок 1 формирования тактовых частот и регенерации и анализатор 6 отсутствия сигнала. В блоке 1 регенерируются двоичные информационные сигналы; регенерированная информационная последовательность поступает для записи на информационный вход блока 2 памяти, содержащий N элемептоз памяти.

Управление записью информации в элементы памяти блока 2 осуществляется с помощью распределителя 3 записи, работающего с информационной тактовой частотой Рипф, сигнал которой формируется в блоке 1 и поступает на вход распределителя 3. Записанная информационная последовательность считывается с соответствующих элементов памяти блока 2 с помощью распределителя 4 считывания с тактовой частотой /каш соответствующей тактовой частоте канала связи. Сигнал тактовой частоты Ркан также формируется в блоке 1 и поступает на вход распределителя 4.

С выхода блока 2 считанная информация поступает на выход устройства.

В анализаторе 6 формируется импульсный сигнал при отсутствии или пропадании информационного сигнала на входе устройства. Выработанный анализатором 6 импульсный сигнал через элементы «ИЛИ 7, 8 поступает на входы установки начальной фазы распределителей 3, 4, ири этом производится автоматическое фазирование распределителей 3, 4 так, что интервал между моментами записи и считывания составляет величину в тактов. Так как .Рциф Л;а1ь то происходит относительное сближение моментов записи и считывания информационных сигналов в каждом элементе памяти блока 2. При сближении импульсов записи и считывания на интервал времени, меньщий половины периода тактовой частоты, блок 5 сравнения скоростей записи и считывания выдает импульс, который с его выходов через элементы «ИЛИ 7, 8 поступит на входы распределителей 3, 4 и произведет их начальное фазирование. Последнее приводит к «асинхронному сбою.

Отстутствие в устройстве анализатора информационного сигнала обеспечивает начальное фазирование распределителей 3, 4 при каждой новой коммутации источника информации, что дает возможность значительного увеличения временного интервала между «асинхронными сбоями, поскольку каждая

новая коммутация источника информации на входе канала сопровождается фазированием распределителей 3, 4, осуществляющим максимальный временной разнос импульсов записи и считывания информации.

Таким образом, устройство обеспечивает ввод двоичной информации при отсутствии «асинхронных сбоев.

Формула изобретения

Устройство для квазисинхронного ввода двоичных сигналов, содержащее на входе блок формирования тактовых частот и регенерации, один выход которого соединен с информационным входом блока памяти, а два других выхода через распределители записи и считывания подключены к входам управления блока памяти и к входам блока сравнения скоростей соответственно, отличающееся тем, что, с целью повыщения пропускной способности канала связи, введены элементы «ИЛИ и анализатор отсутствия сигнала, вход которого соединен с входом блока формирования тактовых частот и регенерации, а выход через элементы «ИЛИ подключен к входам установки начальной фазы распределителей записи и считывания, причем к вторым входам элементов «ИЛИ подключены соответствующие выходы блока сравнения скоростей.

Ёу.од

Въход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переприема двоичных сигналов | 1977 |

|

SU640432A1 |

| Устройство для ввода информации | 1982 |

|

SU1084775A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1986 |

|

SU1401629A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1979 |

|

SU860326A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1974 |

|

SU510792A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| Устройство асинхронного ввода-вывода синхронной информации | 1982 |

|

SU1053307A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

| Устройство для ввода двоичной информации | 1980 |

|

SU924885A1 |

Авторы

Даты

1976-02-15—Публикация

1973-07-30—Подача