I

Изобретение относится к области вь числительной техники и может быть иопользованО| как цифровой генератор значений функции 2 и для построения специализированных и универсальных быстродействующих вычислительных устройств,

Известно цифровое устройство для П тенцирования FlT, содержащее генератор, регистр сдвига, счетчик, триггер.

Недостатком известного устройства является малое быстродействие и низкая точность.

Наиболее близким по сущности техническим решением к изобретению является устройст во для потенцирования f2, содержащее регистр аргумента, два памяти, узел сдвига, триггер, первый коммутатор, блок управления, первый которого соединен с первым входом первого коммутатора, выходы блоков памяти соединены с первым и вторым входами узла сдвига, первый выход регистра аргумента соединен со входом второго блока памяти

Недостатком известного устройства является недостаточные быстродействие и точность.

Целью изобретения является повьпие- ние быстродействия и точности устройс1 ва для потенцирования.

Поставленная цель достигается тем, что в устройство дополнительно введены буферньш регистр, регистр результата,, сумматор и два коммутатора, причем, второй выход регистра аргумента соед& нен с первыми вюдами второго и третьэ го коммутаторов, вторые входы которых соединены соответственно со вторым н первым выходами блока управления, выходы первого и второго коммутаторов соединены ео входами сумматора, выход .которого соединен с входами регистра результата, триггера в третьим входо третьего коммутатора, выход которого через последовательно соединенные первый блок памяти и буферный регистр соединен с третьим входом второго коммутатора, второй в третий входы первого коммутатора соединены с выходами второго блока памяти к узла сдвига, третий вход которого соединен с выходом триггера.

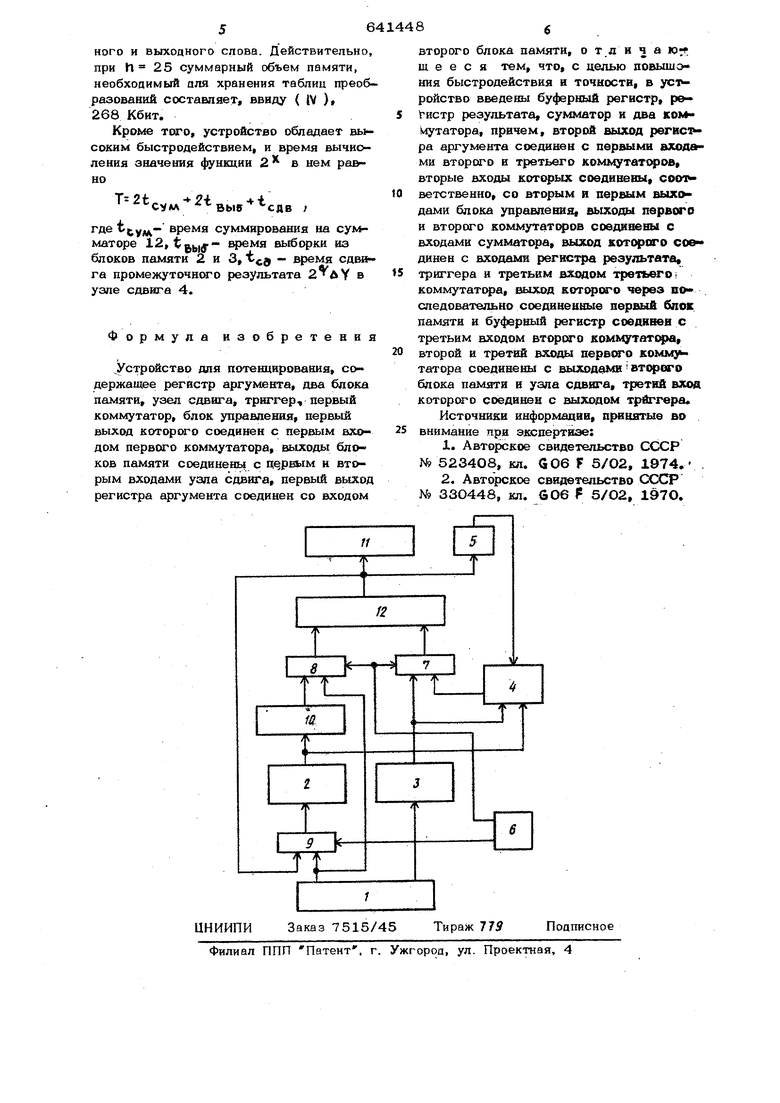

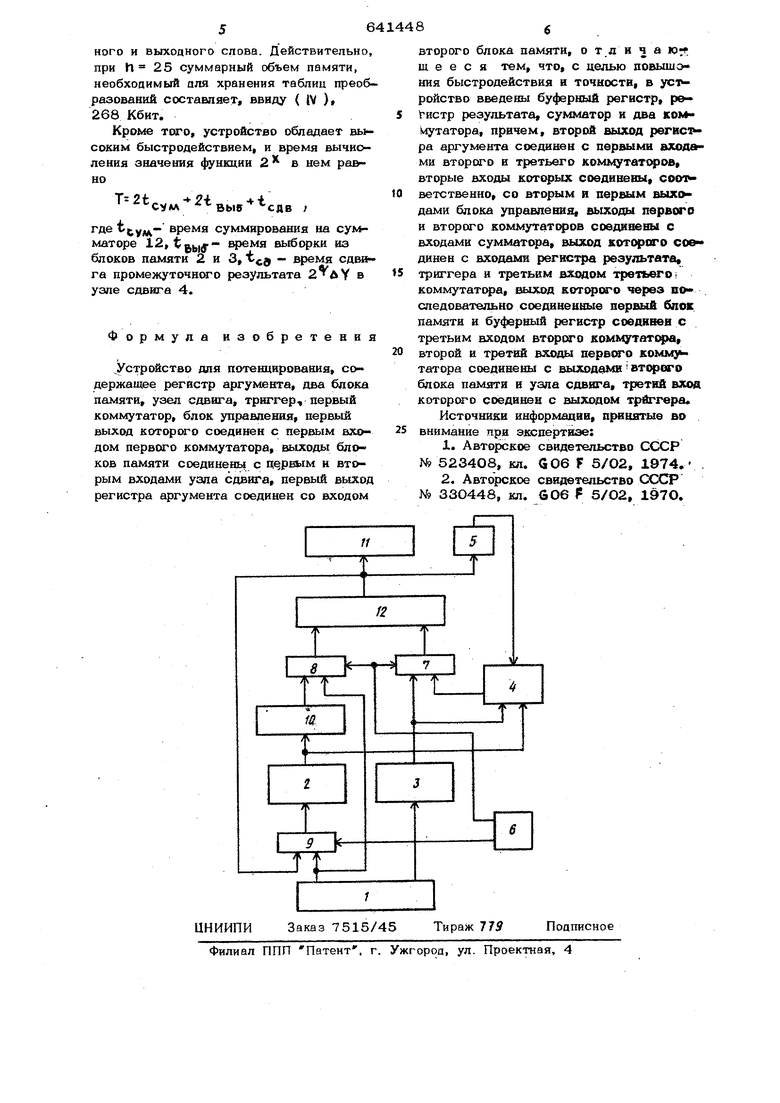

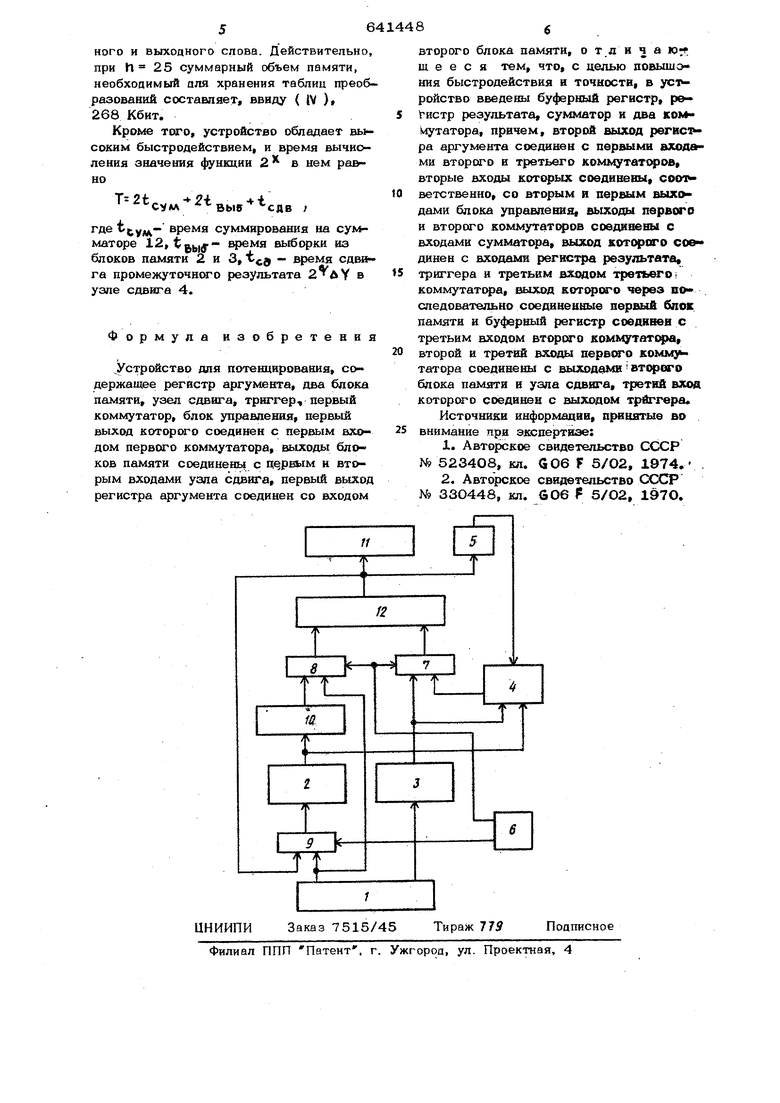

Блок-схема устройства представлена на чертеже.

Устройство содержит регистр аргумента 1, блоки памяти 2, узел CABH га 4 триггер 5, блок управления 6, коммутаторы 7, 8, 9, буерный регистр Ю, регистр результата 11, сумматор 12. Выход сумматора 12 подключен к входам регистрарезультата 11, триггера 5 и третьему входу третьего комму татора 9, выход которого через последовательно соединенные первый блок памяти 2 и буферный регистр 10 полключен к третьему входу второго комму-татора 8. Второй и третий входа перво го коммутатора 7 соединены с выходами второго блока памяти 3 и узла сдв№ га 4, третий вход которого подключен к выходу триггера 5,

Коммутаторы состоят, например, из двух групп схем И и группы схем ИЛИ и управляются от блока управления 6, подключающего к| выходам крммутатрра ту или иную группу входов.

Вычислительные функции 2 от аргумента X (О X 1) производится в устройстве на основе следующих соорношений.

Пусть XQ- число, образованное стар щими разрядами аргумента, дХ - чиоrto, образованное младшими разрядами аргумента,

Vo 2«(I)

Тогда приращение ДУ, которое необходимо добавить к значению YO чтобы получить точное значение функции 2 определяется выражением

, X Хо

(,

Откуда, логарифмируя по основанию 2, nt лучаем...А

eog-2AV-Ao- eogr C2 --f). (11

Кроме того, имеем

) ..

Устройство работает следующим образом.

Значение аргумента X хранится в регистре 1. В первом такте работы yci ройства; значение Х регистра 1 через коммутатор 9 поступает на блок 2, хранящий таблицу преобразований (1), и с его выхода считывается значение о i которое запоминается на буферном регистре 10. Одновременно (в том же такте) на блок 3 с регистра 1 поступает; значение йХ и с блока 3 снимаерЛ V

ся значение функции 2 о,,(2 -1). Во втором такте работы устройства значение регистра 1, через коммутатор 8, и дробная часть значения Z t поступающая с блика 3 через коммутатор 7, складываются на сумматоре 12, образуя согласно формуле ( f/ ) значение мантиссы Ой-ДУ, дробная часть которой передается через коммутатор 9 на блок 2, где преобразуясь по формуле (1), образует, ввиду равенства ( 1И ), на выходе этого блока значение 2.дХ . Здесь - С ( 9 О) - значение характеристики 6 о О дУ определяемое узлом 4 как су мм;а значения триггера .5 и значения характеристики числа 2 2og2(2 -1), снимаемого с блока 3,

В последнем такте полученное значение 2 Л Y поступает на узел 4, который сдвигает это число на ф разрядов вправо, образуя значение Д У . Это значение дУ через коммутатор 7 поступает на сумматор 12 где складывается с поступающим одновременно через коммутатор 8 значением Уо, хранящимся до тех пор на буферном регистре 10, Результат, равный искомому значению Ч 2 , запоминается на регистре 9, Таким образом, устройство преобразует значение аргумента X (О X 1) в значение функции 2 .

Расчеты , проведённые для определения суммарного объема используемых в устройстве блоков 2 и 3 дают следук щую величину:

п (n-K ieo9f2Cn-K- -i)

(Ш

32ii±r

где К разрядов входного и выходнсхго слова устройства, а функция f (х) J хС представляет собой наименьшее целое число, не меньщее X . Данные расчета суммарн1 го объема памяти устройства указывают, что этот объем меньше, чем у известных устройств.

Изобретение позволяет находить значение функции У 2 с большей точностью, чем в прототипе, причем эта точность определяется лишь технологическими ограничениями на емкости блоков памяти. Например, при условии, что сум марный объем блоков памяти не должен превосходить ЗОО Кбит, возможно пост роить устройство на- 25 разрядов вход

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для потенцирования массивов двоичных чисел | 1982 |

|

SU1043646A1 |

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Цифровое устройство для воспроизве-дЕНия фуНКций | 1979 |

|

SU809126A1 |

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU957209A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Функциональный преобразователь | 1991 |

|

SU1807498A1 |

Авторы

Даты

1979-01-05—Публикация

1976-09-13—Подача