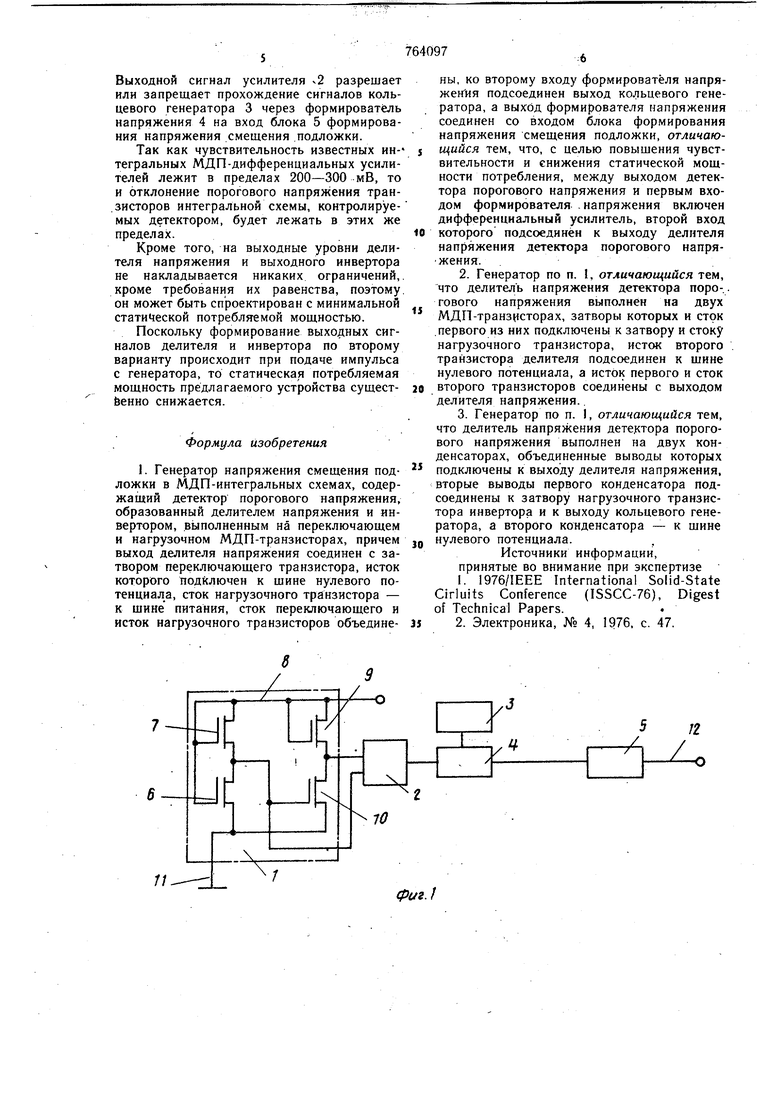

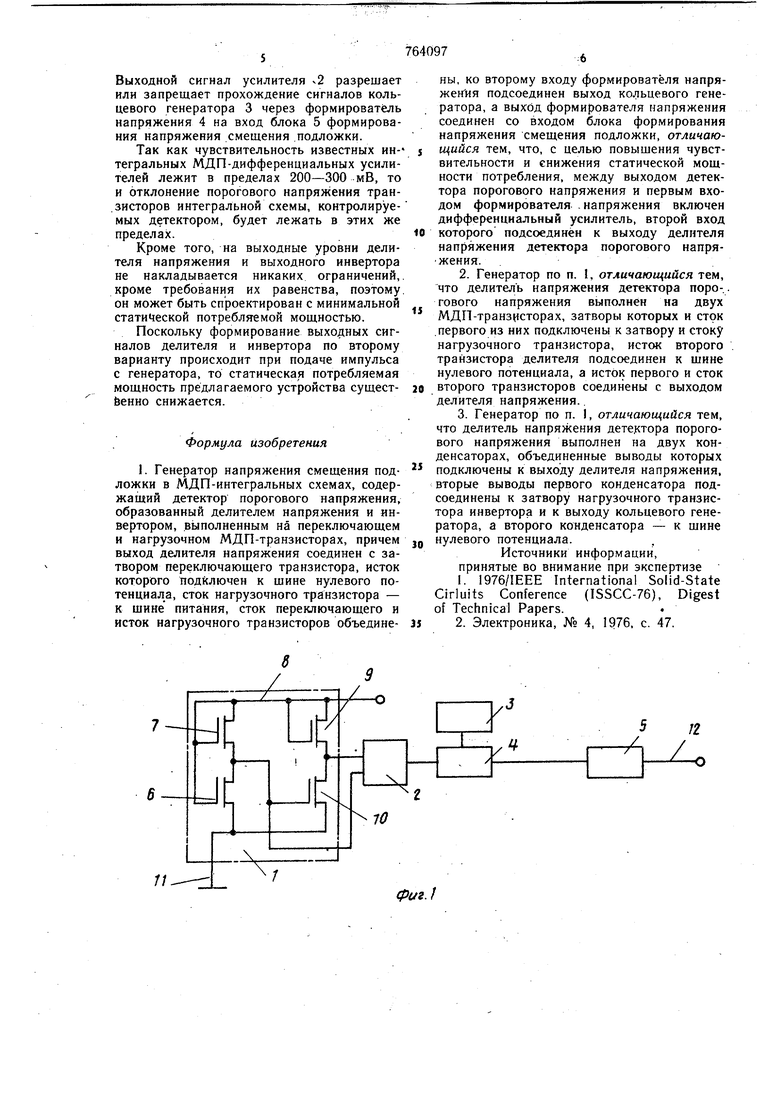

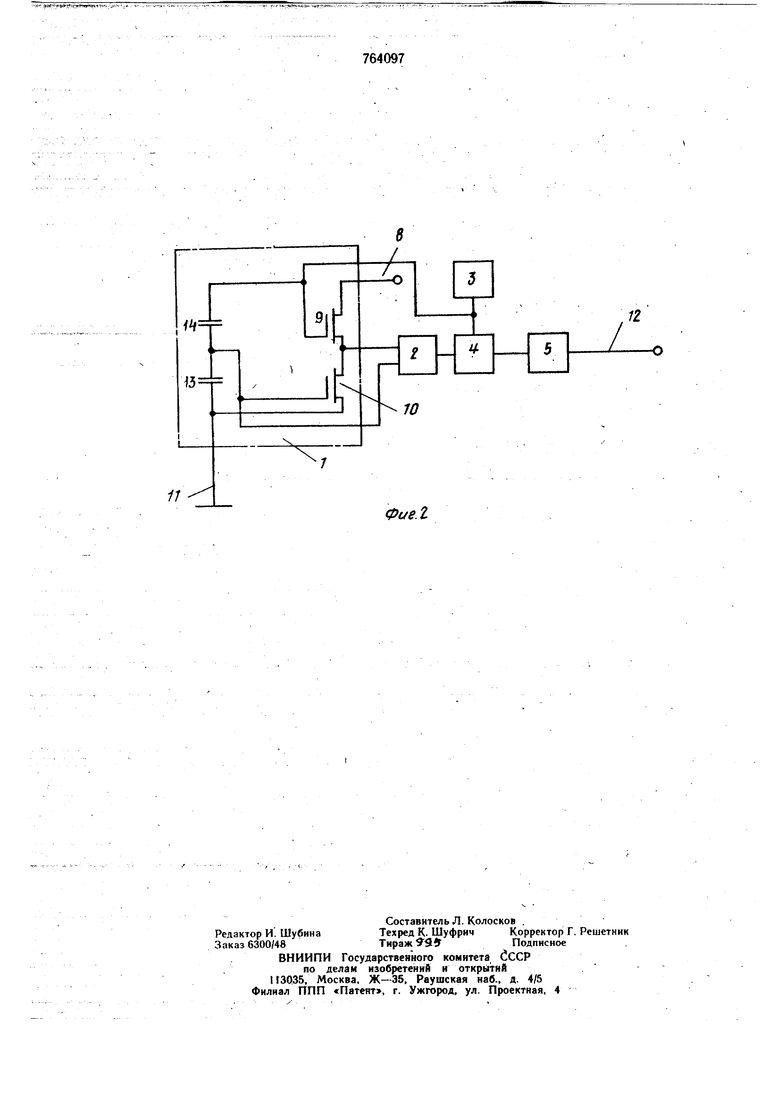

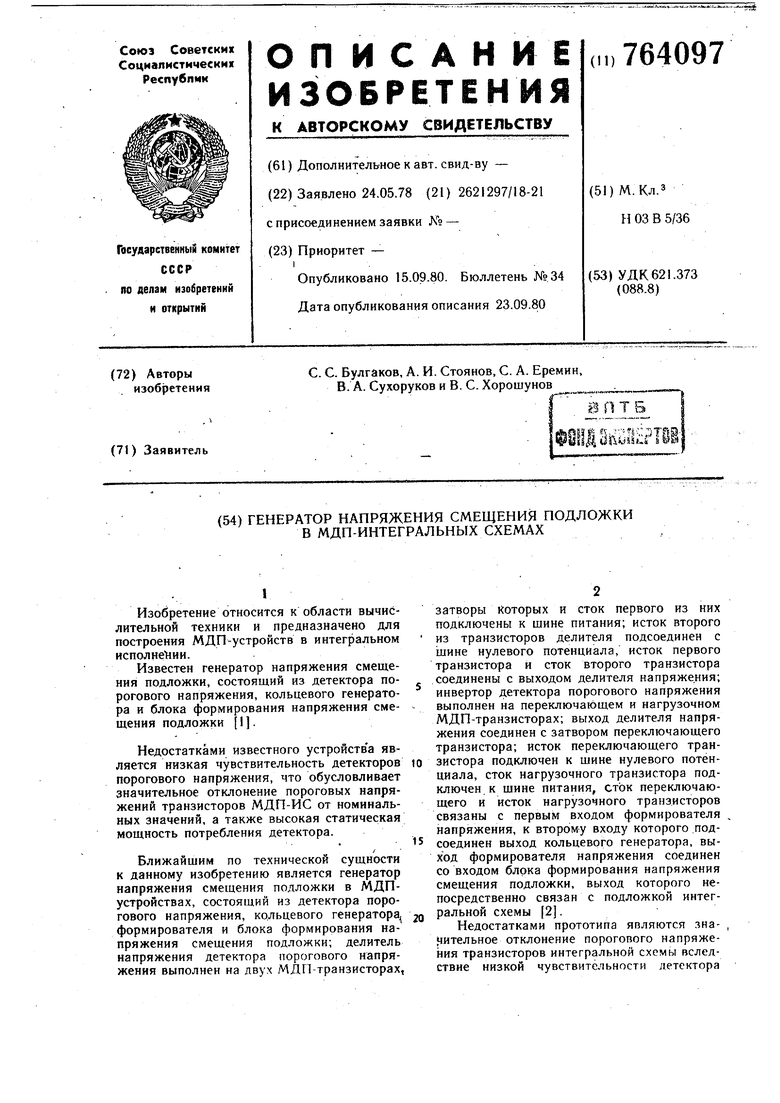

Изобретение относится к области вычислительной техники и предназначено для построения МДП-устройств в интегральном исполнении. Известен генератор напряжения смещения подложки, состоящий из детектора порогового напряжения, кольцевого генератора и блока формирования напряжения смещения подложки 1. Недостатками известного устройства является низкая чувствительность детекторов порогового напряжения, что обусловливает значительное отклонение пороговых напряжений транзисторов МДП-ИС от номинальных значений, а также высокая статическая мощность потребления детектора. Ближайшим по технической сущности к данному изобретению является генератор напряжения смещения подложки в МДПустройствах, состоящий из детектора порогового напряжения, кольцевого генератора, формирователя и блока формирования напряжения смещения подложки; делитель напряжения детектора порогового напряжения выполнен на двух МДП-транзисторах, затворы которых и сток первого из них подключены к щине питания; исток второго из транзисторов делителя подсоединен с шине нулевого потенциала, исток первого транзистора и сток второго транзистора соединены с выходом делителя напряжения; инвертор детектора порогового напряжения выполнен на переключающем и нагрузочном МДП-транзисторах; выход делителя напряжения соединен с затвором переключающего транзистора; исток переключающего транзистора подключен к щине нулевого потенциала, сток нагрузочного транзистора подключен к щине питания, сток переключающего и исток нагрузочного транзисторов связаны с первым входом формирователя напряжения, к второму входу которого подсоединен выход кольцевого генератора, выход формирователя напряжения соединен со входом блока формирования напряжения смещения подложки, выход которого непосредственно связан с подложкой интегральной схемы 2. Недостатками прототипа являются зна- , Нительное отклонение порогового напряжения транзисторов интегральной схемы вследствие низкой чувствительности детектора И большая статическая моишость потребления детектора. Действительно, выходной элемент детектора состоит нз инвертора, чувствительность которого определяется крутизной передаточной характеристики и при выборе крутизны транзисторов, достаточно приемлемой с топологической точки зрения, не обеспечивается высокая чувствительность выходного ивертора. Кроме того, делитель напряжения и выходной инвертор построены по статическому принципу, что вызывает значительное потребление мощности. Целью изобретения является повышение чувствительности и уменьшение статической мощности потребления устройства. Цель достигается тем, что в генератор напряжения смещения подложки в МДП-интегральных схемах, который содержит детектор порогового напряжения, образованный делителем напряжения и инвертором, выполненным на переключающем и нагрузочном МДП-транзисторах, причем выход делителя напряжения соединен с затвором переключающего транзистора, исток которого подключен к шине нулевого потенциала, сток нагрузочного транзистора - к шине питания, сток переключающего и исток нагрузочного транзисторов объединены, ко второму входу формирователя напряжения подсоединен выход кольцевого генератора, а выход формирователя напряжения-соедиг нен со входом блока формирования напряжения смещения подложки, между выходом детектора порогового напряжения и первым входом формирователя напряжения включен дифференциальный усилитель, второй вход которого подсоединен к выходу делителя напряжения детектора порогового напряжения. Делитель напряжения в первом варианте изобретения выполнен на двух МДП-транзисторах, затворы которых и сток первого из них подключены к затвору и стоку нагрузочного транзистора, исток второго транзистора делителя подсоединен к шине нуле вого потенциала, а исток первого и сток второго транзисторов соединены с выходом делителя напряжения. Во втором варианте выполнения устройства делитель напряжения выполнен на двух конденсаторах, объединенные выводы которых подключены к выходу делителя напряжения; вторые выводы первого конденсатора подсоединены к затвору нагрузочного транзистора инвертора и к выходу кольцевого генератора, а второго конденсатора - к шине нулевого потенциала. На фиг. I представлен генератор напряжения, в котором делитель напряжения детектора порогового напряжения выполнен на двух МДП-транзисторах; на фиг. 2 - то же, делитель напряжения выполнен на двух конденсаторах. Генератор напряжения состоит из детектора порогового напряжения 1, диффер)енциального усилителя 2, кольцевого генератора 3, формирователя напряжения 4 и блока 5 формирования напряжения смещения подложки. В первом варианте выполнения устройства делитель напряжения образован МДП-транзисторами 6 и 7, затворы которых, а также сток транзистора 7 подключены к шине питания 8, к которой также подсоединены затвор и сток нагрузочного МДП-транзистора 9 выходного инвертора. Исток транзистора 9 объединен со стоком переключающего МДП-транзистора 10 и подсоединен к первому выходу детектора порогового напряжения 1, который соединен с первым входом дифференциального усилителя 2. Истоки транзисторов 6 и 10 подсоединены к шине нулевого потенциала 11. Сток транзистора 6 объединен с истоком транзистора 7, с затвором транзистора 10 и со вторым входом дифференциального усилителя 2. Выход дифференциал1 ного усилителя 2 подключен к первому входу формирователя напряжения 4, ко второму входу которого подсоединен выход кольцевого генератора 3. Выход формирователя напряжения 4 соединен со входом блока 5, выход 12 которого непосредственно связан с подложкой интегральной шины. В устройстве по второму варианту делитель напряжения образован конденсаторами 13 и 14, средние выводы которых соединены с затвором транзистора 10 и со вторым входам дифференциального усилителя 2: Второй вывод конденсатора 12 соединен с истоком транзистора 10 и с шиной нулевого потенциала 11. Второй ,вывод конденсатора 13 подключен к затвору транзистора 9 и к выходу кольцевого генератора 3. В остальном конструкция генератора по этому варианту та же, что и по первому варианту. Предлагаемый генератор напряжения работает следующим образом. Делитель напряжения формирует на затворе переключающего транзистора 10 выходного инвертора некоторый опорный уровень напряжения, который в общем случае не связан с номинальным пороговым напряжением. При этом соотношение крутизны транзисторов 9 и 10 выходного инвертора выбирается таким, что на выходе инвертора (стока транзистора 10) формируется уровень напряжения, близкий к напряжению на затворе транзистора 10. Если значение порогового напряжения выше или ниже номинального, то на входах дифференциального усилителя 2 формируется разность напряжений, фиксируемая усилителем. При этом на выходе усилителя устанавливается уровень напряжения в соответствии со знаком приращения напряжения на выходе детектор 1 (выходное напряжение делителя напряжения не зависит от значения порогового напряжения транзисторов 6 и 7).

Выходной сигнал усилителя 2 разрешает или запрещает прохождение сигналов кольцевого генератора 3 через формирователь напряжения 4 на вход блока 5 формирования напряжения смещения .подложки.

Так как чувствительность известных интегральных МДП-дифференциальных усилителей лежит в пределах 200-300 мВ, то и отклонение порогового напряжения транзисторов интегральной схемы, контролируемых детектором, будет лежать в этих же пределах.

Кроме того, на выходные уровни делителя напряжения и выходного инвертора не накладывается никаких ограничений,, кроме требования их равенства, поэтому, он может быть спроектирован с минимальной статической потребляемой мощностью.

Поскольку формирование выходных сигналов делителя и инвертора по второму варианту происходит при подаче импульса с генератора, то статическая потребляемая мощность предлагаемого устройства существенно снижается.

Формула изобретения

1. Генератор напряжения смещения подложки в МДП-интегральных схемах, содержащий детектор порогового напряжения, образованный делителем напряжения и инвертором, выполненным на переключающем и нагрузочном МДП-транзисторах, причем выход делителя напряжения соединен с затвором переключающего транзистора, исток которого подключен к шине нулевого потенциала, сток нагрузочного транзистора - к шине питания, сток переключающего и исток нагрузочного транзисторов объединены, ко второму входу формирователя напряжения подсоединен выход кольцевого генератора, а выход формирователя напряжения соединен со входом блока формирования напряжения смещения подложки, отличаюJ щийся тем, что, с целью повышения чувствительности и снижения статической мощности потребления, между выходом детектора порогового напряжения и первым входом формирователя . напряжения включен дифференциальный усилитель, второй вход

0 которого подсоединён к выходу делителя напряжения детектора порогового напряжения.

2.Генератор по п. 1, отличающийся тем, что делитель напряжения детектора поро-.. гового напряжения выполнен на двух

5 МДП-транзисторах, затворы которых и сток .первого из них подключены к затвору и стоку нагрузочного транзистора, исток второго транзистора делителя подсоединен к щине нулевого потенциала, а исток первого и сток

0 второго транзисторов соединены с выходом делителя напряжения..

3.Генератор по п. 1, отличающийся тем, что делитель напряжения детектора порогового напряжения выполнен на двух конденсаторах, объединенные выводы которых

5 подключены к выходу делителя напряжения, вторые выводы первого конденсатора подсоединены к затвору нагрузочного транзистора инвертора и к выходу кольцевого генератора, а второго конденсатора - к шине

Q нулевого потенциала.

Источники информации, принятые во внимание при экспертизе I. 1976/IEEE International Solid-State Cirluits Conference (ISSCC-76), Digest of Technical Papers. j 2. Электроника, № 4, 1976, с. 47.

0ue.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Дешифратор адреса | 1978 |

|

SU741470A1 |

| Управляемый инвертор на мдп-транзисторах | 1976 |

|

SU641655A1 |

| Инвертор на мдп-транзисторах | 1976 |

|

SU646441A1 |

| Логический элемент или-не- на мдптранзисторах | 1977 |

|

SU692089A1 |

| Формирователь сигнала напряжения смещения подложки для интегральных схем | 1983 |

|

SU1149311A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| Матричный накопитель для полупроводникового запоминающего устройства | 1978 |

|

SU729636A1 |

| Динамический инвертор на МДП-транзисторах | 1982 |

|

SU1080210A1 |

Авторы

Даты

1980-09-15—Публикация

1978-05-24—Подача