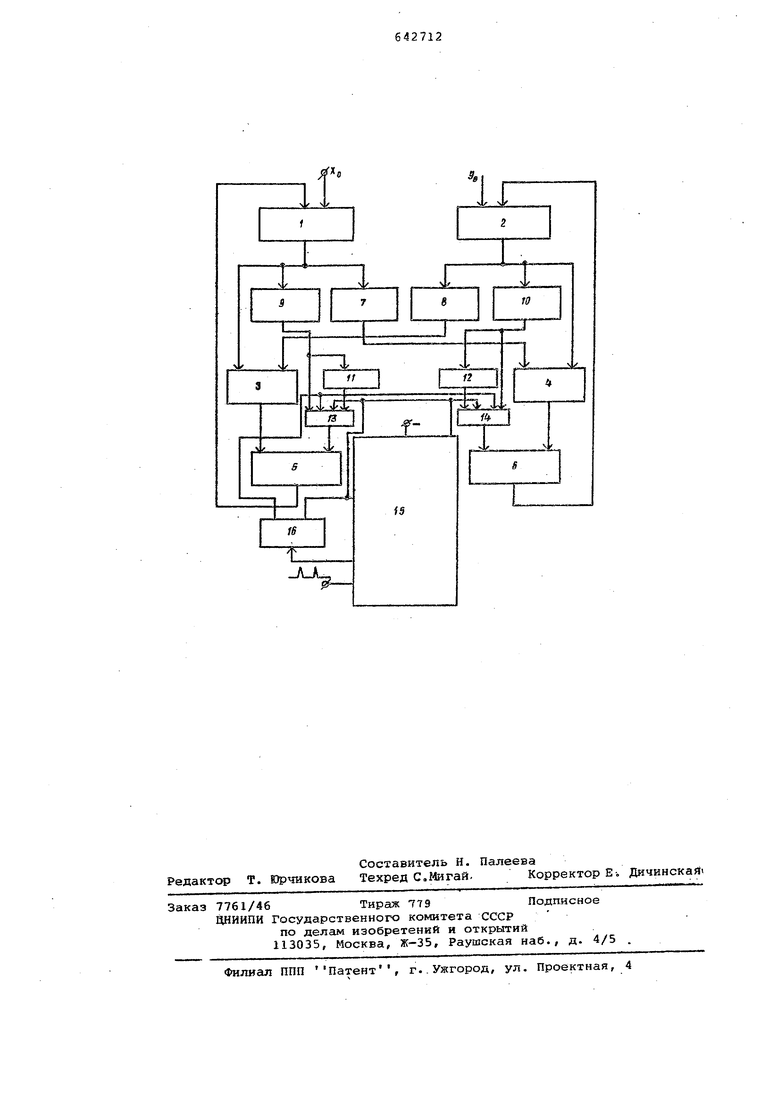

Изобретение относится к области цифровой вычислительной техники. Оно может быть использовано при построении специализированных устройств и калькуляторов с расомренными вычислительными возможностям, реализую1цими алгоритм Cofdic или алгоритм Волдера. Известно устройство l , реализую щее Cofdie -алгоритм, содержащее сум маторы, блоки сдвига кодов, ПЗУ констант и блок управления. Недостатком устройства, является деформация длины вектора в процессе поворота. Наиболее близким по технической сущности к изобретению является цифро вой вычислитель координат вектора 2 содержащий блок управления и первый и второй регистры, выходы которых соединены соответственно с первыми входами первого и второго сумматоров при этом вторые входы последних подключены через первый и второй умножители соответственно к выходам второго и первого регистров. Недостатком этого вычислителя является его низкое быстродействие. Целью изобретения является повышение быстродействия вычислителя координат вектора. Поставленная цель достигается тем, что в вычислитель введены третий и четвертый умножители, третий и четвертый сумматоры, сдвигатели кодов, элементы И и дешифратор. Причем выходы первого и второго регистров подключены соответственно к входам третьего и четвертого умножителей, выходы которых подключены соответственно к первым входам первого и второго элементов И непосредственно и к вторым входам элементов И через соответствующий сдвигатель кодов, первые входы третьего и четвертого сумматоров соединены соответственно с выходами первого и второго сумматоров, вторые входы с выходаг.т первого и второго элементов И, а выходы - с входами первого и второго регистров, выход блока управления соединен с входом дешифратора, первый выход которого-соединен с третьими входами первого, и второго элементов И, а второй выход - с четвертыми входами первого и второго элементов И.. На чертеже представлена блок-схема вычислителя, который содержит регистры 1 и 2, сумматоры 3-6, умножители 710, сдвигатели 11 и 12, элементы И 13 и 14, блок 15 управления и дешиф ратор 16. Работа вычислителя происходит по тактам. В каждом такте блок управле устанавливает соответствующий такту сдвиг кодов в умножителях 7В умножителях 7 и 8 осуществляе умножение на коэффициенты tgrcC,- , в умножителях 9 и 10 осуществляетс умножение на коэффициенты . Сдвигатели 11 и 12 осуществляют фо 1212 рование кодов ytg a. и -|tga ,В зависимости от номера t шага дешифратор 16 управляет элементами И 13 и 14, реализуя i или 1/2 ( а,( - коэффициент, приним ющий в зависимости от i значение или 1). На выходах элементов И в зависимости от i формируются в об ратном коде значения поправоТс &x,-,A С помощью сумматоров 3-б с учетом поправок определяются значения коо динат в i -ом такте. В первом такте с(1/2 tg-aj 2- 2° , Деформация длины вектора после первого шага. vlf Jx-i/ Во втором такте 2, -I / г - гЧ Г-гЧ - , Деформация длины вектора после второго шага 1-2 if Kt-tg fta . {H-2 Kl-Z +2) В третьем такте 3, °f °i/2i a-x. 2 «si/.-Z-j/, Деформация длины вектора после третьего шага 5l -SbVS i )C з) -(1-«-2-)СИ-Г) В четвертом такте .«4, -4п,2-5-/ з -г Ч tg-0(02 Деформация длины вектора после четертого шага i-4 i-3-V ri 2 Kn- Xl-t|-a,) (l+-2-)()( ) ((l-2-r Аналогично производится коррекция искажений длины вектора при последуюих итерациях. Эффективность предложения заключается в повьЕиении быстродействия вычислителя. Выработка цифровых значений координат вектора при его повороте на произвольный угол в произодиться за f тактов, где П -разряд- ность угла Q . При этом отсутствует искажения длины вектора в процессе поворота. Формула Изобретения Цифровой вычислитель координат векгора, содер айщй блок управления, первый и второй регастры, выходы которых соединены соответственно с первы1 ли входами первого и второго сумматоров, вторые входы которых подключены через первый и второй умножители соответственно к выходам второго и первого регистров, :о т л и ч ающ и и с я тем, что, с целью повышения быстродействия, в него введены третий и четвертый умножители, тре-, тий и четвертый сумматоры, сдвигатели кодов, элементы И и дешифратор, причем выходы первого и второго регистров подключены соответственно к входам третьегои четвертого умножителей, выходы которых подключены соответственно к пepвыrvI входам первого и второго элементов И непосредственно и к вторым входам элементов И через соответствующий сдвигатель кодов, пер.вне входы третьего и четвертогосумматоров соединены соответственно с . выходами первого и второго сумматоров, вторые входы - с выходами первого, и второго элементов И, а выходы - с входами первого и второго регистров, выход блока упраалення соединен с входом дешифратора, первый выход которого соединен с.третьш и входами первого и-второго элементов И, а второй выход - с четвёртыми входами первого и второго элементов И. Источники информации, принятые во внимание при экспертизе 1.Байков В.Д., Смолов В,Б. Annaратурная реализация элементарных функций в ЦВМ, Л., 1975, с. 71, рис. За. 2.Патент Великобритании 1331410, кл. Q 4 А 18, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1166103A1 |

| Устройство для формирования изображения | 1987 |

|

SU1474633A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Цифровое устройство для преобразования координат | 1981 |

|

SU960808A1 |

| Устройство для вычисления синусно- косинусных функций | 1978 |

|

SU750495A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

Авторы

Даты

1979-01-15—Публикация

1977-07-27—Подача