1

Изобретение относигся к запоминающим устройствам.

Известно устройство для защиты памяти .

Однадо данное устройство содержит большое количество аппаратуры.

Наиболее близким к данному изобретению техническим решением является устройство для защиты памяти, содержащее блок оперативной памяти, первый регистр числа, первую, вторую и третью группы элементов И; регистр ключей защиты, вход которого является входом устройства по ключам защиты, а выход соединен с первыми входами элементов И первой группы, первый выход блока оперативной памяти соединен с первым входом первого регистра числа, первый выход которого соединен с первыми вдюдами элементов И второй группы, а второй выход - с первыми входами элементов И третьей группы, выход которой соединен с первым входом блока оперативной памяти 21.

Однако данное устройство обладает малым быстродействием и не позволяет производить защиту отдельных ячеек памяти или групп ячеек размерами, отличающихся от страницы или строки.

Цель устройства - повыщение гибкости защиты памяти и быстродействия.

Это достигается тем, что устройство содержит блок контроля информации, блок управления, второй регистр числа, вход которого соединен с первым выходом блока оперативной памяти, а выход со вторым входом блока оперативной памяти, вход блока контроля информации соединен с третьим выходом первого регистра числа, а выход - с первым входом блока управления, первый, второй и третий выходы которого соединены со вторыми входами элементов И. соответственно второй, третьей и первой групп, выход элементов И первой группы соединен со вторым входом первого регистра числа, выходы элементов И второй группы являются информационным

выходом устройства, третий вход первого регистра числа является информационным входом устройства, четвертый выход блока управления является управляюшим выходом устройства.

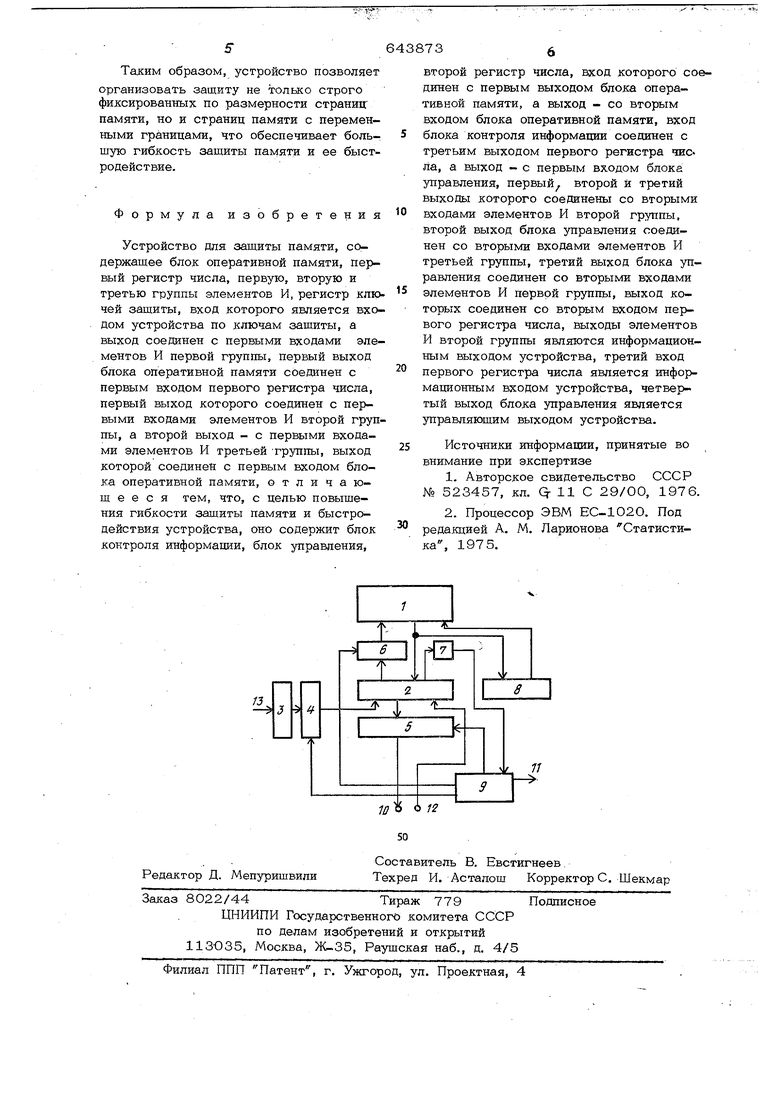

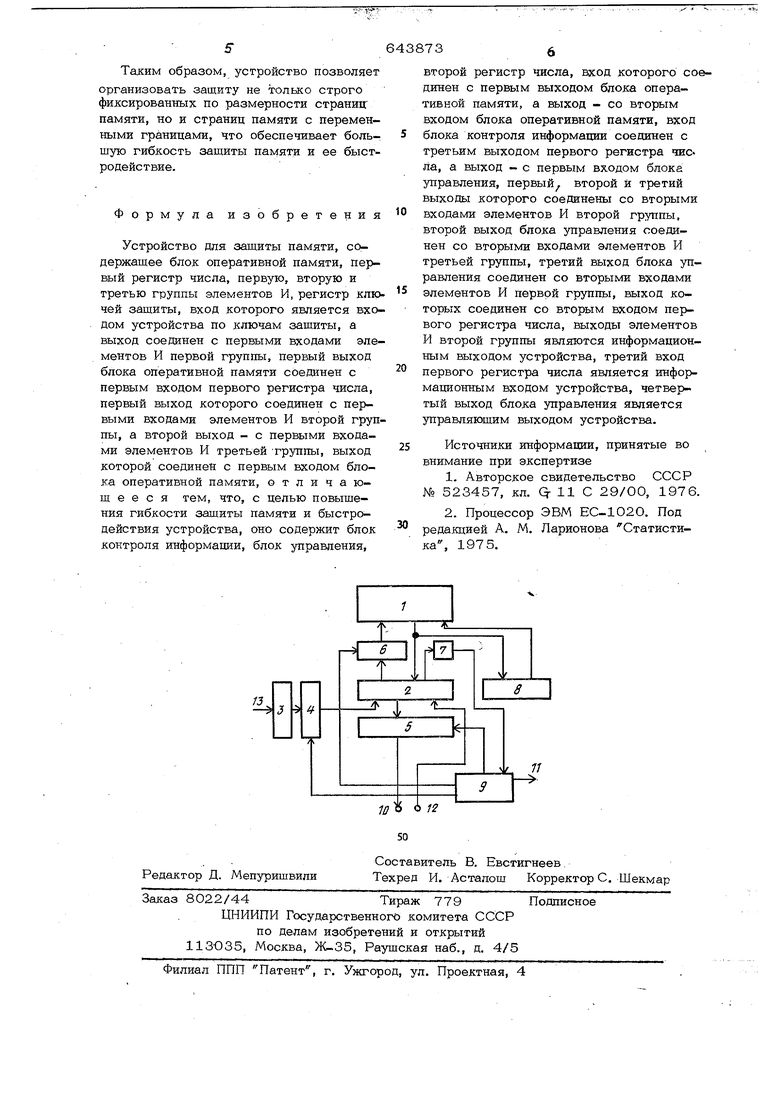

На чертеже представлена блок-схема устройства для зажиты памяти.

Устройство содержит блок 1 оперативной памяти, первый регистр 2 числа, регистр 3 ключей защиты, первую, вторую и третью группы 4, 5, 6 элементов 7 контроля .информации,второй регистр 8 числа, блок 9 управления. Кроме того, на чертеже обозначены информационный выход устройства 10, управляющий выход устройства 11 и информационный вход устройства 12.

Работает устройство следующим образом.

Перед началом обработки программ по сигналам от блока управления 9 ключи страниц поступают через первую группу элементов И 4 на счетные входы триггеров первого регистра числа 2, где поразрядно складываются с содержимым этого регистра и записываются в блок оперативной памяти по.сигналу из блока управления 9,, поступающему на второй вход третьей группы элементов И 6. Причем одинаковый ключ страницы поступает на те ячейки памяти, которые отводятся для пользования одно программой. Перед поразрядным сложением кода числа и кода ключа страницы производится формирование значения контрольных разрядов. Следовательно, перед началом обработки программ в ячейках блока оперативной памяти 1 хранятся коды, сформированные путем поразрядного сложения кодов чисел и кодов ключей.

Перед началом обработки некоторой программы ее ключ заносится на регист ключей защиты 3. Предположим, что требуется счвтать некоторое число из блока оперативной памяти 1. нящийся в блоке 1, считывается и поступает на первый и второй регистры чисел 2 и 8. Для проверки- правильности обращения к отведенной для работающей программы зоне памяти по сигналу из блока управления 9, поступающему на второй вход первой группы элементов И 4, ключ защиты памяти поступит на счетные входы триггеров первого регЬстра числа 2, в результате чего произойдет поразрядное сложение считанного кода и кода ключа зашиты памяти.

В этом случае, если код ключа защиты памяти совпадает с кодом ключа страницы, который ранее был поразрядно сложен с кодом числа, то произойдет восстановление значения кода числа и блок контроля информации 7 не выработает сигнала ошибки, а блок управления 9 выработает сигнал, разрешающий передачу считанного кода числа через вторую группу элементов И 5 на информационный выход устройства 10. Одновременно произойдет регенерация числа. Для регенерации числа используется код, хранящийся во втором регистре числа 8. Если же код ключа защиты памяти не совпадает с кодом ключа страницы, то восстановления кода числа не произойдет и блок контроля 7 выработает сигнал ошибки, по которому из блока управления 9 поступит сигнал программного прерывания на управляющий выход устройства 11. Восстановление содержимого считанной ячейки осуществится за счет регенерации кода, хранящегося во втором регистре числа 8.

При записи числа в блок оперативной памяти- 1 перед поступлением кода числа на третий вход первого регистра числа по информационному входу устройства 12 осуществляется считывание числа из той ячейки дамяти, в которую требуется записать число.

Дальнейшая работа по проверке правильности обращения к памяти осуществляется аналогично работе при считывании. Исключение составляет лишь то, что отсутствует регенерация, а осуществляется запись кода совместно с контрольными разрядами из первого регистра числа 2 через группу элементов И 6 в .блок оперативной памяти 1. Записываемое число по информационному входу устройства 12 поступает на первый регистр числа 2. Ни первом регистре числа 2 осуществляется формирование контрольных разрядов, а затем поразрядное сложение кода ключа зашиты памяти, который соответствует коду ключа страницы, с кодом числа.

В случае нарушения обращения к накопителю при записи числа, запись числа из первого регистра числа 2 в блок оперативной памяти 1 не проводится, а осуществляется регенерация ранее считанного кода из второго регистра числа 8 в блок оперативной памяти 1. Таким образом, устройство позволяет организовать защиту не только строго фиксированных по размерности страниц памяти, но и страниц памяти с переменными границами, что обеспечивает большую гибкость защиты памяти и ее быстродействие. Формула изобретения Устройство для защиты памяти, содержащее блок оперативной памяти, первый регистр числа, первую, вторую и третью группы элементов И, регистр клю чей защиты, вход которого является входом устройства по ключам защиты, а выход соединен с первыми входами элементов И первой группы, первый выход блока оперативной памяти соединен с первым входом первого регистра числа, первый выход которого соединен с первыми входами элементов И второй груп пы, а второй выход - с первыми входами элементов И третьей труппы, выход которой соединен с первым входом блока оперативной памяти, о т л и ч а ющ е е с я тем, что, с целью повышения гибкости защиты памяти и быстродействия устройства, оно содержит блок контроля информации, блок управления, второй регистр числа, вход которого соединен с первым выходом блока оперативной памяти, а выход - со вторым входом блока оперативной памяти, вход блока контроля информации соединен с третьим выходом первого регистра числа, а выход - с первым входом блока управления, первый второй и третий выходы которого соединены со вторыми входами элементов И второй группы, второй выход блока управления соединен со вторыми входами элементов И третьей группы, третий выход блока управления соединен со вторыми входами элементов И первой группы, выход которых соединен со вторым входом первого регистра числа, выходы элементов И второй группы являются информационным выходом устройства, третий вход первого регистра числа является информационным входом устройства, четвертый выход блока управления является управляющим выходом устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 523457, кл. Q- И С 29/00, 1976. 2.Процессор ЭВМ ЕС-1020. Под редакцией А. М. Ларионова Статисти. 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты памяти | 1987 |

|

SU1513458A1 |

| Устройство адресации оперативной памяти | 1986 |

|

SU1417004A1 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 2001 |

|

RU2199774C1 |

Авторы

Даты

1979-01-25—Публикация

1976-11-15—Подача