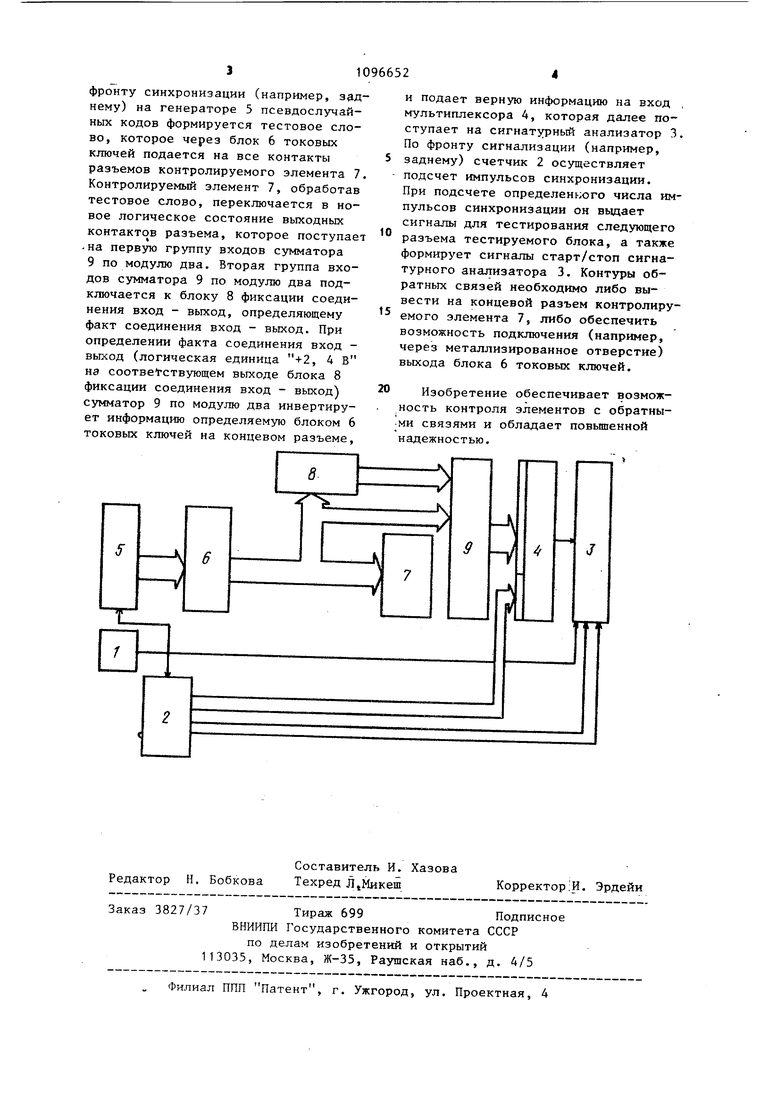

Изобретение относится к вычислительной технике и автоматике и може быть использовано цля контроля интегральных микросхем, а также для поиска неисправных микросхем, обрыВОВ и замыканий на печатных платах Известно устройство для контроля логических блоков, содержащее блок управления, генератор псевдослучайных кодов, накапливающий сумматор, элементы И и блок свертки. Выходы генератора псевдослучайных кодов и выходы контролируемого элемента сое динены с соответст зующими входами элементов И, выходы элементов И сое диваны с входами блока свертки, вых ды которого соединены с входами нак ливающегося сумматора, выход накапливающего сумматора является выходо устройства 1 j . Наиболее близким к изобретению является устройство для функциональ но-параметрического контроля логических элементов, с:одержащее тактов генератор, счетчик, мультиплексор и сигнатурный анализатор, причем вы ход тактового генер)атора соединен с входом счетчика и тактовь м входом сигнатурного анализатора, информаци онный вход которого соединен с выхо дом мультиплексора 2j, Однако известные устройства не обеспечивают возможности контроля логических элементов с обратными связями и с двyxнaпpaвлeнны и цепями информации. Целью изобретения является расширение класса контролируемых элементов . Поставленная цель достигается тем5 что устройство для функционал ного контроля цифровых логических элементовS содержащее тактовый генератор, счетчик, мультиплексор и сигнатурный анализатор, причем выход тактового генератора соединен входом счетчика и тактовым входом сигнатурного анализатора, информационный вход которого соединен с вы ходом мультиплексора, содержит генератор псевдослучайных кодов, бло токовых ключей, блок фиксации соединения вход - выход и сут- матор по модулю два причем группа выходов генератора псевдосл;уАчайных кодов через блок токовых ключей соединен с группой входов контролируемого элемента, группа вьпсодов которого соединена с группой входов блока фиксации соединения вход - выход и первой группой входов сумматора по модулю два, вторая группа входов которого соединена с группой выходов блока фиксации соединения вход - выход, а группа выходов соединена с группой информационных входов мультиплексора, группа управляющих входов которого соединена с группой выходов счетчика, первый и второй разрядные выходы которого соединены с входами задания окна измерения сигнатурного анализатора, выход тактового генератора соединен с тактовым входом генератора псевдослучайных кодов. На чертеже изображена структурная схема устройства для функционального контроля цифровых логических элементов. Устройство содержит тактовый генератор 1, выход которого соединен с входом счетчика 2 и с тактовым входом сигнатурного анализатора 3. Информационный выход сигнатурного анализатора 3 соединен с выходом мультиплексора 4, Группа выходов генератора 5 псевдослучайных кодов через блок 6 токовых ключей соединена с группой входов контролируемого {цифрового логического) элемента 7. Группа выходов контролируемого элемента 7 соединена с группой входов блока 8 фиксации соединения вход - выход и первой группой входов сумматора 9 по модулю два. Вторая группа входов сумматора 9 по модулю два соединена с группой выходов блока 8 фиксации соединения вход - выход, а группа вькодов соединена с группой информационных нходов мультиплексора 4. Группа управляющих входов мультиплексора 4 соединена с группой выходов счетчика 2, первый и второй разрядные выходы которого соединены с входами задания окна измерения сигнатурного анализатора 3. Вьрсод тактового генератора 1 соединен с тактовым входом генератора 5 псевдослучайных кодов. Устройство работает следующим образом. При включении питания тактовый генератор 1 начинает вырабатывать сигналы максимальной частоты работы контролируемого элемента 7. По

фронту синхронизации (например, заднему) на генераторе 5 псевдослучайных кодов формируется тестовое слово, которое через блок 6 токовых ключей подается на все контакты разъемов контролируемого элемента 7. Контролируемый элемент 7, обработав тестовое слово, переключается в новое логическое состояние выходных контактов разъема, которое поступает -на первую группу входов сумматора 9 по модулю два. Вторая группа входов сумматора 9 по модулю два подключается к блоку 8 фиксации соединения вход - выход, определяющему факт соединения вход - выход. При определении факта соединения вход выход (логическая единица +2, 4 В нэ соответствующем выходе блока 8 фиксации соединения вход - выход) сумматор 9 по модулю два инвертирует информацию определяемую блоком 6 токовых ключей на концевом разъеме.

и подает верную информацию на вход , мультиплексора 4, которая далее поступает на сигнатурный анализатор 3. По фронту сигнализации (например, заднему) счетчик 2 осуществляет подсчет импульсов синхронизации. При подсчете определенного числа импульсов синхронизации он выдает сигналы для тестирования следующего разъема тестируемого блока, а также формирует сигналы старт/стоп сигнатурного анализатора 3. Контуры обратных связей необходимо либо вывести на концевой разъем контролируемого элемента 7, либо обеспечить возможность подключения (например, через металлизированное отверстие) выхода блока 6 токовых ключей.

Изобретение обеспечивает возможность контроля элементов с обратными связями и обладает повьшенной надежностью.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Устройство для встроенного тестового контроля | 1984 |

|

SU1196877A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1191911A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1254489A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО КОНТРОЛЯ ЦИФРОВЫХ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ, содержащее тактовый генератор, счетчик, мультиплексор и сигнатурный анализатор, причем выход тактового генератора соединен с входом счетчика и тактовым входом сигнаIтурного анализатора, информационный вход которого соединен с выходом мультиплексора, о-тличающеес я тем, что, с целью расширения й-класса контролируемых элементов, оно содержит генератор псевдослучайных кодов, блок токовых ключей, блок фиксации соединения вход - выход и сумматор по модулю два, причем группа выходов генератора псевдослучайных кодов через блок токовых ключей соединена с группой входов контролируемого элемента, группа выходов которого соединена с группой входов блока фиксации соединения вход - выход и первой группой входов сумматора по модулю два, вторая группа входов которого соединена с группой выходов блока фиксации соединения вход - выход, а группа выходов соединена с группой информационных входов: мул 1;р(Л плексора, группа управляющих входов которого соединена с группой выходов счетчика, первый и второй разряд-t ные выходы которого соединены с вхо§ дами задания окна измерения сигнатурного анализатора, выход тактового генератора соединен с тактовым входом генератора псевдослучайных кодов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических блоков | 1976 |

|

SU643877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для функционально-парамет-РичЕСКОгО КОНТРОля лОгичЕСКиХэлЕМЕНТОВ | 1979 |

|

SU830391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-07—Публикация

1981-10-16—Подача