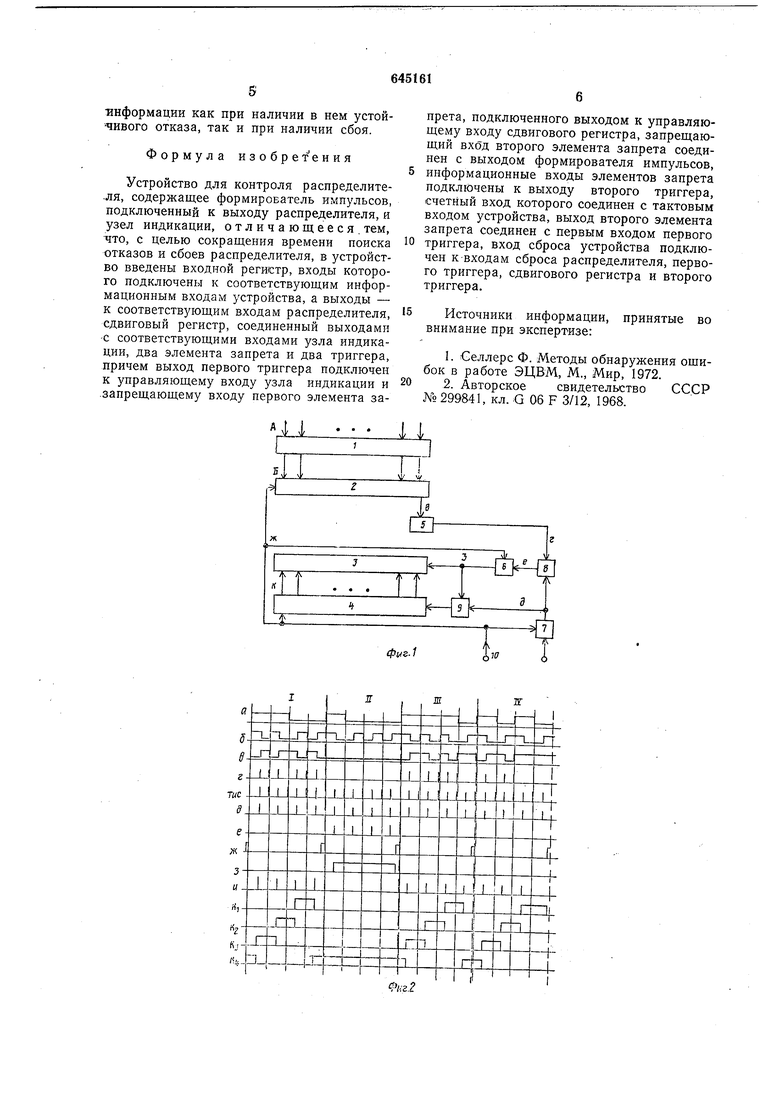

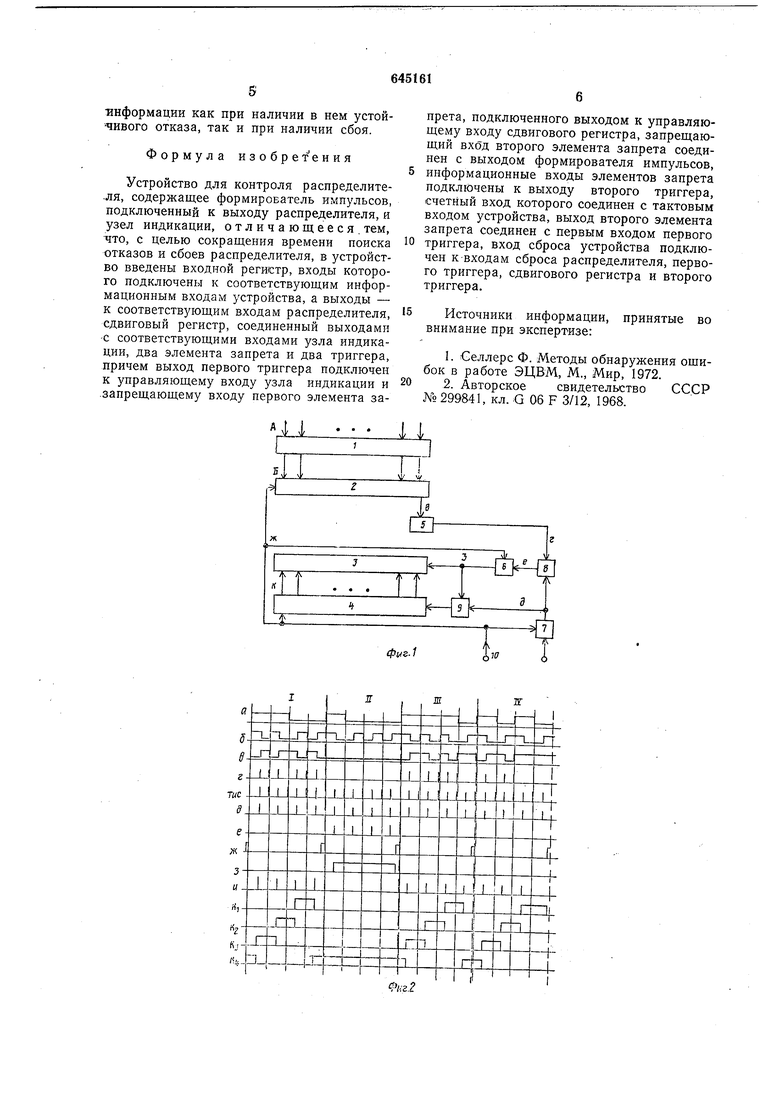

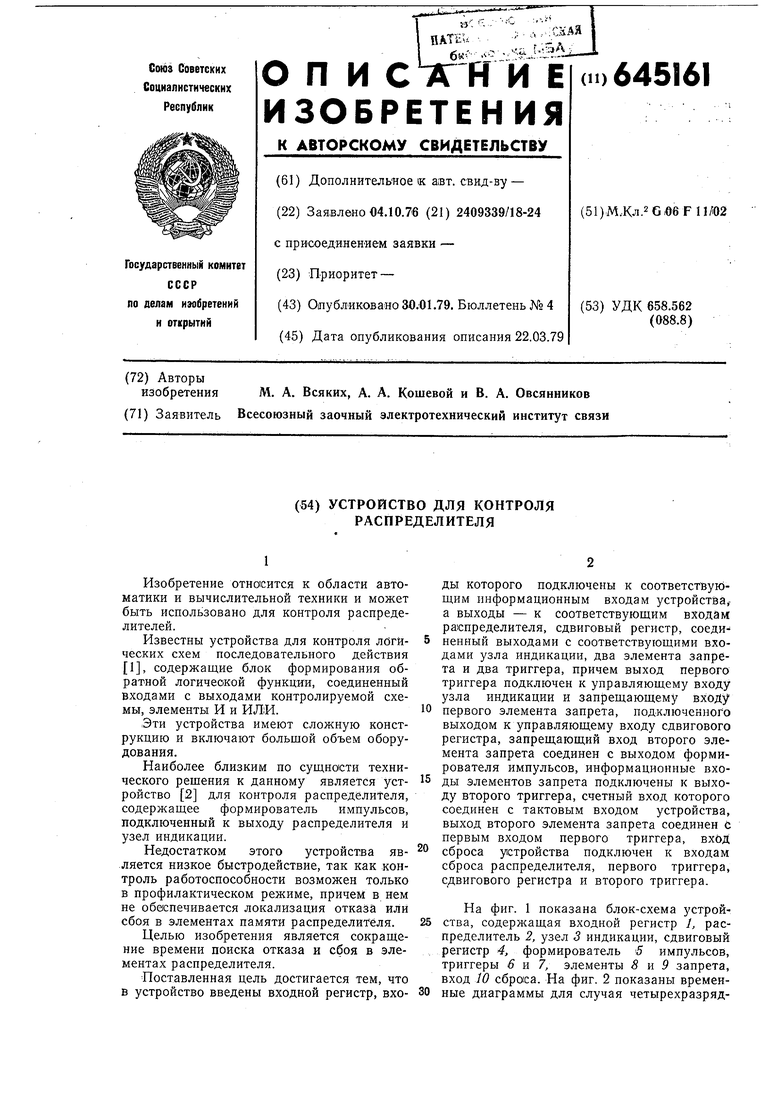

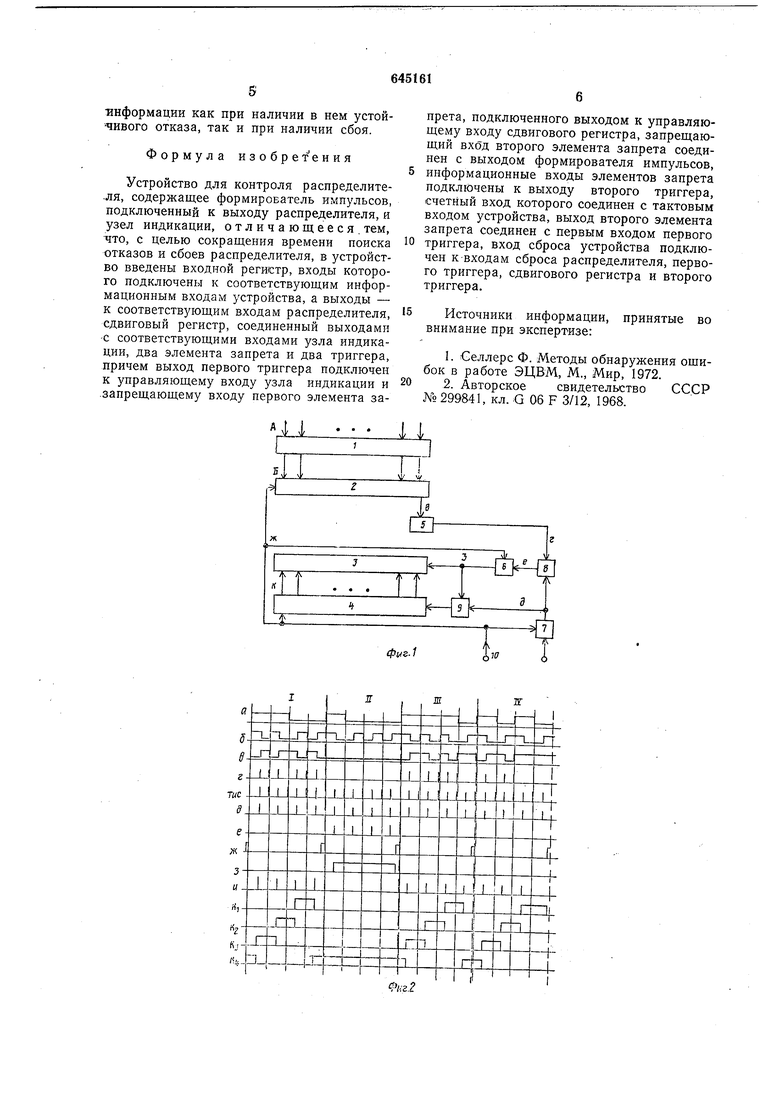

ного распределителя в точках, отображенных на фиг. 1. В основу предлагаемого устройства положено свойство выявления наличия перехода нуля в единицу или единицы в нуль за время длительности входной кодовой при считывании кодовой комбинации с. выхода распределителя 2, на входы которого поступают кодовые комбинации сообщения, предварительно преобразованные на входном регистре / в двухуровневые сигналы. При этом единичные посылки на входах распределителя будут иметь переход единицы в нуль, а нулевые - переход нуля в единицу (см. позидию Б временной диаграммы). Устройство работает следующим образом. Каждый раз перед проведением контроля элементы памяти распределителя 2, сдвигового регистра 4 и триггера 6 устанавливаются в состояние логического нуля при поступлении сигнала на вход ,10 сброса. При этом только в 1-ый разряд сдвигового регистра записывается логическая единица, а остальные разряды устанавливаются в нуль. При отсутствии отказов и сбоев в элементах памяти распределителя (раздел I временной диаграммы) с его выхода на каждом временном интервале, равном длительности входной кодовой посылки, появится двухуровневый сигнал с переходом единицы в нуль или нуля в единицу. На выходе формирователя 5 появляются импульсы, определяющие наличие перехода нуля в единицу или единицы в нуль при считывании с элементов памяти каждого, разряда распределителя 2 (позиция Г временной диаграммы). При этом импульсы с формирователя 5 будут запрещающими для элемента 8. Следовательно, тактовые импульсы с выхода триггера 7 не поступят на вход триггера 6, который будет находиться в исходном состоянии (состоянии логического нуля) в течение всего времен и считывания кодовой комбинации, что означает отсутствие ошибки в каждом цикле считывания (см. позиции Г, Д, Е, 3 временной диаграммы). В состоянии логического нуля сигнал с ыхода триггера 6 является разрешающикг для элемента 9 запрета. Поэтому тактовые импульсы, поступая с выхода счетного триггера 7 через элемент 6 на вход регистра 4 сдвига, будут переписывать логическую единицу, записанную при начальной установке в его 1-й разряд, в последующие разрйды.при каждом цикле считывания кодовой комбинации с распределителя 2. В блоке 3 индикации при отсутствии отказов и сбоев в элементах памяти распределителя 2 будет наблюдаться мерцание элементов индикации, так как с выходов сдвигового регистра 4, в каждом цикле считывания поступает импульс, длительность которого равна длительности входной кодовой посылки распределителя 2 (позиции И, Ki, KZ, Кг, Kt временной диаграммы). При появлении сбоя элементов памяти, например в 4-м разряде распределителя (раздел II временной диаграммы), уже в 1-м цикле считывания кодовой комбинации, поступившей на входы распределителя, будет отсутствовать двухуровневый сигнал на его выходе (позиция В временной диаграммы). В этом случае с выхода формирователя 5 не будут выдаваться запрещающие импульсы и тактовые импульсы с выхода триггера 7 через элемеит 8 запрета поступят на вход триггера 6, и первый же импульс перебросит его в со стояние логической единицы (позиции В, Г, Д, Е, 3 временной диаграммы). Так к:ак сигнал логической единицы с выхода триггера 6 является сигналом «ошибка, а также запрещающим сигналом для элемента 6, то тактовые импульсы с выхода триггера 7 через элемент 6 не поступят на вход сдвигового регистра 4 и логическая единица, записанная в 1-м его разряде, не будет переписываться в последующие разряды сдвигового регистра 9 (позиции И, К4 временной диаграммы). Поэтому в блоке 3 индикации будут индицированы элемент «отказ и элемент «отказ 4 разряда. При повторном проведении контроля распределителя 2 индикация элемента «отказ 4 разряда наблюдаться не будет (раздел III временной диаграммы), поскольку ранее имел место сбой. При наличии устойчивого отказа, например в 1-м разряде распределителя 2, будет-иметь место локализация неисправности в 1-м разряде, как в текущем диагностическом процессе, так и в последующем (разделы III и IV временной диаграммы). В этом случае устройство работает аиалогичио описанному выше. В результате на выходе распределителя двухуровневый сиг-, нал будет отсутствовать в 4-м цикле считывания и на выходе элемента 8 в этом цикле появится тактовый импульс, поступивший с выхода триггера 7 (позиции В, Г, Е, 3 вре-. менной диаграммы), который перебрасывает триггер 6 в состояние логической единицы. Поступление тактовых импульсов на вход сдвигового регистра 4 через элемент 6 прекращается и продвижение в нем логической единицы завершается на 4-м разряде. В блоке 3 постоянно индицируются элемент «отказ и элемент «отказ 1 разряда. Повторение диагностического процесса, как следует из раздела IV временной диаграммы, дает также локализацию отказа в 1-м разряде передающего распределителя 2. Следовательно, в данном разряде распределителя 2 имеет место устойчивый отказ. Таким образом, устройство обеспечивает локализацию неисправностей элементов памяти распределителя в режиме обработки

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1978 |

|

SU773735A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

| Устройство для контроля распределителя | 1980 |

|

SU942026A1 |

| УСТРОЙСТВО СИГНАЛИЗАЦИИ | 2007 |

|

RU2335030C1 |

Авторы

Даты

1979-01-30—Публикация

1976-10-04—Подача