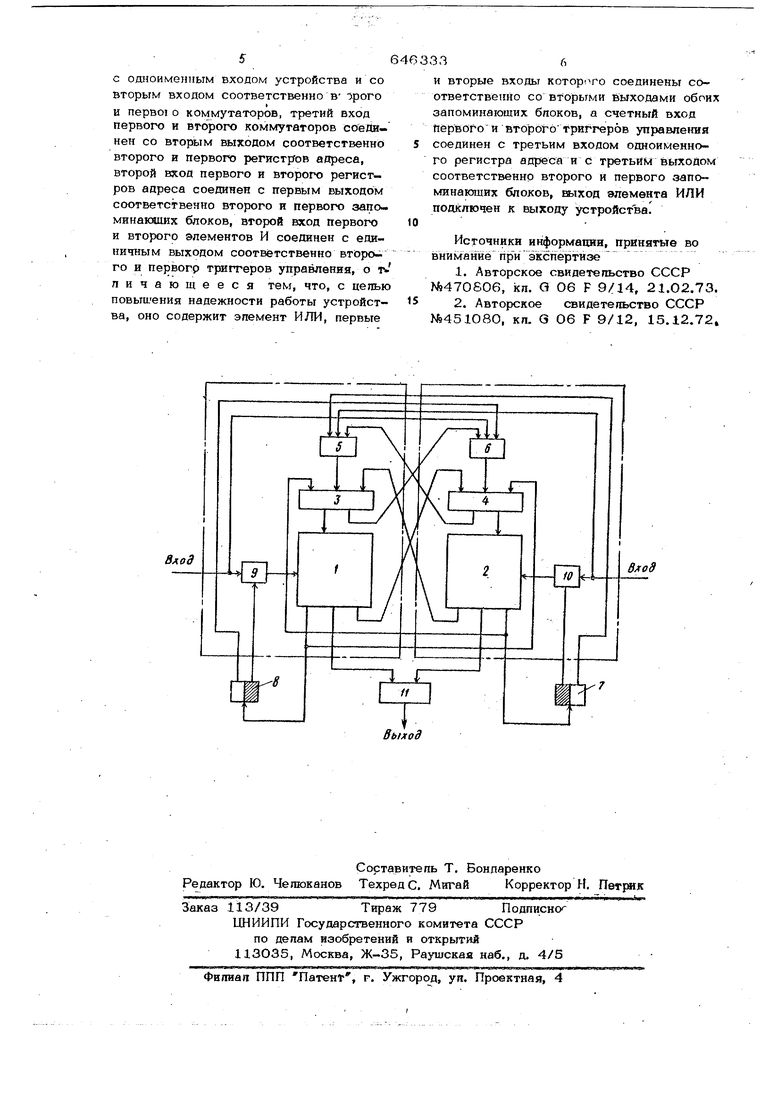

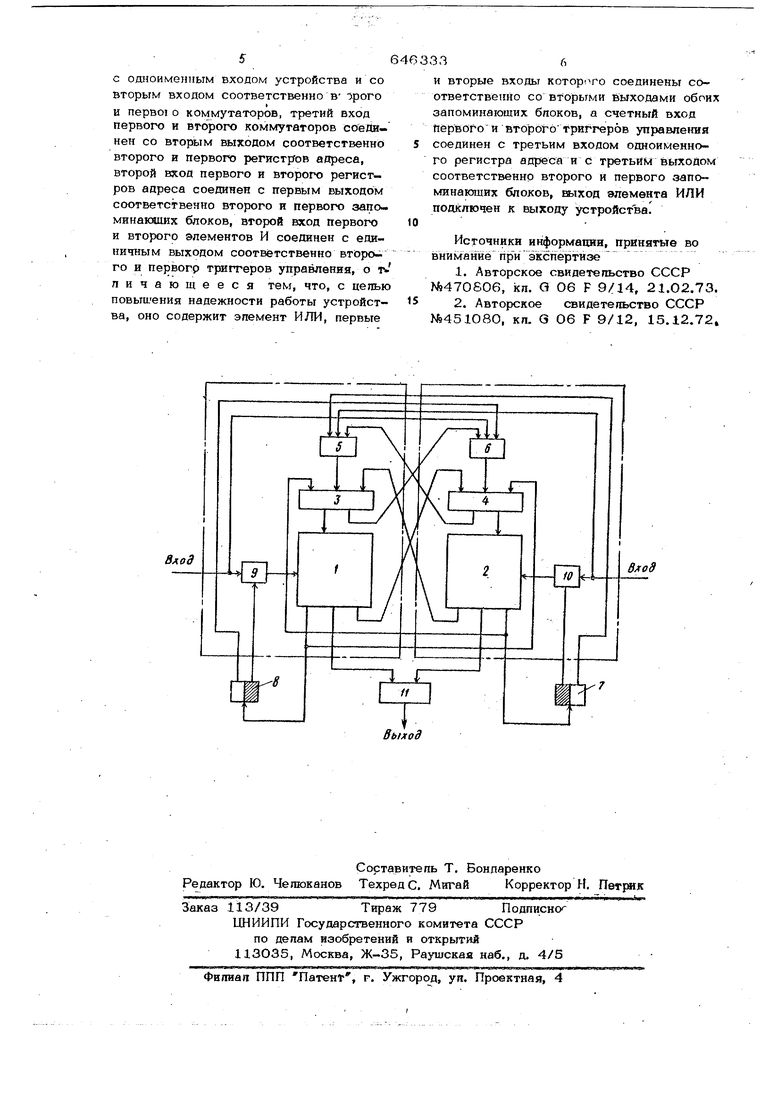

(54) ПЕРЕСТРАИВАЕМОЕ МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ ,,,,,.,„,; з / . .;-; адреса, второй &х6д первого и второго регистра адреса соединен с пЪрвым выходом соответственно второго и Первого запоминающего блока, второй вход первого и второго элемента И соединен с ejQHHH4HbiM выходом соответственно второго и первого триггера управпения. Недостаток известного устройства аакшочается в том, что в случае отказа одного из запоминающих блоков нет воз можности перестройки на работу другого запоминающего блока, что снижает в целом функциональную надежность всего устройства. , Цегпью Изобретения является повышение надежности работы устройства. Для этого в устройство введен элемент ИЛИ, первые и вторые входы кото рого соединены соответственно со вторыми выходами обоих запоминающих блоков, а счетный вход первого и второ го триггера управления соединен с третьим входом одноименного регистра адреса и с третьим выходом соответственно второго и первого запоминающего блока, выход элементу ИЛИ подключен вьтходу устройства. На чертеже представлена функционал ная схема предлагаемого устройства. Устройство содержит первый запоминающий блок 1, второй запоминающий блок 2, первый регистр адреса 3, второй регистр адреса 4, первый коммутатор 5, второй коммутатор 6, первый триггер управления 7, второй триггер управления 8, первый элемент И 9, второй элемент И 10, элемент ИЛИ И Устройство работает следукнцим образом. Пусть в исходном состоянии п эрвый триггер управления 7 и второй триггер 8 управления находятся в единичном состоянии и пусть на регистре 3 (4) адреса находится адрес микрокоманды подлежащей считыванию. Так как триг геры 7, 8 находятся в единичном состоянии, то они разрешают прохождение поступившего на вход тактового импуль са через элемент И 9 (10) н блокирую коммутаторы 5, 6. На третьем ыходе запоминающего блока 1 (2) появляется считанная микрокоманда, а адрес следующей микрокоманды заводится на регистр 4 (3) azqjeca другого блока. На выходе устройства микрооперации с пер вого и втсрЬго блоков появляются поочередно. При отказе одного из запомизнающих блоков, например 1, происходит перестройка на работу другого запоминающего блока 2, а именно: со второго выхода отказавшего запоминающего блока 1 подается на третий вход регистра, 4 адреса работающего блока сигнал, устанавливающий на этом регистре фиксированный адрес. С того же выхода запоминающего блока 1 подаетс5, сигнал на счетный вход триггера 8, который устанавливает его в нулевое состояние. Адрес следующей микрокоманды, считанный с выхода запоминающего работающего блока 2, поступает на вход регистра 3 адреса отказавшего блока. Далее этот адрес через разблокированный коммутатор 6 работающего блока поступает на регистр 4 адреса этого блока. По данному адресу запоминающий блок 2 выдает микрооперацию на элемент ИЛИ Ни далее на выход устройства, а адрес следующей микрокоманды заводится на регистр 3 адреса отказавщего блока. Таки.м образом, повьппение функциональной надежности устройства достигается тем, что в случае- отказа одного из запоминающих блоков, другой запоминающий блок перестраиваемого микропрограммного устройства продолжает работать и по фиксированному арресу устройство переходит на программу обработки отказа либо на подпрограмму рещения данной задачи по усеченному алгоритму. Устройство же прототип в случае отказа одного из запоминающих устройств прекращает выдачу информации. Формула изобретения Перестраиваемое микропрограммное устройство управления, содержащее даа запоминающих блока, два регистра адреса, два элемента И, два коммутатора и два триггера управления, причем первый вход первого и второго коммутаторов соединен с нулевым выходом соот ветственно первого я второго триггеров управления, выход первого и второго коммутаторов соединен с входом соответственно первого и второго регистров адреса, nepiM)ifl выход первого и второго регистров адреса соединен с первым входом одноименного запоминающего блока, второй вход каждого запоминающего блока соединен с ныходом однонменного элемента И, первый вход первогч н второго елемеатов И соединен с одноименным входом устройства и со вторым входом соответственно В iporo и перво о коммутаторов, третий вход первого и второго коммутаторов соёдинеи со вторым выходом соответственно второго и первого регистргов адреса, второй вход первого и второго регистров адреса соединен с первым выходом соответственно второго и первого запоминакших блоков, второй вход первого и второго элементов И соединен с единичным выходом соответственно второго и первогр триггеров управления, о т пинающееся тем, что, с цепью повышения надежности работы устройства, оно содержит эпемент ИЛИ, первые 36 и вторые входы котор го соединены соответственно со вторыми выходами обоих запоминающих блоков, а счетный вход первого И второго триггеров управления соединен с третьим входом одноименного регистра адреса и с третьим выходом соответственно второго и первого запоминающих блоков, выход элемента ИЛИ подключен к выходу устройства. Источники информация, принятые во внимание при экспертизе 1.Авторское свидететЕЬство СССР N9470806, кп. Q 06 F 9/14, 21.02.73. 2.Авторское свидетельство СССР №451080, кп. 6 06 F 9/12, 15.12.72

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1980 |

|

SU938283A1 |

| Перестраиваемое микропрограммноеуСТРОйСТВО упРАВлЕНия | 1979 |

|

SU830383A1 |

| Реконфигурируемое устройство с программным управлением | 1981 |

|

SU1007108A1 |

| Микропрограммное устройство управления | 1980 |

|

SU888120A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

Авторы

Даты

1979-02-05—Публикация

1976-10-11—Подача